具体参考Xilinx文档,pg121-c-counter-binary Version12.0。

一、Binary Counter有什么用?

Binary Counter是Vivado中的IP核,即二进制计数器。

二进制计数器可用于创建加法计数器、减法计数器和加 /减计数器,输出宽度可达 256位。

计数上限和增量值都是用户可编程的。当计数器到达上限时,下一个计数为零。除此之外,也可选用户可编程阈值输出。

二、Binary Counter怎么用?

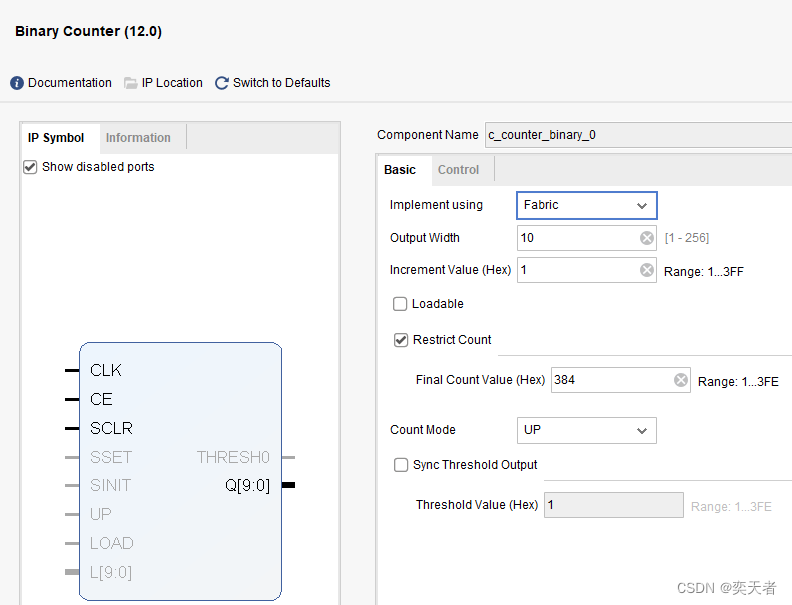

基本参数设置

重要参数

Implement using:可以设置计数器的实现类型为Fabric(FPGA互联矩阵和嵌入其中的CLBs)或DSP Slice(DSP48E2原语定义)。

Output Width:指定计数器的位宽。

Increment Value:指定计数器的十六进制表示的增量值。当Restrict Count为false时,有效范围为1到

2

O

u

t

p

u

t

W

i

d

t

h

−

1

2^{Output Width}-1

2OutputWidth−1;当 Restrict Count为true时,增量值的有效设置由公式控制 :

对于向上计数器,有 :

最终计数值(Final Count Value) / 增量值(Increment Value) = 整数

对于向下计数器,有:

(

2

O

u

t

p

u

t

W

i

d

t

h

2^{Output Width}

2OutputWidth - 最终计数值(Final Count Value)) / 增量值(Increment Value)=整数

Restrict Count:当Restrict Count为true时,计数器只向上 (或向下 )计数到最终计数值参数中指定的值。

当Restrict Count为false时,计数器计数到可以使用指定的输出位宽表示的最大值。此选项与向

上 /向下计数器选项和同步设置控制是互斥的。

Final Count Value:当选用Restrict Count时,该参数可指定计数器的上限,以十六进制表示。

Count Mode:此参数可指定计数器是向上计数UP,向下计数DOWN,还是在UP引脚上指定其方向 (向上 /向下 )(UPDOWN)。

其他参数

Loadable:Loadable = true时,允许输入端口 L[N:0]上 的值通过逻辑并加载到下一个有效时钟边沿的输出寄存器中。

Sync Threshold:当此参数等于 true时, THRESH0 生成组合输出。

Threshold Value:指定该值 THRESH0 作为十六进制值被激活的值。

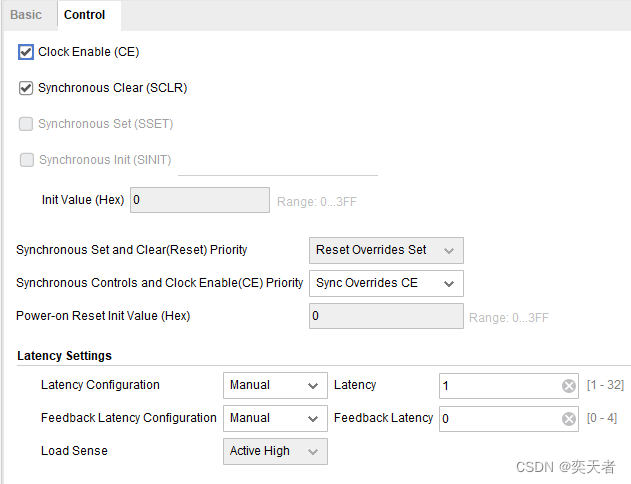

控制参数设置

重要参数

CE:指定是否包含时钟使能引脚。

SCLR:指定是否包含复位清零引脚。

Power-on Reset Init Value:指定上电复位时输出的初始值,以十六进制表示,与SCLR端口相斥。

其他参数

Init Value:以十六进制形式指定断言时 SINIT 输出初始化的值。如果 SINIT为 false,则忽略初始值。

SSET:指定是否包含SSET引脚。 SSET引脚在DSP Slice实现中无效。

SINIT:指定是否包含SINIT 引脚,当断言时,同步设置输出值为初始值定义的值。

注意: 如果SINIT存在,则既SCLR SSET不存在,也不存在。SINIT引脚在DSP Slice实现中无效。

Synchronous Set and Clear(Reset) Priority:该参数控制 fabric:SSET and SINIT,输入是否 SCLR, 合格 CE,

当设置为 Sync_Overrides_CE时,同步控制将覆盖 CE 信号;当设置为 CE_Overrides_Sync时,SCLR 仅当 CE 为高时有效。

注意:在结构原语上, SCLR and SSET 控件会覆盖 CE, ,因此选择 CE_Overrides_Sync通常会导致额外的逻辑。

Synchronous Controls and Clock Enable(CE) Priority:控制相对优先 SCLR 级and SSET。

当设置为 Reset_Overrides_Set时,SCLR 覆盖 SSET,默认值是Reset_Overrides_Set。因为这是原语排列的方式,设定 SSET 优先级需要额外的逻辑。

Latency Settings

Latency Configuration:自动或手动 ;自动设置最大速度的最佳延迟 ;手动允许用户将延迟设置为允许的值之一。

Latency:当 “延迟配置 ”为 “手动 ”时,用于设置时延。

Feedback Latency Configuration:自动或手动 ;自动设置最佳反馈延迟以达到最高速度 ;手动允许用户将反馈延迟设置为允许的值之一。

Feedback Latency:当 “反馈延迟配置 ”为 “手动 ”时,用于设置延迟。

端口说明

| 信号 | 输入/输出 | 端口描述 |

|---|---|---|

| CLK | I | 上升沿时钟信号 |

| UP | I | 控制加/减计数器的计数方向,高电平时向上计数,低电平时向下计数 |

| CE | I | 高电平时钟使能 |

| SCLR | I | 同步清除,高电平时,输出强制为低电平 |

| THRESH0 | O | 用户可编程阈值信号 |

| Q[N:0] | O | 计数器输出 |

| L[N:0] | I | 输入装载数据 |

| LOAD | I | 负载控制信号 |

| SSET | I | 同步设置,高电平时,输出强制为高电平 |

| SINIT | I | 同步初始化,高电平时,输出强制为用户设置的状态 |

实例化代码

reg i_clk; // 时钟信号

reg cen; // 高电平时,时钟启用

wire rst; // 高电平时,输出清零

wire [9:0] q; // 计数器输出

assign rst = ~i_rst_n;

c_counter_binary_0 rcount_1(

.CLK(i_clk),

.CE(cen),

.SCLR(rst),

.Q(q_1)

);

1145

1145

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?