具体参考Xilinx文档,pg063-dist-mem-gen Version8.0。

一、Distributed Memory Generator有什么用?

Distributed Memory Generator是Vivado中的IP核,即分布式存储器。

它可以生成只读存储器 (ROM),单端口、简单双端口和双端口随机存取存储器 (RAM),

且生成的存储器支持16-65536字的数据深度,和1-1024位的数据宽度。

二、Distributed Memory Generator怎么用?

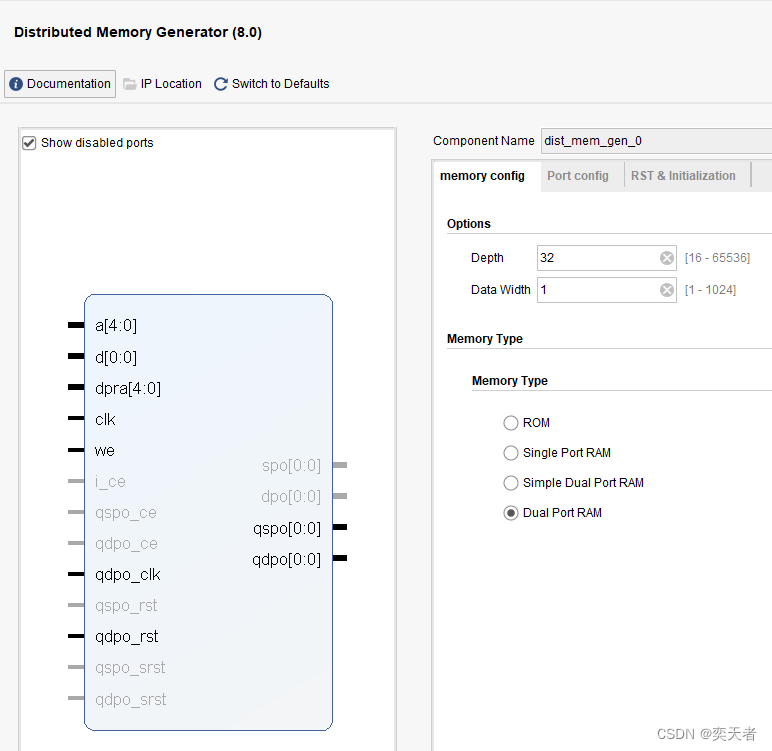

存储器配置

Depth:深度。以16为步长,输入有效范围为16-65536的值,默认值为64。

Data Width:数据宽度。输入内存的宽度,取值范围为1-1024,默认值为16。

Memory Type:内存类型。选择四个选项之一,分别为ROM,Single Port RAM(单端口RAM),Simple Single Dual RAM(简单双端口RAM), Dual Port RAM(双端口RAM),默认设置为单端口RAM。

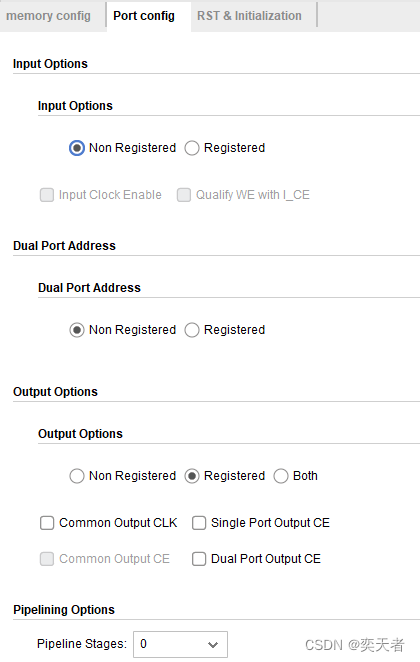

端口配置

重要参数

Input Options:输入选项。选择所需的输入类型的选项。

选择Registered,会根据所选的内存类型产生不同的效果。对于单端口RAM、简单双端口和双端口,生成a [N:0] 地址输入上的寄存器、数据输入寄存器和WE寄存器。

Input Clock Enable:输入时钟使能。当输入选项设置为Registered且存储器类型是RAM时,可选输入可用。

Qualify WE with I_CE:仅对单端口RAM、简单双端口RAM和双端口RAM,输入选项设置为Registered并选择输入时钟启用。当选择时,WE寄存器具有由I_CE输入驱动的时钟使能。

Dual Port Address:简单双端口/双端口地址。仅对简单的双端口RAM和双端口RAM有效,并控制DPRA[N:0] 输入上是否存在寄存器。

Output options:输出选项。选择所需的输出类型的选项。

Common Output CLK:公共输出CLK。仅对Registered的简单双端口RAM启用。

Common Output CE:共同输出CE。仅对Non Registered的简单双端口RAM启用。

Single Port Output CE:单端口输出时钟使能。仅对输出Registered的存储器或输入Registered的ROM启用,以提供此可选引脚。

Dual Port Output CE:双/简单双端口输出时钟使能。仅对输出Registered的简单双端口RAM和双端口RAM启用,以提供此可选引脚。

其他参数

Pipelining Options:流水线选项选择。当选择Registered的单端口RAM,简单的双端口RAM和双端口RAM时,可以将可选的流水线寄存器放置到输出路径中。

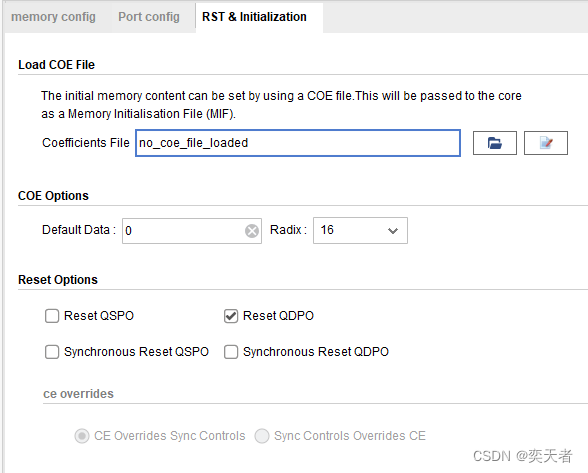

复位与初始化

重要参数

Load Coe File:加载COE文件。可以使用COE file设置存储元件的初始值。要加载COE file,单击文件夹图标浏览。要查看初始内容,单击编辑图标显示。

COE Options:COE选项。输入要存储在COE文件中未初始化的内存位置中的初始值。

Default Data:默认数据。 不输入值时,默认为0。可以按基数定义的二进制、十进制或十六进制格式确定默认数据输入值。该值应等于选定的数据宽度。

Radix:基数。 选择默认数据值的基数。可选项为2、10和16。

Reset Options:重置选项。

Reset QSPO:重置QSPO。如果选中,则可以使用异步单端口输出复位引脚。

Reset QDPO:重置QDPO。如果选择,异步简单双端口和双端口输出复位引脚是可用的。

Synchronous Reset QSPO:同步复位QSPO。如果选中,则可使用同步单端口输出复位引脚。

Synchronous Reset QDPO:同步复位QDPO。如果选中,则可使用同步简单双端口和双端口输出复位引脚。

其他参数

ce overrides:ce覆盖

CE Overrides Sync Controls:CE覆盖同步控制。仅当选择了同步复位选项之一且选择了相应的输出时钟使能时才启用。当选择时,同步控制信号由时钟使能引脚限定。

Sync Controls Overrides CE:同步控制覆盖CE。仅当选择了同步复位选项之一且选择了相应的输出时钟启用时,同步控制才会覆盖CE启用。当被选择时,同步控制信号的操作与输出时钟使能信号的状态无关。

端口说明

以(Dual-Port Distributed RAM)双端口分布式RAM为例。

| 信号 | 输入/输出 | 端口描述 |

|---|---|---|

| d[p:0] | I | 要写入双端口RAM存储器的数据输入 |

| a[n:0] | I | 地址输入。只有ROM和单端口RAM的地址输入。 |

| dpra[n:0] | I | 双端口读地址。 |

| spo[n:0] | O | 非注册的单端口输出总线 |

| qspo[n:0] | O | 注册的单端口输出总线 |

| dpo[n:0] | O | 非注册的双/简单双端口输出总线 |

| qdpo[n:0] | O | 注册的双/简单双端口输出总线 |

| clk | I | ROM和单端口RAM的写入时钟和寄存器时钟 |

| qdpo_clk | I | 双端口和简单双端口RAM输入和输出寄存器的时钟和寄存器时钟 |

| we | I | 写入启用 |

| i_ce | I | 输入时钟使能 |

| qspo_ce | I | 在ROM上,时钟使能控制所有输入和输出寄存器。 |

| qdpo_ce | I | 双端口的时钟使能控制 |

| qspo_rst | I | 单端口注册的输出异步复位 |

| qdpo_rst | I | 双端口注册的输出异步复位 |

| qspo_srst | I | 单端口注册的输出同步复位 |

| qdpo_srst | I | 双端口注册的输出同步复位 |

实例化代码

// 以双端口RAM为例

reg din; // 输入数据

reg [4:0] wa; // 写地址输入

reg wen; // 写使能位

wire rst; // 复位信号,高电平有效

wire [4:0] ra; // 读地址输入

wire dout; // 存储器输出

assign rst = ~i_rst_n;

dist_mem_gen_0 dint_ram(

.a(wa),

.d(din),

.dpra(ra),

.clk(i_clk),

.we(wen),

.qdpo_clk(i_clk),

.qdpo_rst(rst),

.qspo(),

.qdpo(dout)

);

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?