Quartus II提供的LPM_couter IP核的使用

FPGA设计方式:

原理图,Verilog HDL设计方式,IP核输入方式

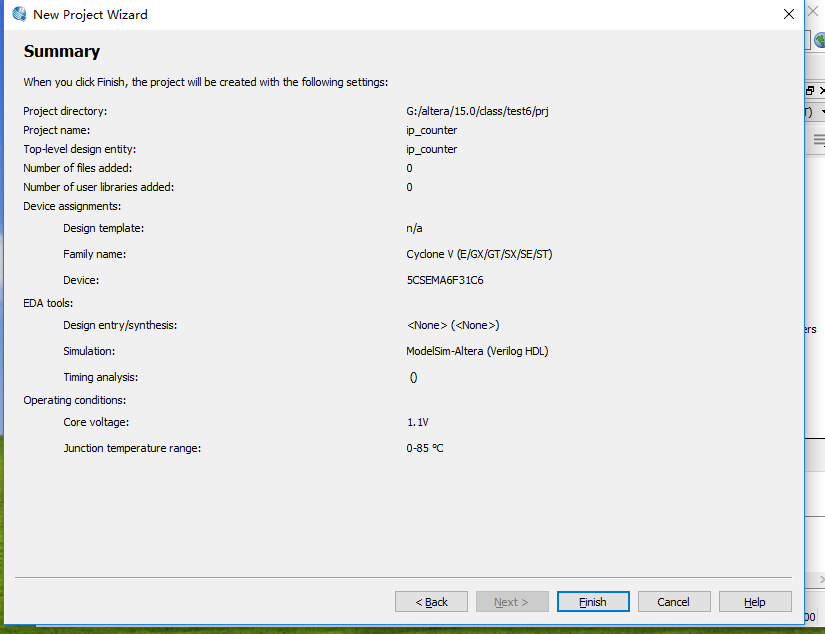

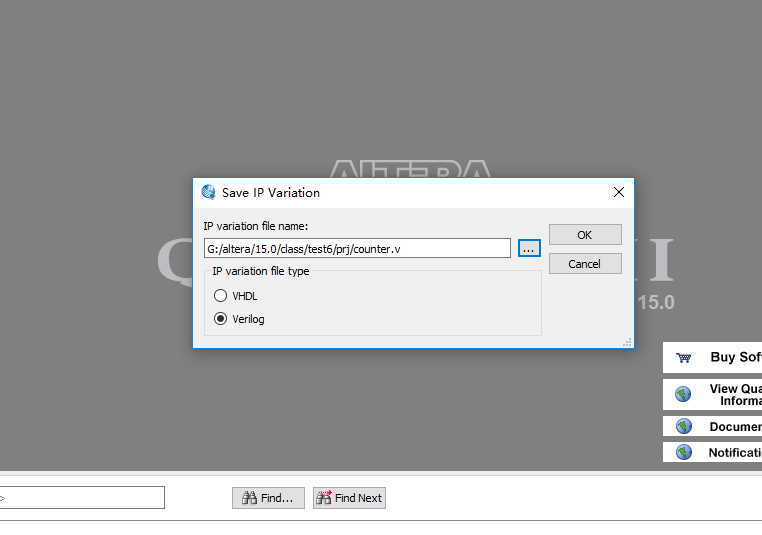

创建IP核

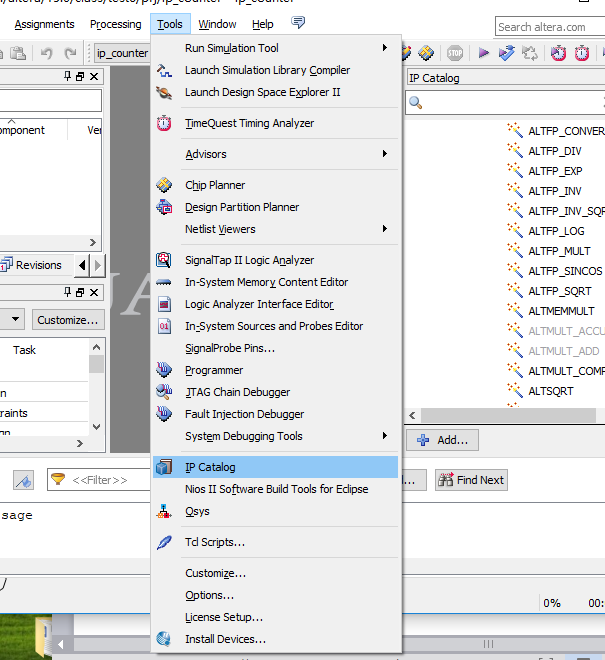

点击TOOLS—IP catalog-libray-Arithmetic-LPM_COUNTER

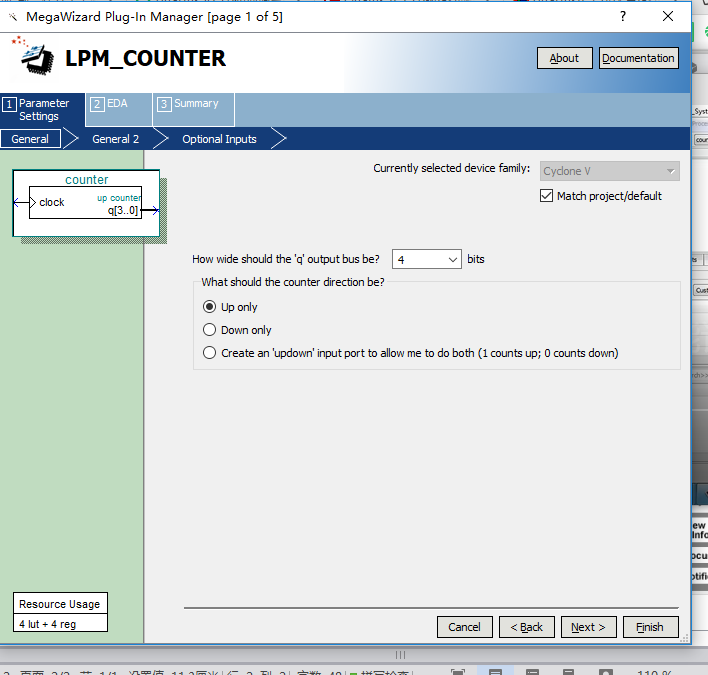

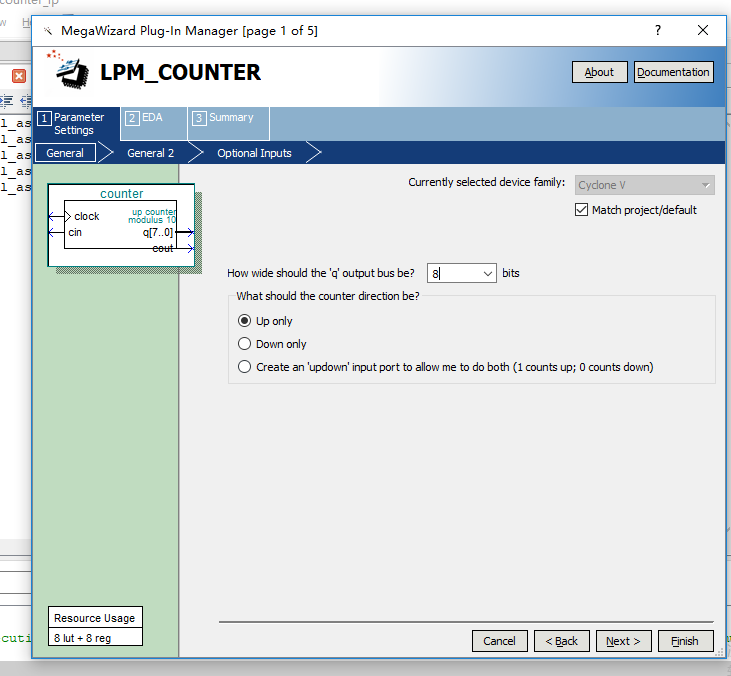

选择希望输出的寄存器是多少位的,计数类型。

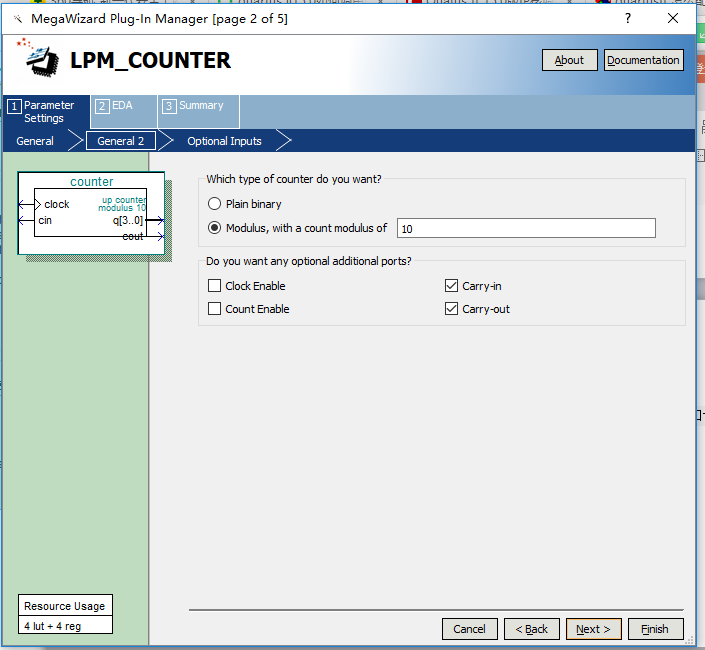

选择计数器类型(直接计数还是以模的形式计数),是否需要时钟使能和计数使能信号、进位链的输入和进位链的输出。

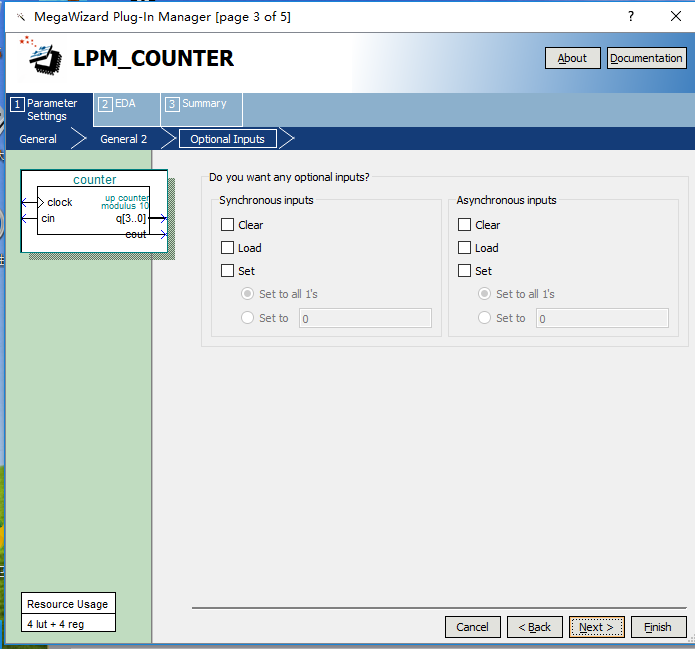

清零加载等信号

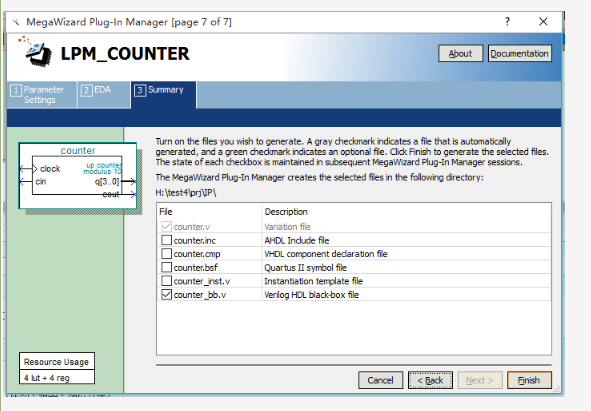

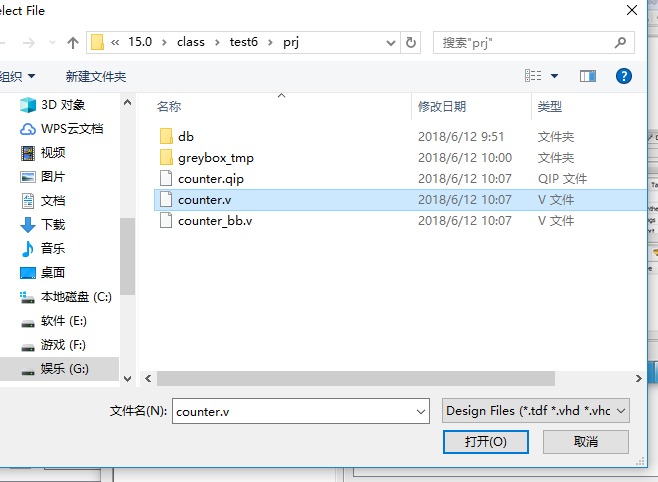

创建成功后的IP核的文件信息

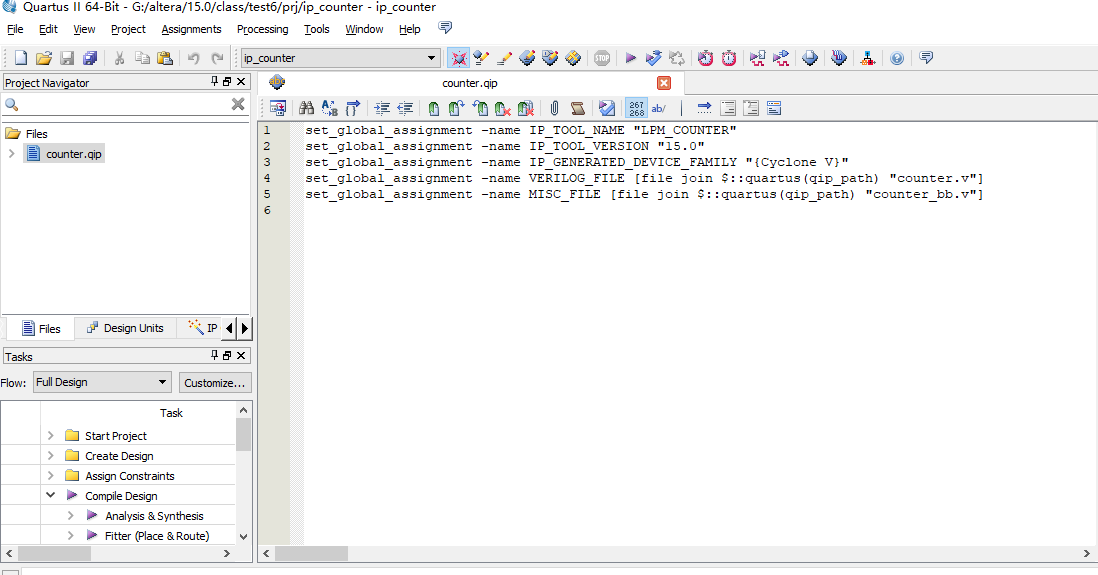

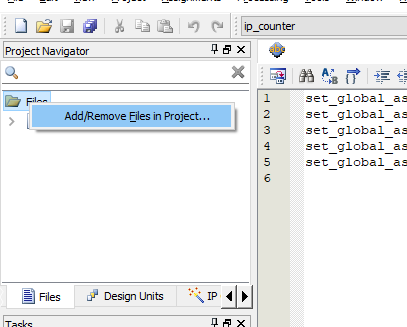

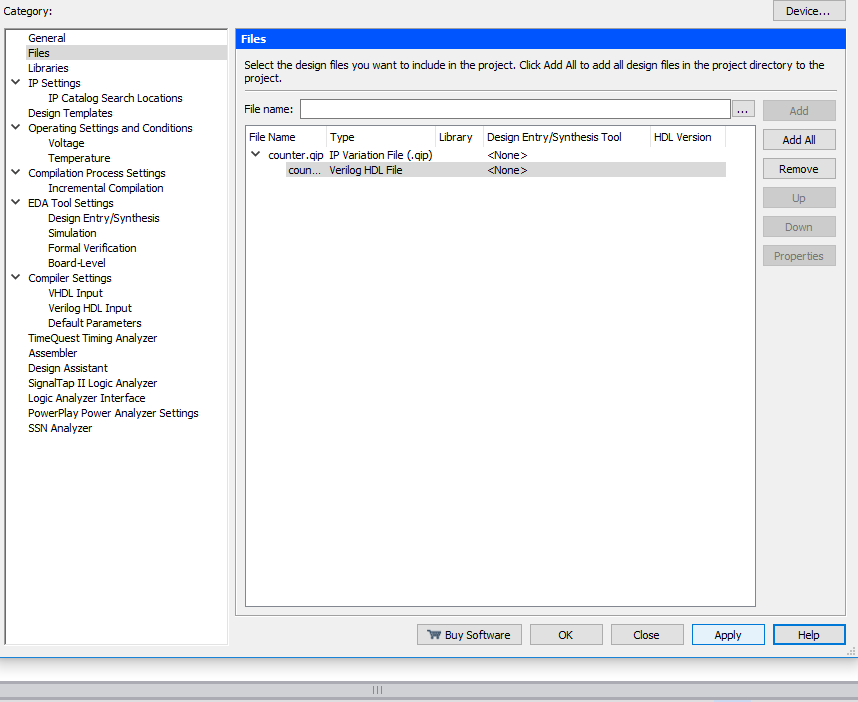

将counter.v文件加载到顶层文件中

Ip核已经做好了功能,直接利用就可以;

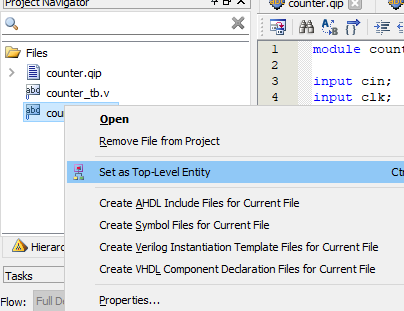

把counter_ip设置为顶层文件后进行编译。

编写testbench文件进行测试IP核功能

`timescale 1ns/1ns `define clock_period 20 module counter_tb; reg cin,clk; // 进位输入 计数基准时钟; wire cout;//进位输出 wire [3:0] q; counter counter0( .cin(cin), .clock(clk), .cout(cout), .q(q) ); initial clk = 1; always #(`clock_period/2)clk = ~clk; initial begin repeat(20)begin cin = 0; #(`clock_period*5)cin = 1; #(`clock_period)cin = 0; end #(`clock_period*200); $stop; end endmodule

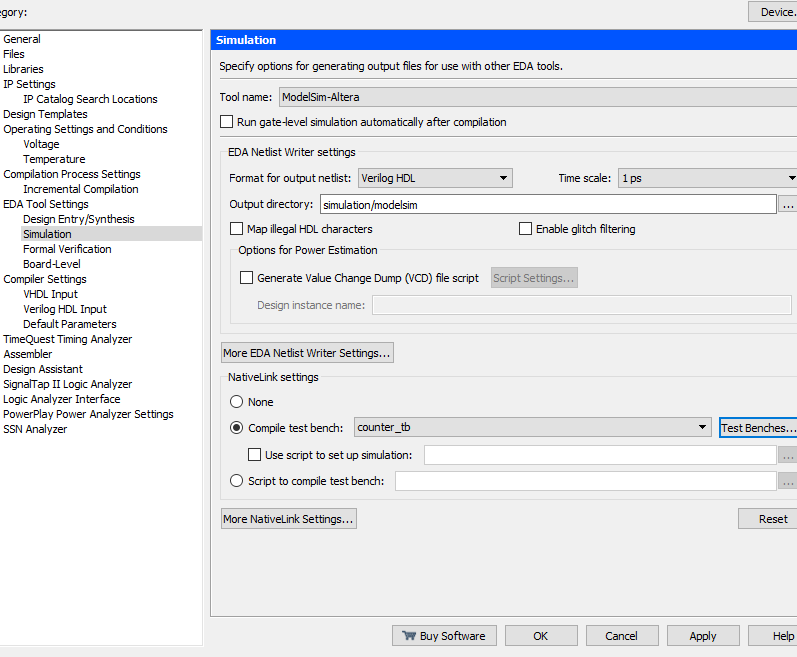

设置仿真

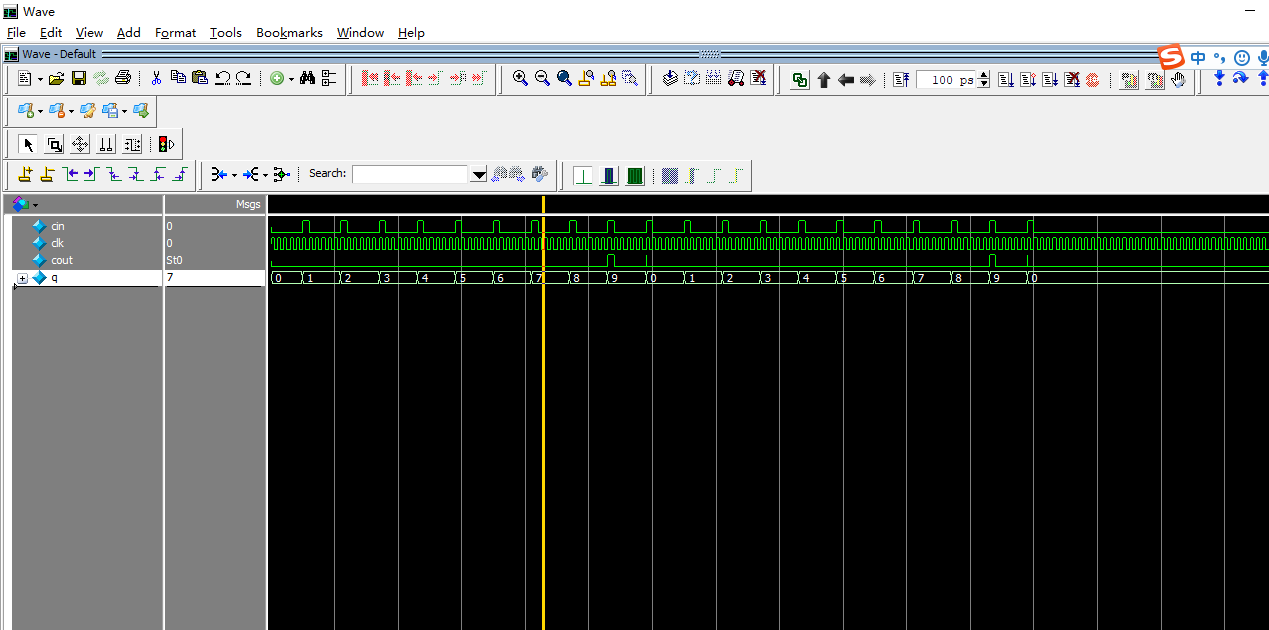

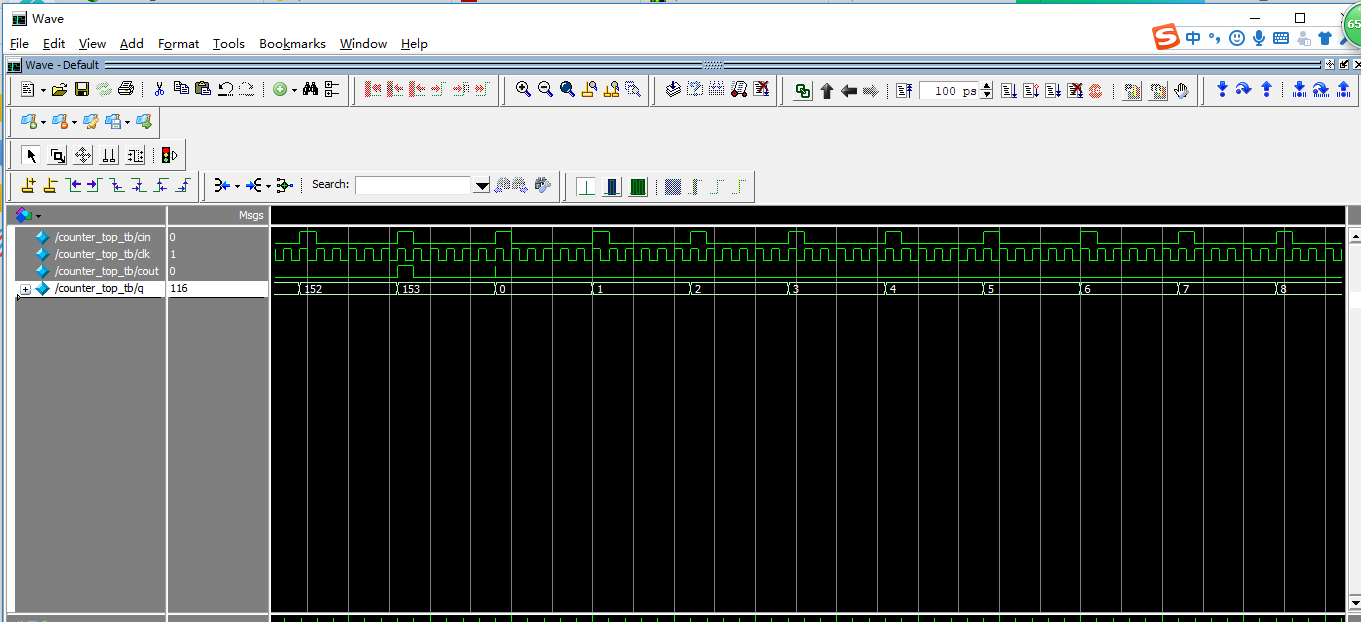

运行 仿真,可以看到每隔5个clk有一个cin信号,计数器完成一次计数,到计数到设定的模值10时会产生一次c_out信号,然后计数器重新开始从0开始计数,与设计的期望。

若要将计数器改为8位计数器:

(1)可以将 ip核改为8位

(2)也可以进行级联

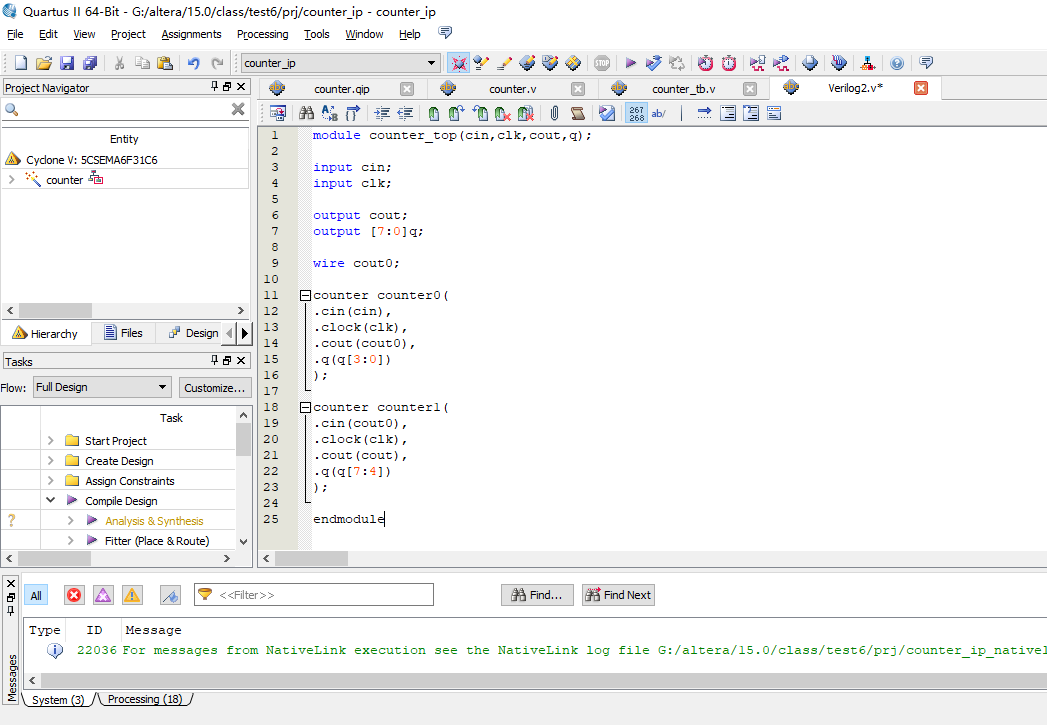

新建Verilog文件进行编程如下。

这里的原理是将前一级的c_out作为下一级计数的c_in,此时即将两个计数器级连起来了,这样就将一个四位的计数器转换成了一个八位的计数器。

将这个文件设置为顶层文件。

module counter_top(cin,clk,cout,q); input cin; input clk; output cout; output [7:0]q; wire cout0; counter counter0( .cin(cin), .clock(clk), .cout(cout0), .q(q[3:0]) ); counter counter1( .cin(cout0), .clock(clk), .cout(cout), .q(q[7:4]) ); endmodule 编写testbench如下 `timescale 1ns/1ns `define clock_period 20 module counter_top_tb; reg cin,clk; // 进位输入 计数基准时钟; wire cout;//进位输出 wire [7:0] q; counter_top counter0( .cin(cin), .clk(clk), .cout(cout), .q(q) ); initial clk = 1; always #(`clock_period/2)clk = ~clk; initial begin repeat(300)begin cin = 0; #(`clock_period*5)cin = 1; #(`clock_period)cin = 0; end #(`clock_period*200); $stop; end endmodule

2312

2312

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?