FPGA常见问题解决方法

- 0 使用加法,注意数据位宽的变化

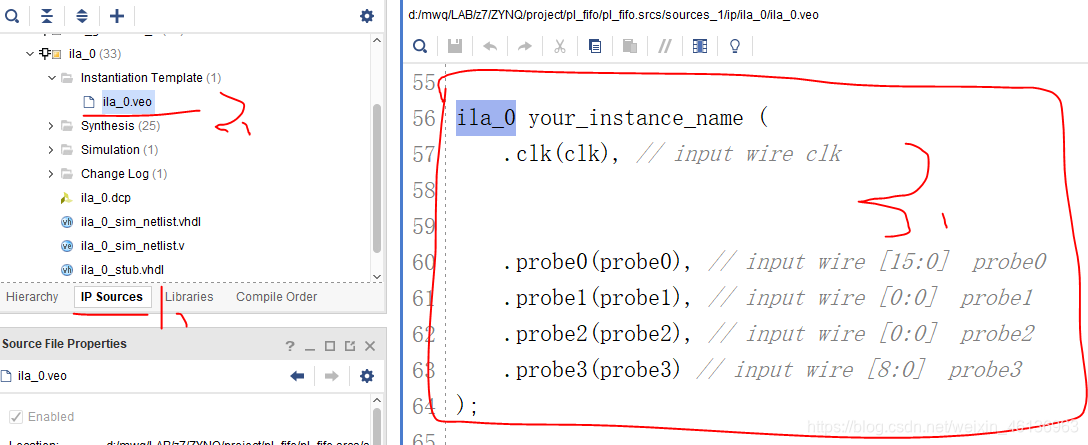

- 1 IP怎么调用

- 2 如何在仿真中观察更多的信号

- 3 仿真波形如何显示十进制数

- 4 常见快捷键

- 6 约束文件的两种方法

- 7 修改源文件或者约束文件或者BD后,发现ILa波形不变如何处理

- 8 xpm_fifo如何使用

- 9 什么时候用input、output;什么时候用wire。两者的区别是什么?

- 10 module 'xpm_fifo_async' not found

- 11 注意点

- 12 [DRC MDRV-1] 多驱动网络

- 13 自己封装的IP如何保证每次修改IP后,不会影响以前工程的IP。

- 14 光标变成黑块解决方法

- 15 testbench文件的报错如何找到错误详细信息

- 16 Vivado IP核锁定的解决办法(两种解决办法)

0 使用加法,注意数据位宽的变化

// 将四个阵元加权后的信号合成起来

//下面这行代码不对,没有考虑位宽的扩展

//assign real_y = Ct_1I+Ct_2I+Ct_3I+Ct_4I; // 实部

// 为什么需要扩展两位

// 比如:4个1相加等于4,加数只需要1bit进行表示,而和需要3bit进行表示,所以要扩展两位

// 由于最后只需要16bit,所以低两位不要。

wire [17:0] real_y_18bit;

wire [17:0] imag_y_18bit;

assign real_y_18bit = {Ct_1I[15],Ct_1I[15],Ct_1I}

+{Ct_2I[15],Ct_2I[15],Ct_2I}

+{Ct_3I[15],Ct_3I[15],Ct_3I}

+{Ct_4I[15],Ct_4I[15],Ct_4I}; // 实部

1 IP怎么调用

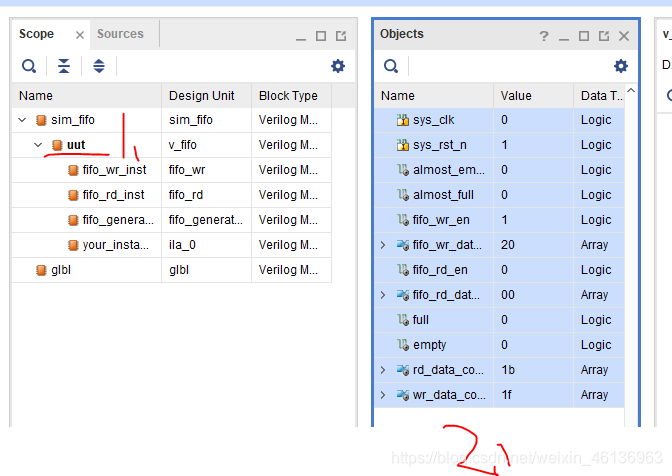

2 如何在仿真中观察更多的信号

跑出结果后—双击uut----选中object的所有信号—右键,点击 add to wave window

3 仿真波形如何显示十进制数

点击信号---------右键,点击radix--------点击 unsigned dec

4 常见快捷键

批量修改快捷键:Ctrl+Alt

6 约束文件的两种方法

法一:点击“Open Elaborated Design”------在弹出的窗口中点击“OK”按钮----------------在菜单中选择“Window -> I/O Ports”-----------在弹出的 I/O Ports 中可以看到管脚分配情况

法二:新建约束文件-----编写约束文件

7 修改源文件或者约束文件或者BD后,发现ILa波形不变如何处理

(1)检查是否export硬件,检查导出硬件时是否勾选了比特流文件。

(2)如果生成比特流文件所花时间较短,则重新生成比特流文件。

(3)关闭软件,重新启动。

(4)重新启动SDK端,并且选择debug界面。

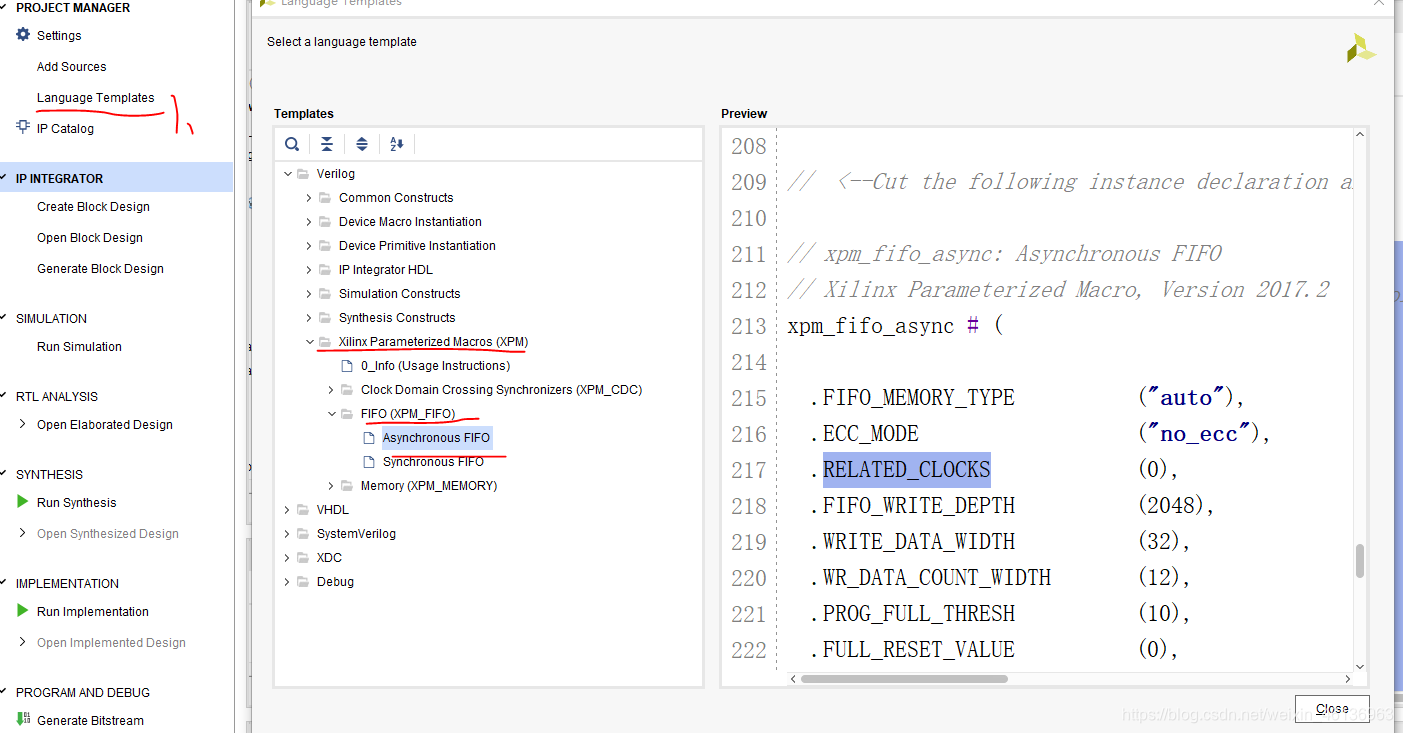

8 xpm_fifo如何使用

Language Templates--------- Verilog-----------Xilinx Parameterized Macros(XPM)--------XPM--------XPM_fifo-----------Asynchronous FIFO,复制到.v中,如下图所示

/*

* Instantiate async fifo by using Xilinx parameterized Macros. For ultrasclae, refer to ug974, for 7 series ug953

* write and read depth is 1024, write and read data width is 8

*/

xpm_fifo_async #(

.CDC_SYNC_STAGES (2),

.DOUT_RESET_VALUE ("1"),

.ECC_MODE ("no_ecc"),

.FIFO_MEMORY_TYPE ("auto"),

.FIFO_READ_LATENCY (1),

.FIFO_WRITE_DEPTH (1024),

.FULL_RESET_VALUE (0),

.PROG_EMPTY_THRESH (10),

.PROG_FULL_THRESH (10),

.RD_DATA_COUNT_WIDTH (11),

.READ_DATA_WIDTH (8),

.READ_MODE ("std"),

.RELATED_CLOCKS (0),

.USE_ADV_FEATURES ("0707"),

.WAKEUP_TIME (0),

.WRITE_DATA_WIDTH (8),

.WR_DATA_COUNT_WIDTH (11)

)

xpm_fifo_async_inst (

.rst (~adc_rst_n),

.wr_clk (adc_clk),

.wr_en (adc_buf_wr),

.din (adc_buf_data),

.rd_clk (M_AXIS_CLK),

.rd_en (adc_buf_rd),

.dout (M_AXIS_tdata),

.empty (empty),

.full (),

.almost_empty (),

.almost_full (),

.wr_data_count (),

.rd_data_count (),

.prog_empty (),

.prog_full (),

.data_valid (),

.dbiterr (),

.sbiterr (),

.overflow (),

.underflow (),

.wr_ack (),

.wr_rst_busy (),

.rd_rst_busy (),

.injectdbiterr (1'b0),

.injectsbiterr (1'b0),

.sleep (1'b0)

);

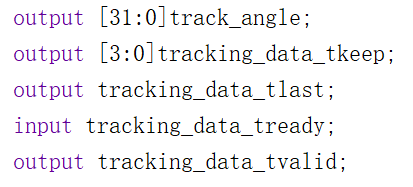

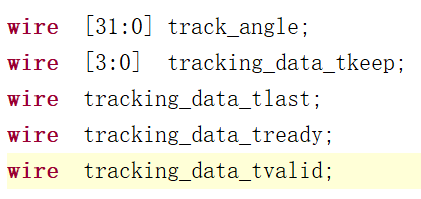

9 什么时候用input、output;什么时候用wire。两者的区别是什么?

第一种情况:用input、output。

用input、output需要编写这5个信号的约束文件。

第二种情况:wire。

此时不需要编写这5个信号的约束文件。

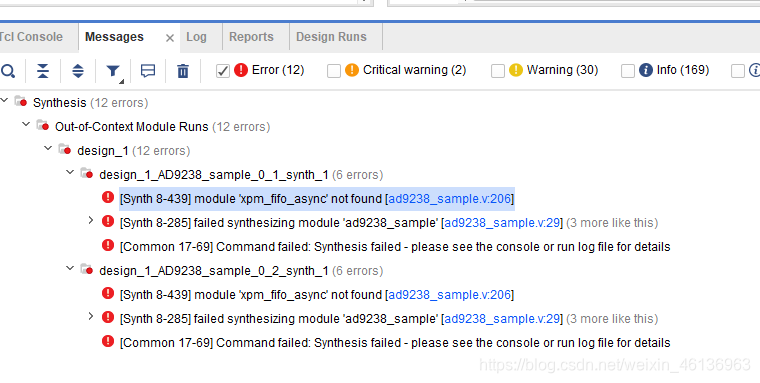

10 module ‘xpm_fifo_async’ not found

解决方法:

在TCL console输入命令:

set_property XPM_LIBRARIES XPM_FIFO [current_project]

11 注意点

(1)“Run As”时最好勾选复位,以及program 比特流文件。

(2)有 PL 的设计要“Program FPGA”,如果PL 多次修改,别忘了重新导出硬件。

12 [DRC MDRV-1] 多驱动网络

13 自己封装的IP如何保证每次修改IP后,不会影响以前工程的IP。

(1)将IP封装好后,命名为repo。

(2)每建立一个工程文件时,将repo文件复制在该工程目录下。

(3)打开该工程,注意删除以前的IP repo文件,重新添加本工程文件目录下的IP repo.

14 光标变成黑块解决方法

按一下 insert即可

15 testbench文件的报错如何找到错误详细信息

打开.sim文件,\sim_1\behav目录下

16 Vivado IP核锁定的解决办法(两种解决办法)

法一:

1.生成IP核的状态报告 Tools -> Report -> Report IP Status

2.点击Upgrade Selected

3.更新完成后IP Status

法二:

下面介绍另一种方法,对应上述方法不能使用的情况(Upgrade Selected 按钮是灰色的 情况)

在 Tcl console中 执行如下一条命令即可:

upgrade_ip [get_ips]

938

938

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?