一、quartusII简介

quartusII是一款集成式的EDA软件,主要用于FPGA的开发,包括了verilog代码编辑器、综合器、仿真器等,其还可以与modelsim实现联合仿真。

软件下载见:我的安装过程记录见博文,这是我转载的B站的视频以及我的下载记录,该视频我觉得讲得非常详细,非常适合入门,感谢!

注意:在quartusII软件中,命名Verilog代码文件名(.v)需要与模块名保持一致,且不能用中文或全数字命名。

此外,推荐参考书黄继业、潘松《EDA技术实用教程》第六版,作为初学者觉得可读性很高。

二、quartusII常用功能

2.1 项目内顶层文件切换与不同项目间切换

任何一项设计都是一项project,需要保持在一文件夹内。(因此,同一工程的所有文件都应在同一文件夹,而不同的项目就最好放不同文件夹)

- 项目内顶层文件切换

Asignment-Setings-General-Top-level entity - 不同项目间切换

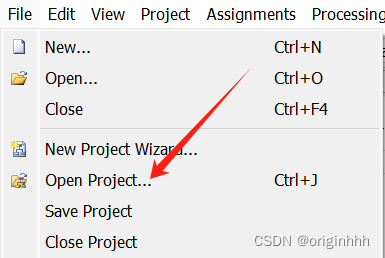

如需要切换项目,应该点击Open Project,选择相应项目的文件夹,选择QPF文件,而不是上方的Open File。

2.2 RTL级图形观察

- start compilation编译成功后,Tool-Netlist-RTL Viewer,即可看到对应代码的RTL级电路。

2.3 代码仿真验证(这里没有加延时,主要是功能仿真之类的)

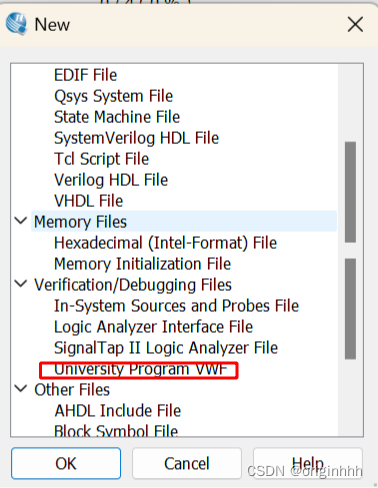

quartusII自带的仿真自带的仿真软件已经慢慢被放弃,目前主流是与第三方仿真软件,如ModelSim,如果代码功能比较简单可以选择University Program VWF 进行仿真,如果代码功能比较复杂则可以通过编写对应代码的测试代码(常称为Test Bench)直接使用ModelSim联合仿真。(如果刚开始安装quartusII时未安装ModelSim,需要安装仿真器后才可使用)

- VWF仿真(按如下操作)

- 创建仿真

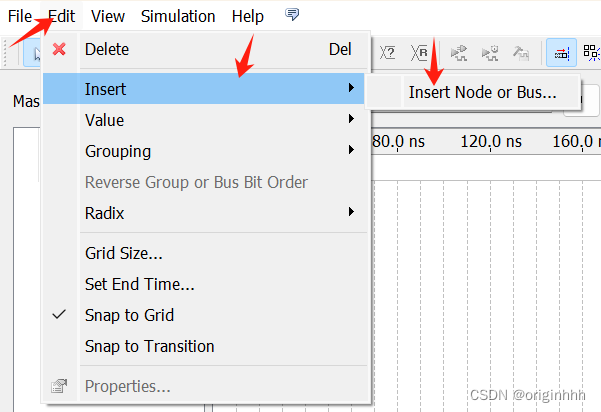

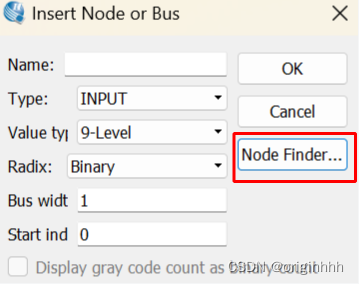

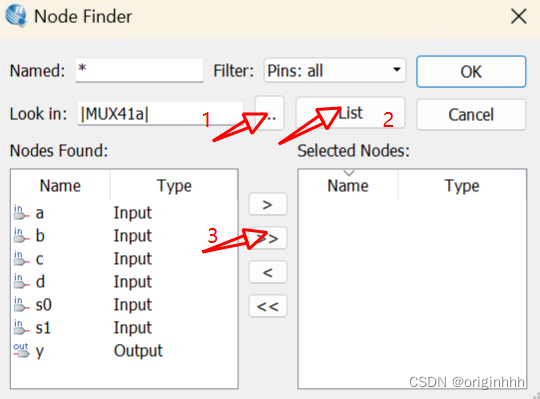

2. 插入端口

3. 设置仿真时间:Edit-Set End Time,看电脑性能与个人需求决定,如10us。

4. 设置输入信号(有两种方法)

方法1(总体设置)

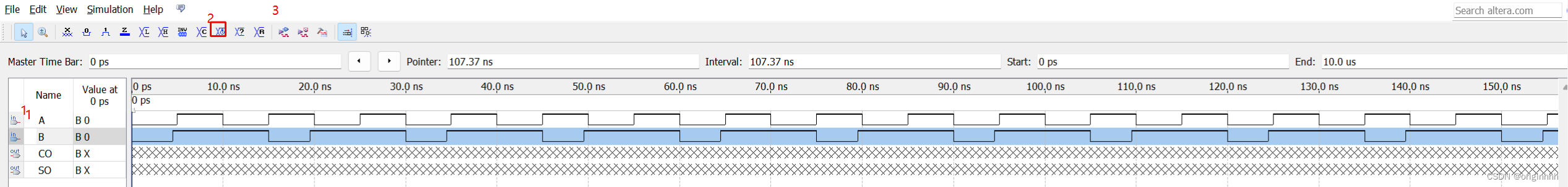

分别选择输入端口(1处),分别设置输入信号(2处),其中,Period是周期总长、Duty cycle是高电平信号在一个周期中的占比,进行仿真(3处)。总体设置可以方便的产生输入信号的总体波型。

方法2(特殊设置)

总体设置输入信号,很难根据自己想要研究的问题设置特定的波形输入形式,于是我们可以在某一特定的区域按照我们自己的需求更改输入波形。

- 可以点击鼠标左键在输入信号需要更改的区域拖动,最后会形成一个方框,再点击上方工具栏中?标,即可更改选中区域的输入信号。

- 方框最少需要选中两网格线之间的距离,可以在Edit-Grid Size中修改网格线宽度。

争对波形图的放大与缩小,做出如下说明,选择功能表中缩放标,左击放大、右击缩小。

Modelsim联合仿真

使用改功能,需要写一段用于仿真测试Testbench代码,该代码文件应该与本项目在同一文件夹内。

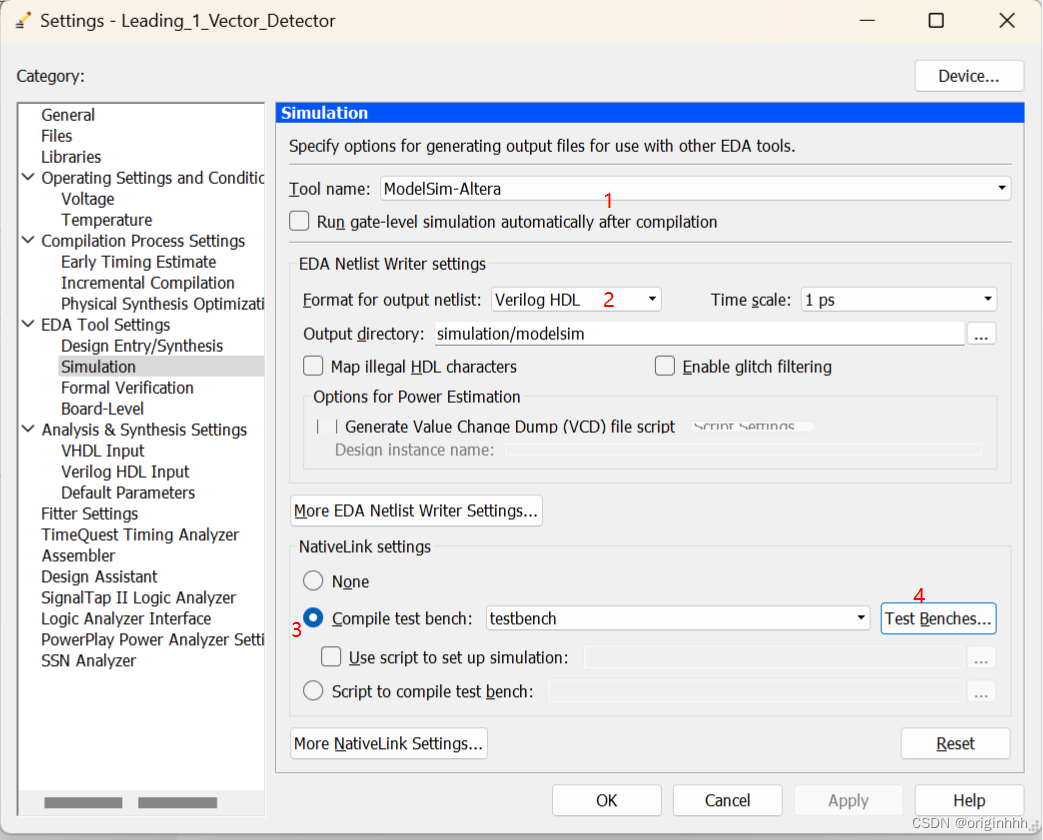

- assignment-EDA Tool Setting-simulation,即可进入该界面。

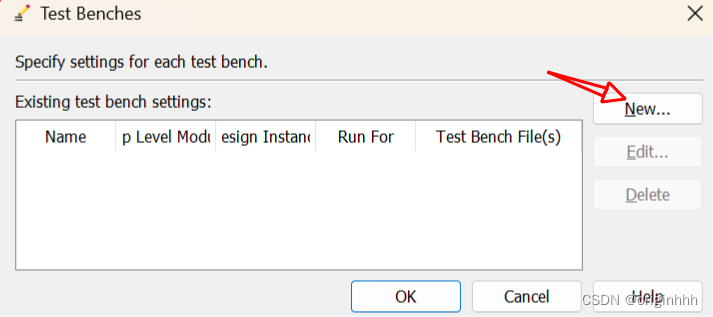

- 按顺序操作完成后,点击第4处即可进入如下界面。

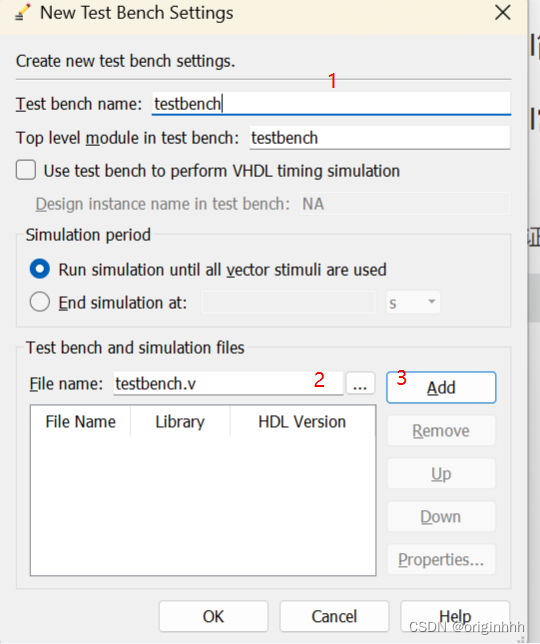

- 在1处输入自己命名的测试文件名(如我的就叫testbench),2处选择对应的测试代码文件,点击Add。注意:需要(1与2处)的文件名需一致

- Tools-Run Simulation Tool-RTL Simulation

三、modelsim仿真单独使用流程

- 文件管理

- 在自己的代码存储文件夹中创建一个用于保存modelsim文件的文件夹,比如我的在E:\Program_Project\Modelsim_project中。

- 然后在该目录下给对应项目创建一个文件夹E:\Program_Project\Modelsim_project\filter1

- 工程创建与导入

- 创建一个工程,File-New-project

选择刚刚工程的文件地址:E:\Program_Project\Modelsim_project\filter1

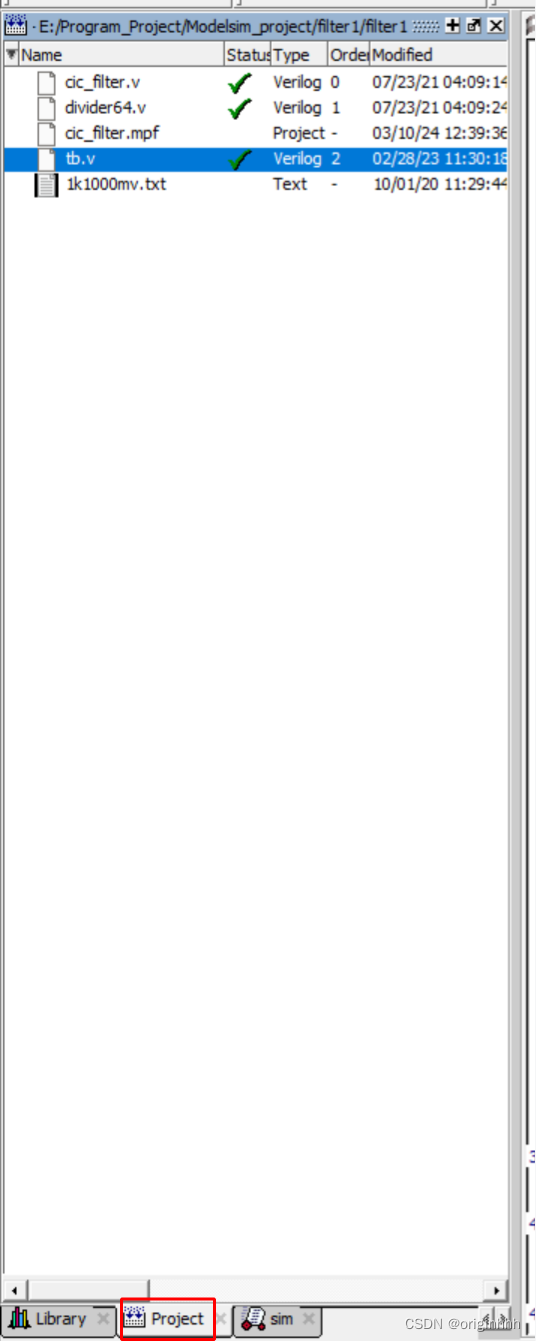

工程名:filter1 - 导入已有源代码,找到如图Project,如果没有在View中进行添加

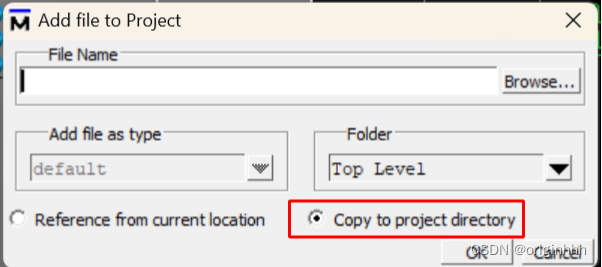

- 导入源代码,在Project中右键

add to project-Exsting Files(注意选择copy to project directory!!)

- 编译与仿真

- 编译,同样在Project下右键,compile

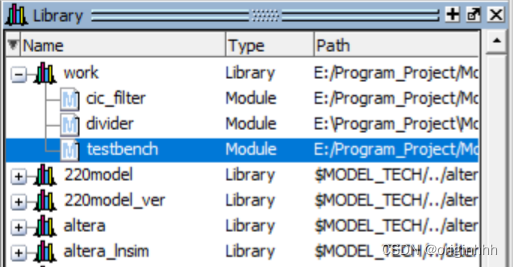

- 仿真,View下找到Library-work-testbench,右键simulate

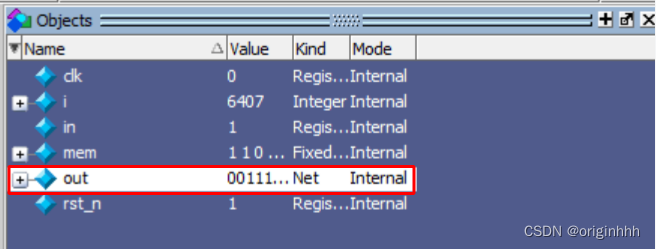

- 找到Object界面,右键add wave,这里我们添加输出out,其他信号输入同理添加波形

- 设置仿真时间,开始仿真(点击:run,如果继续点击run会仿真下一段仿真时间,如设置仿真时间1ms,再次点击run,就会仿真出1~2ms的仿真波形,以此类推)

- 关于Wave界面的一些说明

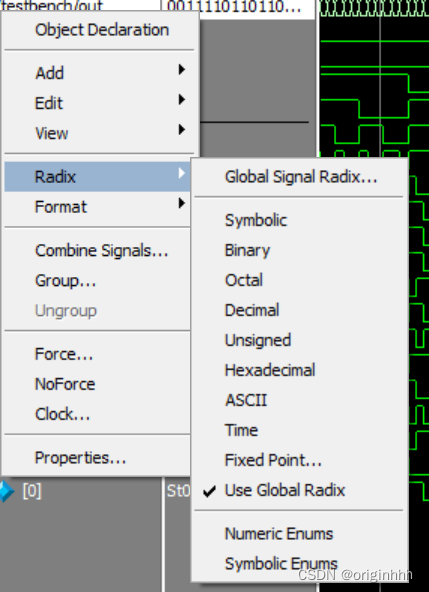

- 选择信号,Radix选择信号几进制

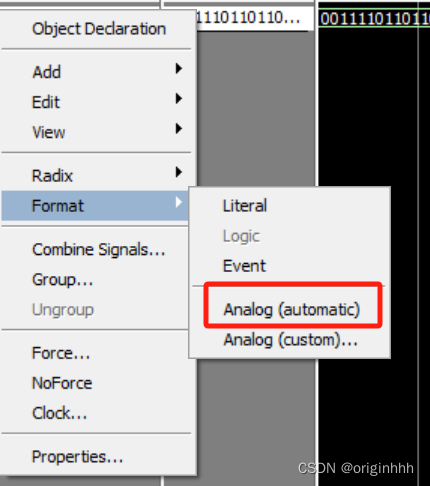

- 产生模拟信号

四、在FPGA上实现

其实单纯从操作流程上看,其实可以跑一个简单的流水灯算法(FPGA开发界的hello,world)熟悉一下流程即可,因此数字集成电路前端设计又回归到了本质:算法设计与系统架构

5033

5033

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?