面试官通常还喜欢在某个点深入的询问下去,特别是一些通用的的偏中端的问题,作为一个前端设计工程师,仅仅会写RTL代码是远远不够的。

CDC分析主要分析内容:

1.未同步的跨时钟域问题Ac_Unsynch01,Ac_Unsynch02

主要报告单bit或者多bit未做跨时钟域的问题。

2.跨时钟域处理错误(Clock_sync)

不同时钟域信号直接组合逻辑、或者同一信号在同一时钟域分别做多次同步

3.聚合问题AC_conv01/02/03

当多个信号或者单个信号分开跨时钟域后又汇合,会出现聚合问题。引起竞争和冒险

聚合问题有可能会引起数据一致性(data coherency)问题,即同步前的数据与同步后的数据不一致。

解决办法:clk1的输出采用时序逻辑输出,不要采用组合逻辑输出。

4数据丢失AC_cdc01a

比如快时钟跨时钟域到慢时钟,未做展宽。

5.毛刺问题

数据毛刺和时钟毛刺

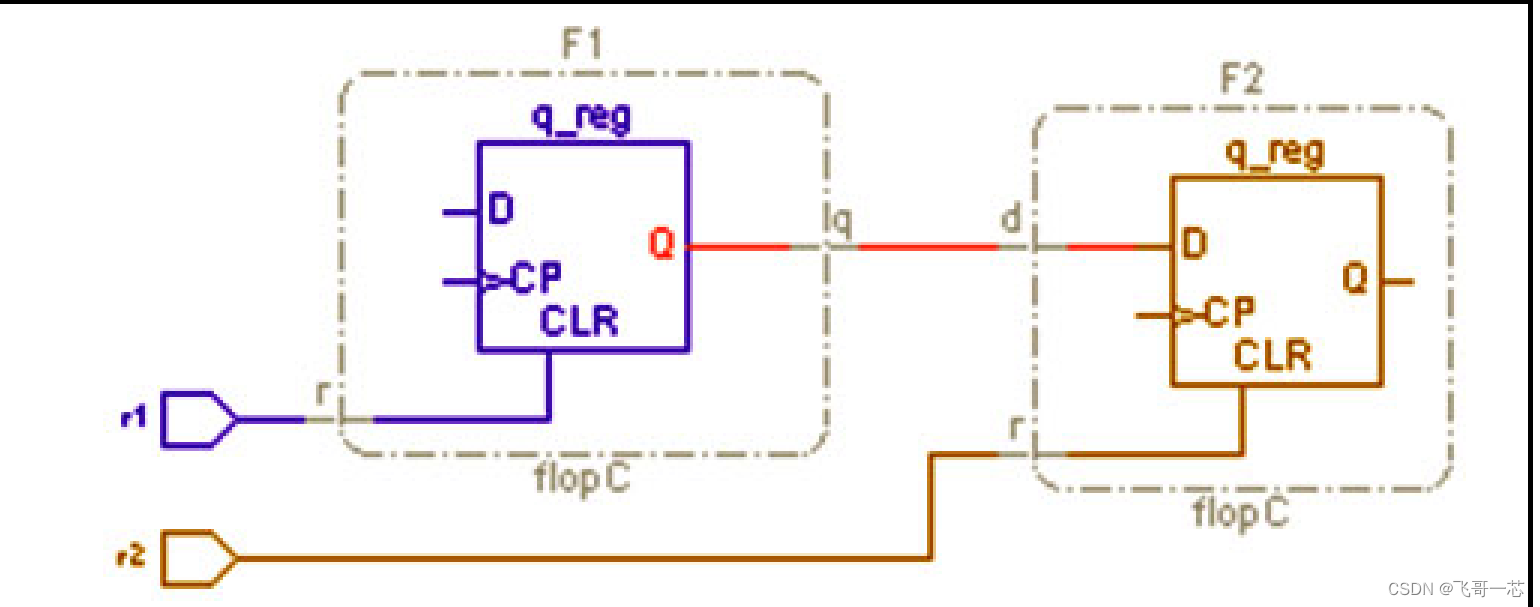

6..复位同步问题Ar_*

用于分析复位相关,比如是否做同步释放,同一时钟域复位不同时钟域。

7.RDC(Reset Domain Crossing)

复位顺序带来亚稳态。

解决方法1:过滤法,通过保证复位顺序来避免亚稳态

解决方法2&

订阅专栏 解锁全文

订阅专栏 解锁全文

751

751

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?