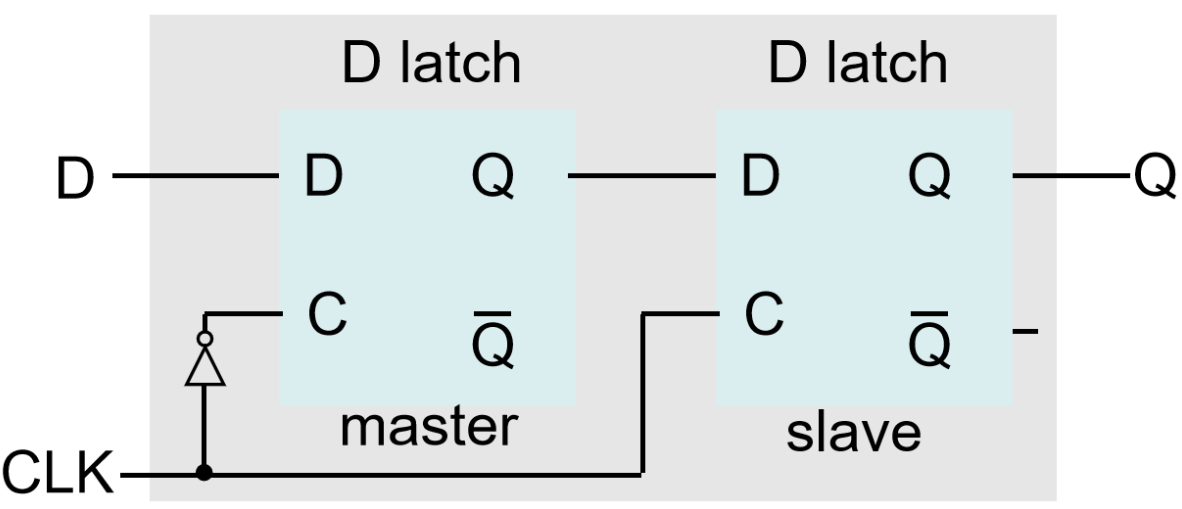

Q:本篇我们设计由2个D锁存器(主-从拓扑结构)组成的基本D触发器。

A:基本D触发器工作原理:主锁存器的输出作为从锁存器的输入,主锁存器的时钟信号与从锁存器的时钟信号相反,即当CLK=0时加载主锁存器的值;CLK=1时加载从锁存器的值,当CLK从0跳变为1时,主锁存器无效,会自动加载从锁存器的值。在D触发器中,仅当CLK的输入值发生从“0”到“1”的转变时(即时钟上升沿),D的值才会被存储到输出Q中。

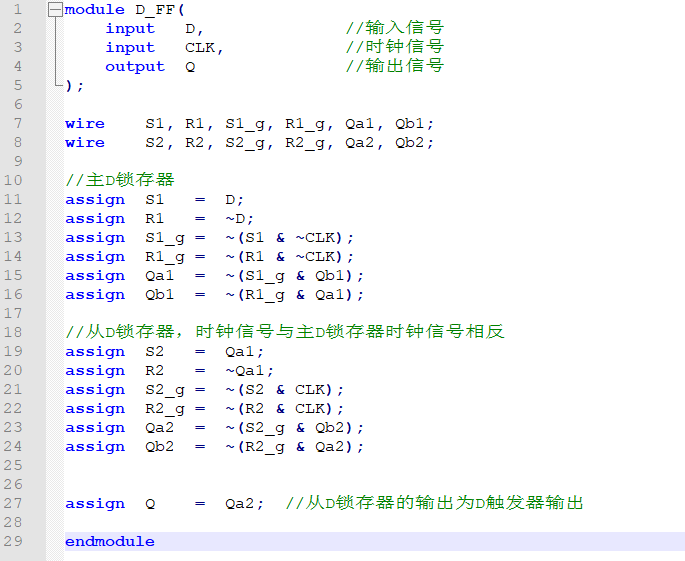

部分Verilog HDL代码:

例化D触发器:使用DE2-115开发板的SW[0]作为数据输入D,KEY[0]作为时钟输入CLK;LEDR0显示D触发器的输出值Q。

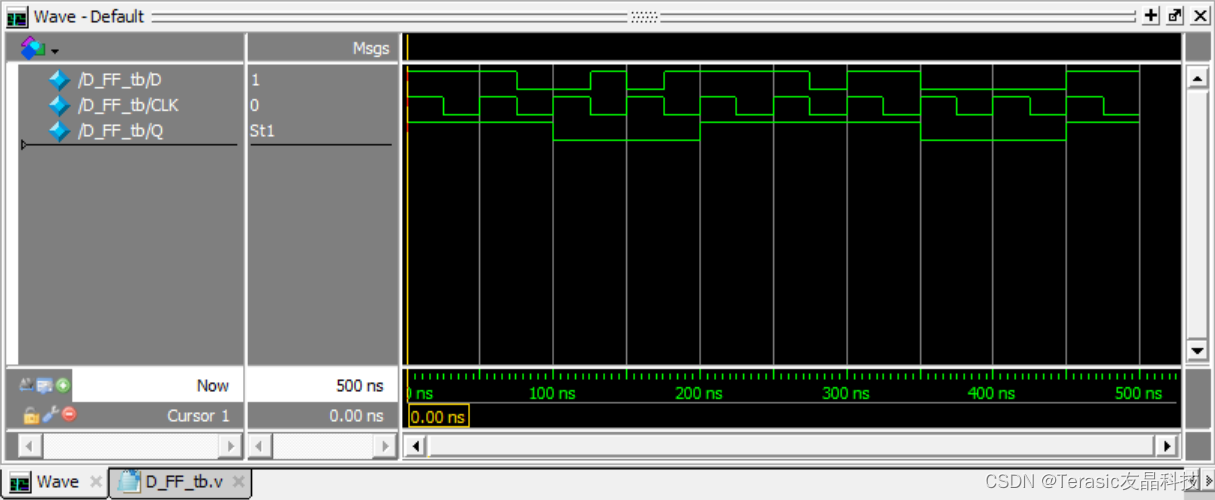

ModelSim仿真结果:

本文介绍了由两个D锁存器构成的D触发器的工作原理,详细阐述了主从锁存器的时钟控制机制。并通过VerilogHDL代码示例展示了如何实例化D触发器,并在DE2-115开发板上进行ModelSim仿真,展示了输出值的变化过程。

本文介绍了由两个D锁存器构成的D触发器的工作原理,详细阐述了主从锁存器的时钟控制机制。并通过VerilogHDL代码示例展示了如何实例化D触发器,并在DE2-115开发板上进行ModelSim仿真,展示了输出值的变化过程。

2796

2796

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?