Q:本篇我们采用寄存器来实现时序逻辑电路--4位计数器。

A:与四个T 触发器构成的4位同步计数器类似,寄存器包含一个使能端口、复位端口、时钟输入端口以及4位输出。

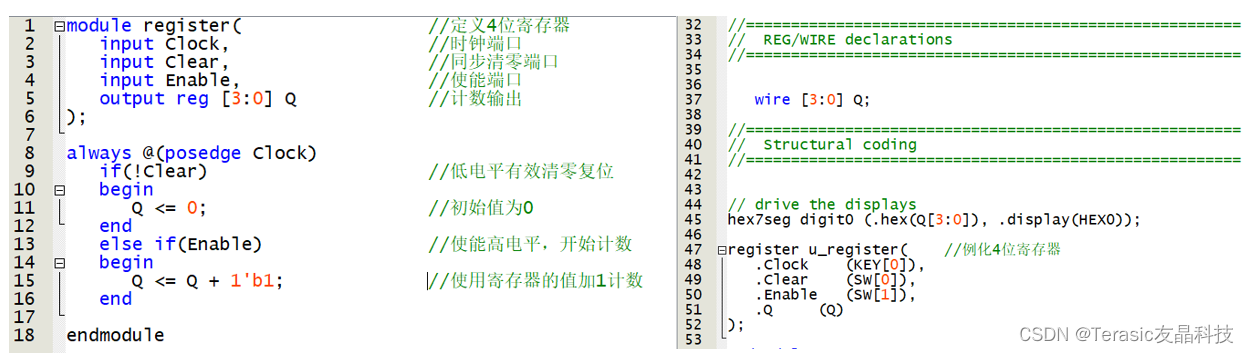

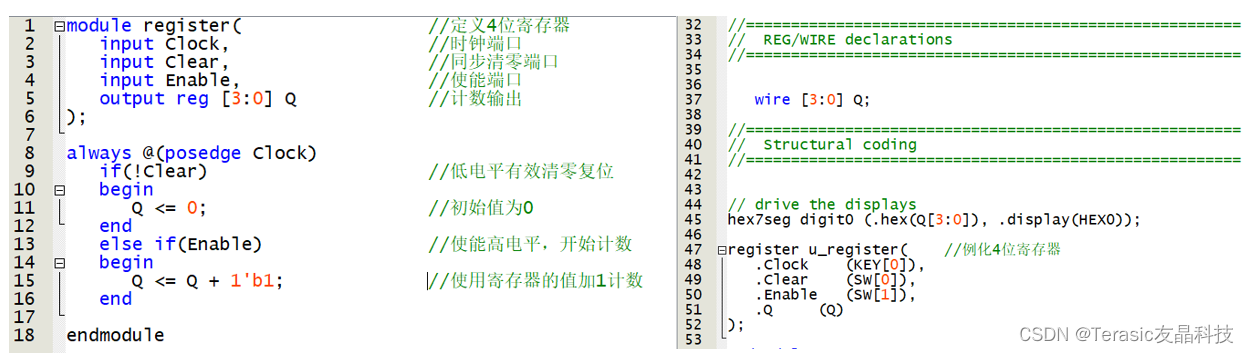

寄存器以及例化部分Verilog代码:

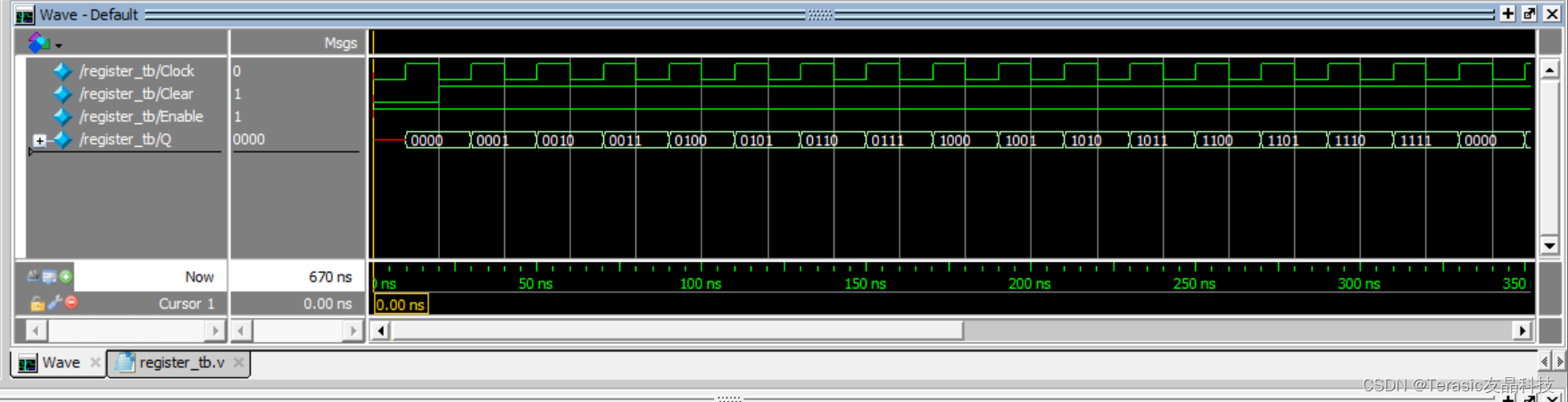

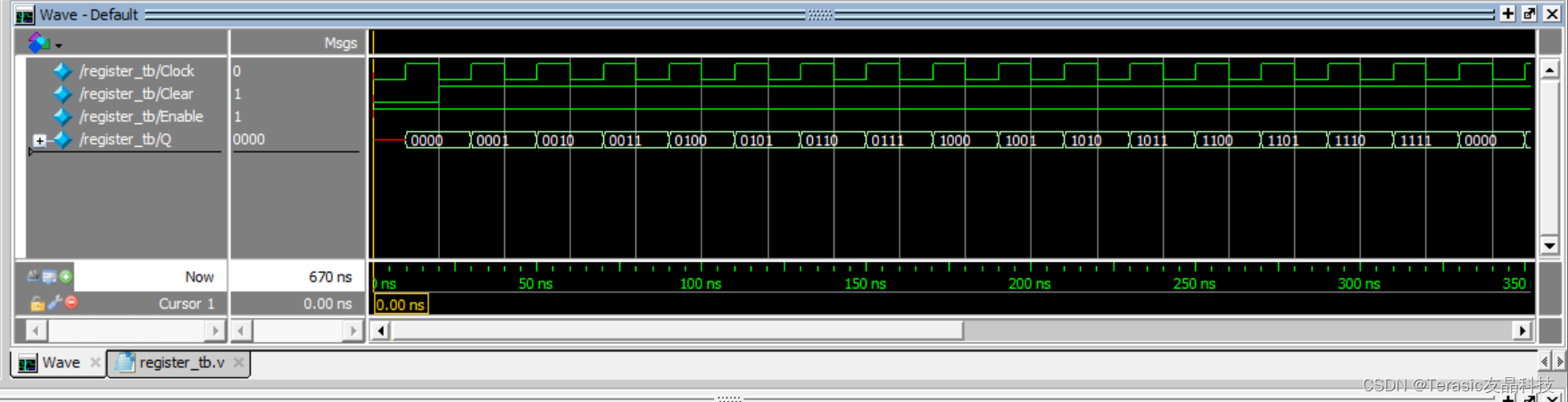

使用DE2-115开发板的SW[0]作为同步复位信号Clear,SW[1]作为使能信号Enable,KEY[0]作为时钟信号Clock,计数器的计数值以十六进制的形式显示在数码管HEX0上。ModelSim仿真结果:

Q:本篇我们采用寄存器来实现时序逻辑电路--4位计数器。

A:与四个T 触发器构成的4位同步计数器类似,寄存器包含一个使能端口、复位端口、时钟输入端口以及4位输出。

寄存器以及例化部分Verilog代码:

使用DE2-115开发板的SW[0]作为同步复位信号Clear,SW[1]作为使能信号Enable,KEY[0]作为时钟信号Clock,计数器的计数值以十六进制的形式显示在数码管HEX0上。ModelSim仿真结果:

6247

6247

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?