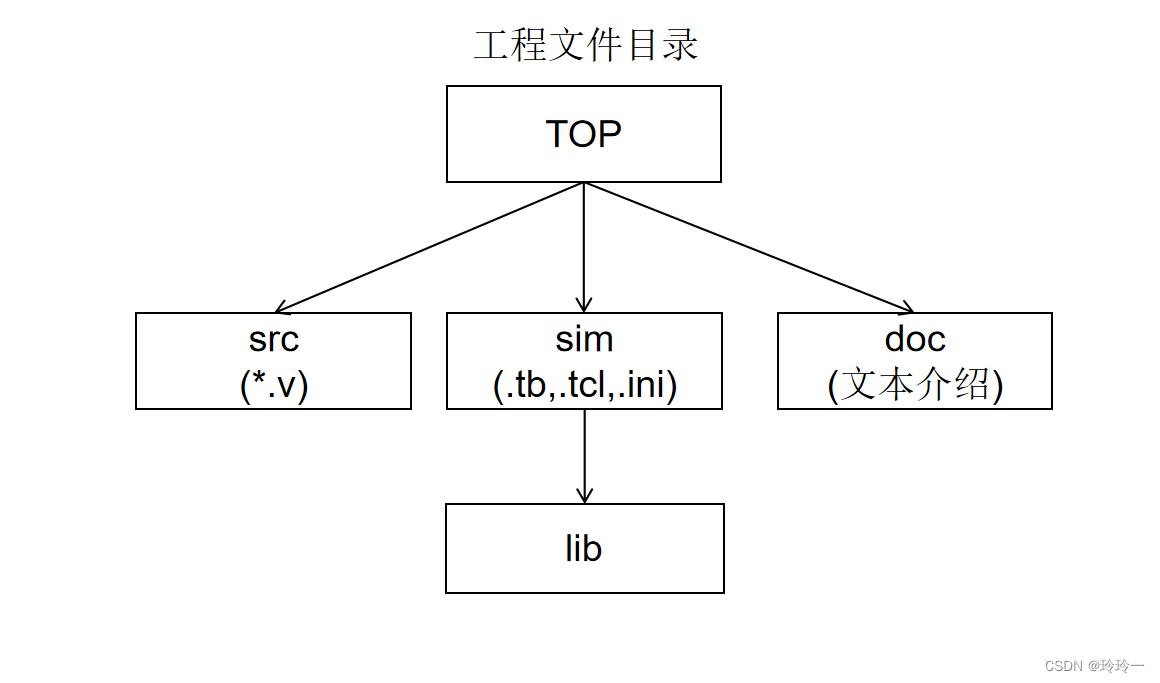

1.工程文件目录的创建

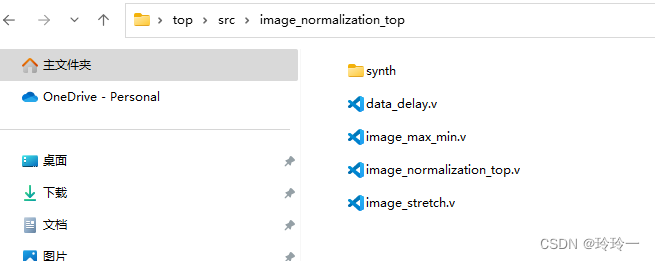

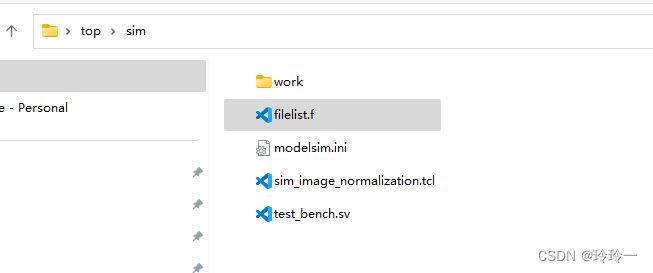

有层次的创建工程可以更加高效的完成功能仿真验证。所有.v源码放在src文件夹,testbench,tcl脚本和工程配置文件放在sim文件夹,在sim文件夹下创建一个work文件夹存放lib文件,doc文件夹下存放项目介绍,修改记录等文本文件。

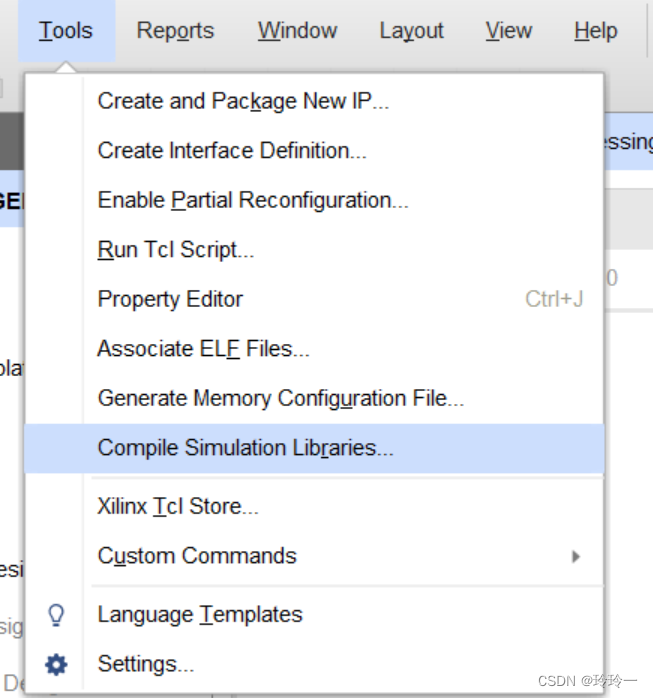

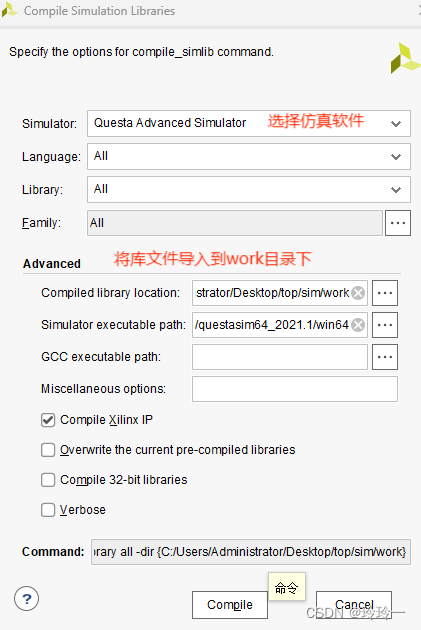

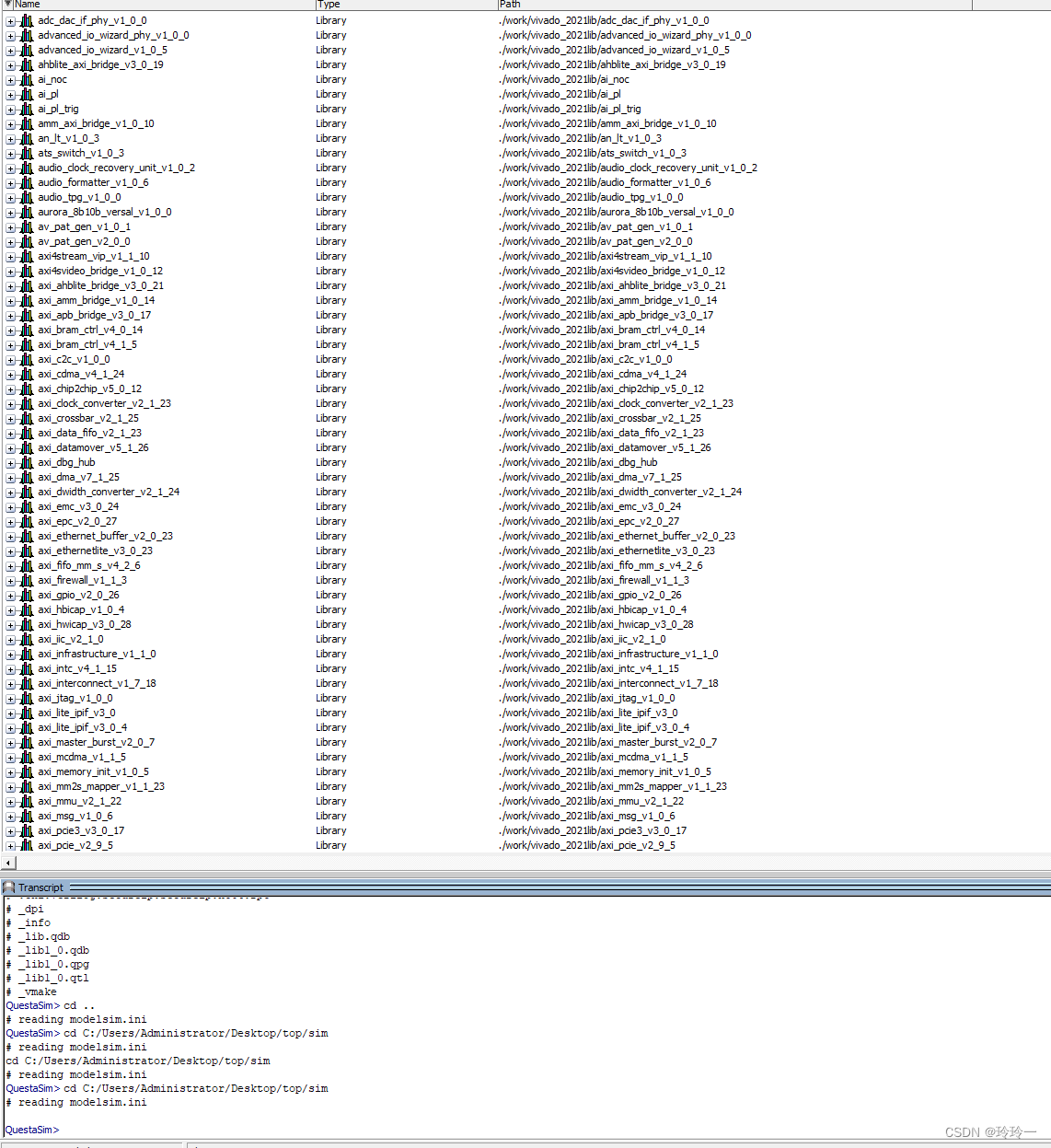

2.添加vivado ip库

首先需要打开vivado软件导出仿真库

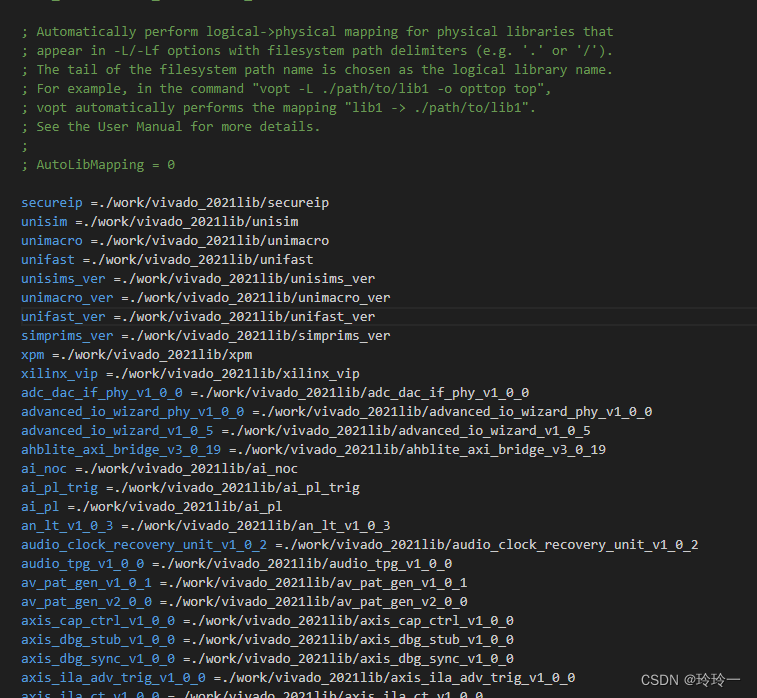

vivado库导出完成后进入work目录下找到modelsim.ini文件,并将其复制到sim文件夹下,使用文本编辑器修改modelsim.ini文件中库文件的索引路径(最好改成相对路径)

打开questasim软件,在命令行处cd到modelsim.ini文件所在目录,questasim会自动加载配置文件,如下图所示表明vivado仿真库正确添加

3.将需要仿真的源文件放在src目录下,tb文件放在sim目录下

4.使用TCL编写自动化仿真脚本

4.1.常用tcl指令介绍

set: 设置变量

USER_DEFINED_VERILOG_COMPILE_OPTIONS:define宏定义变量,写法“+define+HONG_NAME”;

TOP_LEVEL_NAME:顶层模块名,这里给test_bench;

logical_libraries:编译库列表,创建列表的基本方法是将列表的元素放在大括号内, 列表元素由空格分隔

# setup variables for simulation script

set USER_DEFINED_VERILOG_COMPILE_OPTIONS "+define+MODELSIM +define+SIM"

set TOP_LEVEL_NAME test_bench

set logical_libraries [list "work" "work_lib"]vlib:创建库

在物理目录创建库,用法:vlib <path>

vmap:将库映射到工作库

虚拟库映射到真实文件夹

#创建一个库,名字叫vivado_work

vlib vivado_work

vlib ./vivado_work/work

#将vivado_work库链接到工作库

vmap vivado_work workvlog:编译verilog和systemverilog文件到working库

添加-work work就是将.v文件编译的结果放到到work库,便于中间文件管理,如果不指定库就是编译到默认库。用法:vlog -sv -work <work> <path>

+notimingchecks:屏蔽时序检查,加快仿真速度;

+nospecify:仿真时忽略库文件中指定的路径延时;

vlog -sv $USER_DEFINED_VERILOG_COMPILE_OPTIONS ../../../src/image_normalization_top/*.v -work workvcom:编译.vhd文件

vcom $USER_DEFINED_VERILOG_COMPILE_OPTIONS ./sim/*.vhdvsim

该命令用于启动questasim仿真环境,使用方法

vsim [option] [design_unit]

options:可选的仿真选项;

design_unit:要仿真的设计文件,可以是顶层模块,可以是实例也可以是信号;

"-voptargs=+acc":优化部分参数加快仿真速度 ;

"-t ns":指定仿真时间分辨率;

“ -L vivado_lib -L work ” :把逻辑映射库 vivado_lib 和逻辑映射库 work 链接起来,因为不同的源文件vlog或vcom的结果放在了不同的库路径下,需要将所有编译后的结果链接起来。

vsim -t ns -voptargs=+acc -L vivado_lib -L work test_benchrun

该命令用于执行仿真过程,指令格式:run [option] [time_limt];

option:可选的运行选项;

time_limt:单步执行的时间限制;

#连续仿真

run -all

#单步仿真

run 10uslog -rec /*

记录所有的信号,运行这个命令后即使在仿真前没有把信号加入wave窗口,仿真完成后直接加入wave窗口就可以查看波形,比较方便,但是缺点是当工程较大和仿真时间很长时仿真速度较慢,占用内存也较大。

append指令

append 命令比较简单,它将一段字符串连接到另一字符串尾部从而组成新的字符串。此命令对变量直接修改。

set elabcommand " "

set lib1 "-L vivado_lib"

set lib2 " -L work_lib"

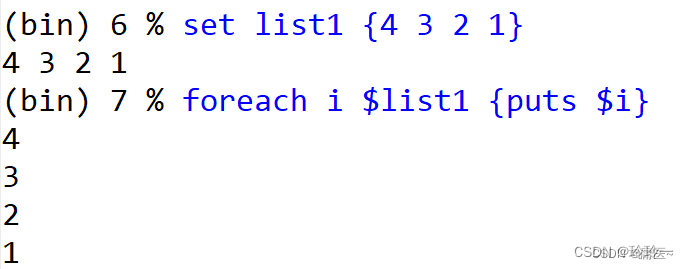

append elabcommand $lib1 $lib2foreach指令

反复循环操作一个或多个列表的每个元素

语法 :foreach 变量 列表 循环主体

功能: 从第0个元素开始,每次按顺序取得列表的一个元素,将其赋值给变量,然后执行循环主体一次,直到列表最后一个元素

例如:foreach library list body {...}

foreach命令执行一个循环,循环的变量是一个或多个列表的元素。最简单的情况下是一个循环变量 library和一个列表 list, list中的值一次分配给library。 body是一个Tcl脚本,对于每个 list中的元素(顺序是由第一个到最后一个), foreach分配元素的内容给 library,然后调用Tcl解释器去执行 body。

set logical_libraries [list "work" "vivado_lib"]

set elabcommand " "

foreach library $logical_libraries { append elabcommand " -L $library" }

append elabcommand " $TOP_LEVEL_NAME"

eval vsim -voptargs=+acc $elabcommandalias指令

为一个可执行程序定义一个别名,定义一个build可执行命令,用于编译所有的源文件。定义一个rerun命令用于配置仿真环境,添加仿真波形,设置仿真运行时间。

# compile system, only need to run once (without IP and src changes)

alias build {

vlog -sv $USER_DEFINED_VERILOG_COMPILE_OPTIONS ../src/image_normalization_top/*.v

vcom $USER_DEFINED_VERILOG_COMPILE_OPTIONS ./sim/*.vhd

vlog -sv $USER_DEFINED_VERILOG_COMPILE_OPTIONS test_bench.sv

}

alias elab_debug2 {

set elabcommand " "

foreach library $logical_libraries { append elabcommand " -L $library" }

append elabcommand " $TOP_LEVEL_NAME"

eval vsim -voptargs=+acc $elabcommand

}

alias rerun {

elab_debug2

log -rec /*

#添加默认仿真观测信号

do wave.do

run -all

}filelist文件编写与添加

较大的工程仿真时需要添加很多源文件,一个一个源文件在tcl中添加不利于文件管理。

+incdir+ `include文件的搜索目录。

+define+HONG_NAME :define 宏定义

filelist.f文件写法如下:

+incdir+ ./inc/memory.h

./lib/memory/dpram_1280x14/dpram_1280x14.v

./lib/memory/dpram_1280x14/dpram_1280x14_rtl.v

./lib/memory/dpram_1280x32/dpram_1280x32.v

./lib/memory/dpram_1280x32/dpram_1280x32_rtl.v

./lib/memory/dpram_4096x10/dpram_4096x10.v

./lib/memory/dpram_4096x10/dpram_4096x10_rtl.v

./lib/memory/dpram_4096x14/dpram_4096x14.v

./lib/memory/dpram_4096x14/dpram_4096x14_rtl.v

./lib/memory/dpram_16384x10/dpram_16384x10_rtl.v

./lib/memory/dpram_16384x14/dpram_16384x14_rtl.v通过tcl脚本命令添加filelist.f文件,并对其编译

vlog +notimingchecks +nospecify -f filelist.f -work workadd wave 添加仿真信号观测列表

可以将要查看的信号通过 add_wave指令写入wave.do文件中,启动仿真时会自动加载wave窗口。

add wave -position insertpoint sim:/test_bench/image_DeNoise/*

add wave -position insertpoint sim:/test_bench/image_DeNoise/DNS_guide_ab_out_11x11_inst/*vsim -view 浏览仿真波形

通过vsim -view TOP_NAME.wlf指令浏览上一次仿真结束后保存的波形文件

4.2完整TCL自动化仿真脚本

#quit current sim

quit -sim

#clear transcript

.main clear

# setup variables for simulation script

set USER_DEFINED_VERILOG_COMPILE_OPTIONS "+define+MODELSIM +define+SIM"

set TOP_LEVEL_NAME test_bench

set logical_libraries [list "work" "vivado_lib"]

# compile system, only need to run once (without IP and src changes)

alias build {

# vlog +notimingchecks +nospecify -f filelist.f -work work

vlog -sv $USER_DEFINED_VERILOG_COMPILE_OPTIONS ../src/image_normalization_top/*.v

# vcom $USER_DEFINED_VERILOG_COMPILE_OPTIONS ./sim/*.vhd

vlog -sv $USER_DEFINED_VERILOG_COMPILE_OPTIONS test_bench.sv

}

alias elab_debug2 {

set elabcommand " "

foreach library $logical_libraries { append elabcommand " -L $library" }

append elabcommand " $TOP_LEVEL_NAME"

eval vsim -voptargs=+acc $elabcommand

}

alias rerun {

elab_debug2

log -rec /*

run -all

}

5.TCL脚本使用方法

1.打开questam软件,并在transcript命令行中cd到sim文件夹下;

2.在transcript命令行中source TCL_NAME.tcl #source tcl脚本文件;

3.在transcript命令行中输入 build ,用于编译所有的源文件;

4.在transcript命令行中输入rerun,启动波形仿真。

1372

1372

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?