关于Vivado和Modelsim联合仿真的爱恨情仇

心路历程

vivado自带仿真工具虽然可以使用,但是每一次修改代码后都会使用较长的时间才能重新仿真,时间太长真的接受不了。但是modelsim仿真是比较快的,所以建议使用modelsim进行仿真开发。虽然网上有很多关于vivado和modelsim联合仿真的文档,但是小编多次实验发现,简单的按照网上通用做法将两个软件做联合仿真老是出问题。有时候今天仿真好好的,第二天突然就不行了,或者换一个电脑,仿真就挂掉了。这种问题很影响工程进度。下面将自己的经验分享给大家。

版本对应

每一个版本的vivado都会有一个对应的modelsim版本与之对应,不然会出现错误,如果版本不对应可能无法解决错误。而且每一次仿真找问题都太麻烦了。具体vivado版本对应表可在技术手册ug973中查看,如下图所示:

在下载对应版本的modelsim后,按照网上通用做法生成vivado仿真编译库,在生成modelsim仿真编译库时,一定不能存在错误结果,不然会导致意想不到的结果。

仿真设置

将vivado的modelsim仿真设置好后,如果修改代码,就必须重新加载文件,可以直接run xxx.do文件,不必关闭modelsim。

具体操作方法:

1)使用notepad打开xxx_complie.do文件,去掉quit -force,这句会直接强制关闭modelsim;

2)回到xxx_simulate.do文件,在文件开头增加do xxx_complie.do代码。

3)在modelsim的transcript窗口输入do {xxx_simulate.do}就可以加载。

4)如果存在已经设置好的波形配置,进制显示,信号位置顺序等,可以将Wave(.do文件)界面保存下来,等到重新加载仿真后在打开.do文件。

补充:

关于modelsim和Vivado联合仿真实现后,ise 软件和modelsim的仿真不能用了的处理办法:

环境变量原因:

1) 破解license文件的环境变量:MGLS_LICENSE_FILE: …\LICENSE.TXT

2) Mmodelsim运行ini文件:MODELSIM: …\modelsim.ini

一般设置好这两个环境变量后,modelsim就可以正常启动了,如果点击ise或者vivado的仿真按钮后还是不能启动modelsim,就需要查看modelsim根目录下ini文件是否被程序修改,如果被修改了(一般是自动修改的),就将想要实现仿真的软件的library库中找到相应的modelsim.ini,直接替换掉modelsim根目录中的文件即可。如果是该程序前一天还可以仿真,第二天就突然不能仿真,就需要将vivado工程目录下的根目录中所有的日志文件删除,以及sim目录中的所有文件后,就可以了。

错误解决

1、在生成modelsim仿真编译库时,一定不能存在错误结果,不然会导致意想不到的结果。比如,我利用vivado生成编译库时有错误结果,导致加载modelsim时报错:dds 仿真IP核出错。

2、出现报错:[vsim-3363]

解决:忽略掉这种报错,在seting设置界面,simulation页的modelsim.simulate.vsim.more_options*选项填:-warning 3363。就可以忽略掉该条报错,使得仿真继续。

3. 2022年7月5日——出现联合仿真库不匹配的问题:在使用别人的工程进行仿真时,会遇到找不到相关库文件的情况,例如:vcom_1598/vcom_1136,报错,但是自己定义的仿真库和vivado是对应的,但就是会报错!如果删除前工程日志文件(…/xxx.jou,…/xxx.log)无效,替换modelsim.ini也无效时,可以直接简单粗暴的将生成的modelsim仿真库文件夹中的所有内容都复制到工程中就可以解决报错问题。(…/work.sim/sim_1/behav/modelsim/modelsim_lib/msim路径下)

4.2022年10月28日 ——报错:(vlog-7)filed to open design unit file…问题。解决办法是因为程序的文件目录名称太长了,建议将工程移到名称短的目录中。

5.2023年6月15日 ——报错:(vopt-19)Failed to access library 'modelsim_lib/msim…问题(就是找不到仿真的IP核库文件)。解决办法:我将modelsim的环境变量、库路径等都核对了,没有错。最后发现是库文件夹里面的modelsim.ini文件内部的路径是错误的,将对应正确的路径改为自己的就可以了。错误见下图:

修改位置如下:相当于将所有的不正确路径都要替换!

5.2023年11月3日 ——报错:

1)未知名的错误,点击仿真按钮,不能进入modelsim界面就报错,提示某个文件路径很深,提示error:(vlog-7)failed to open design unit file…in read mode,故将对应文件的被使用环境都去掉,如下图所示:

将该文件的使用环境选项都去掉。

2)执行完上一步还是不行,现在可以打开modelsim了,但是报错:note mult pps a b extra_b……。在modelsim的tcl命令行没有发现错误提示,直接了当说是不能加载…simulate.do文件第9行,像这种报错不好排查,故又往上翻了好多行tcl命令行提示,终于找到错误提示,说是某个文件端口找不到。排查后发现是两个大模块中有两个文件是不同功能但是模块名称相同,导致端口找不到出错。修改端口名称后可以正常仿真。

后续还会持续更新错误解决办法!!

关于使用modelsim查看状态转移图

在程序设计时,有时候需要查看我们编写的程序状态转移图,以便直观的查看对应状态跳转,而vivado又不支持该功能,那么既然选择了modelsim进行仿真,顺便使用其状态转移图又何乐不为呢。

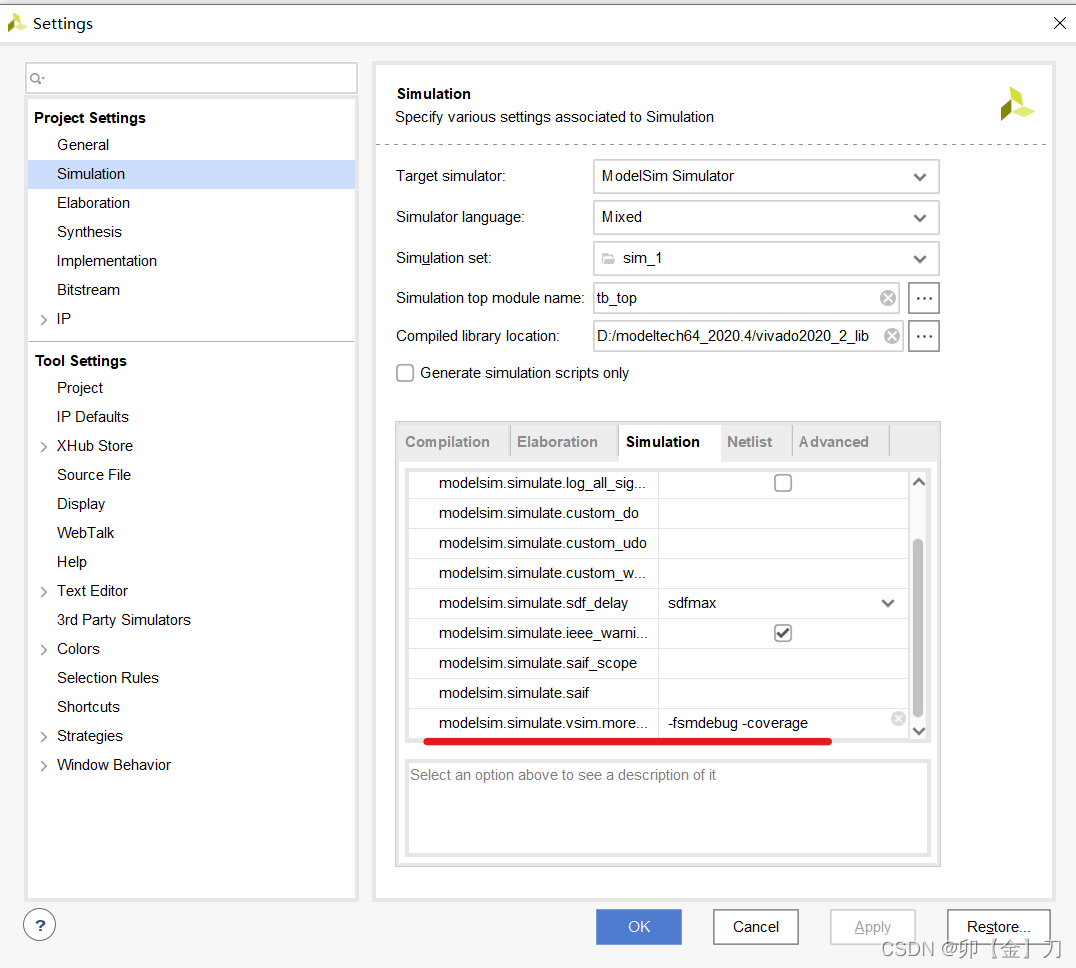

- 在seting设置界面,进入到simulation选项卡,在simulation页面下,在modelsim.simulation.vsim.more_options选项填入“-coverage -fsmdebug”即可。如下如:

- 在modelsim仿真软件中打开FSM界面,即可查看到对应的状态转移图。

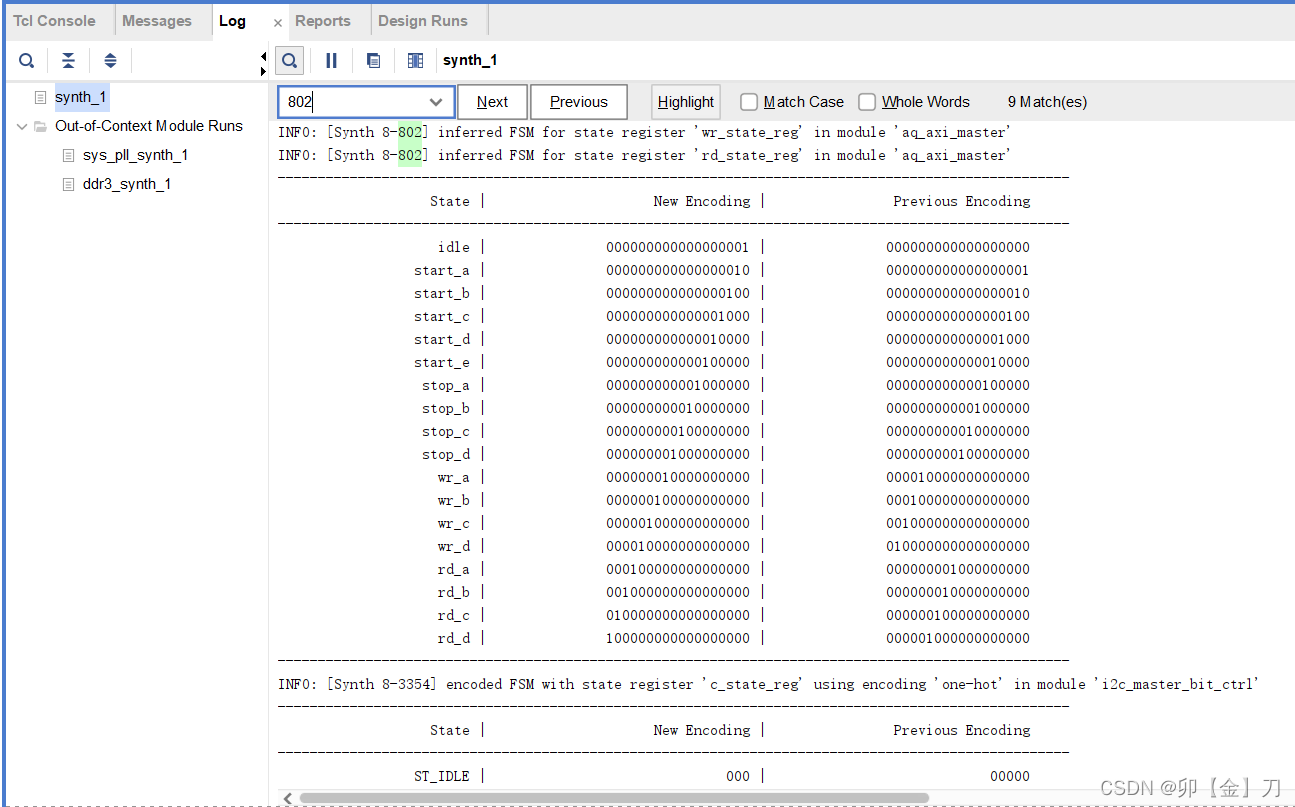

既然说到状态机,在vivado中,可以查看状态机实际综合出的编码方式,以及你编写的状态机是否被EDA软件识别为状态机。具体查看方法是,在综合完之后,在vivado的log界面,搜索:3354、802、fsm、state等关键字就可找到对应的状态机实现说明。如下图:

7400

7400

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?