DRAM有很多的IDD,分别是什么,具体代表何种含义,具体又有什么作用呢。

本文以DDR5的IDD定义当作参考:特注:所有以下IDD,都有同等的IDDQ跟IPP。意义相同,只是吃电流的power source不同

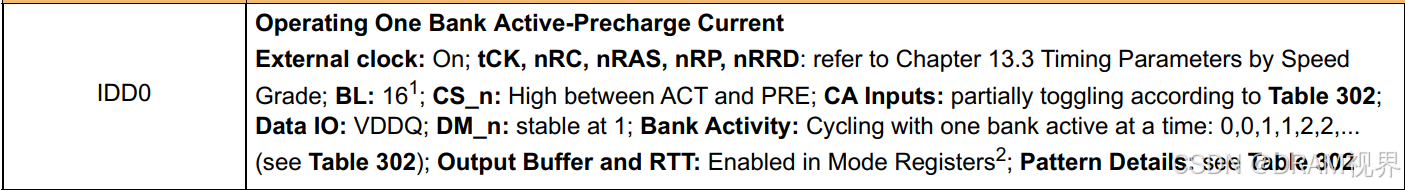

IDD0: ACT+PRE Current

IDD0基本代表着打开跟关闭wordline的电流消耗。用它来评估wordline打开跟关闭是否正常

IDD2N: Prechange Standby Current

IDD2N基本代表DRAM idle时候的电流消耗,此时DRAM未进入任何mode,只是处于idle. tCK仍在跑,DQ/CA等input buffer keep打开。

基本用来评估静态功耗的。这部分基本由两部分组成,一个是device本身的leakage,一个是电路里面的设计部分对一些idle的时候有没有做特殊的gating处理

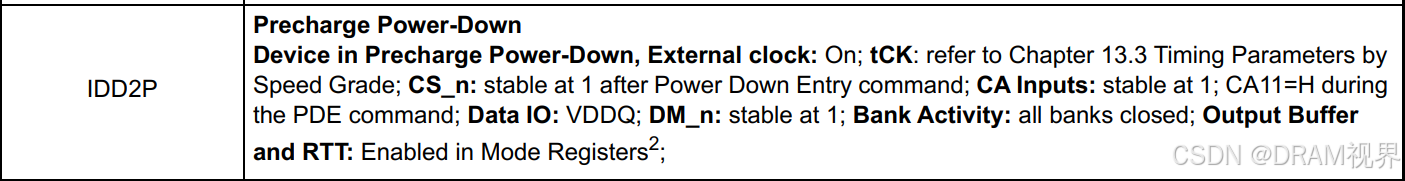

IDD2P:Precharge Power-Down mode Current

所谓precharge powerdown mode,也就是wordline没有打开,所有bank处于idle的时候进入的powerdown mode.这个时候的power,基本有一部分是可以断电跟clock gating了。这部分如果不同厂家有差别,只能说是内部电路处理上的差异。特别是IDD2N跟IDD2P的差值

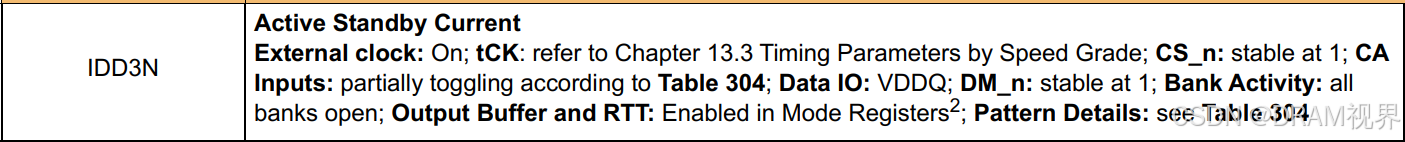

IDD3N: Active Standby Current

所谓active standy,是针对IDD2N的precharge standby 而言的。所谓precharge standby,就是值得bank idle, 那么active standby指的是bank不idle,bank的wordline有被打开,打开之后的电流消耗,这部分其实就是为了评估打开wordline的过程对电流的消耗部分

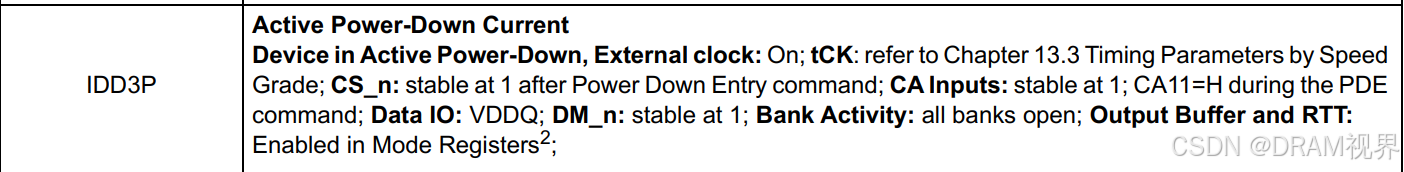

IDD3P: Active Powerdown Current

顾名思义,就是active了wordline之后进入powerdown mode,这种操作是被允许的,只要别在powerdown里面呆的时间太长,导致long-tRAS时间不满足就行。tRAS时间太长了,wordline的电位可能会慢慢衰减,导致潜在的data丢失风险。

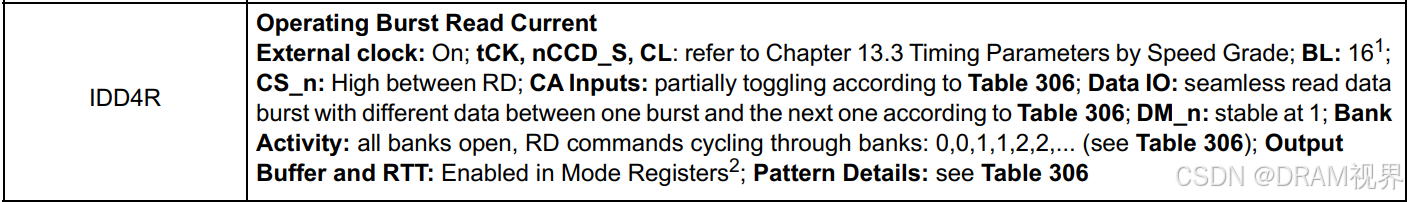

IDD4R/IDD4W: burst read/write Current

这个地方的测试pattern是seamless write/read,用来模拟最busy的情况下,DQ连续翻转的case下的电流消耗

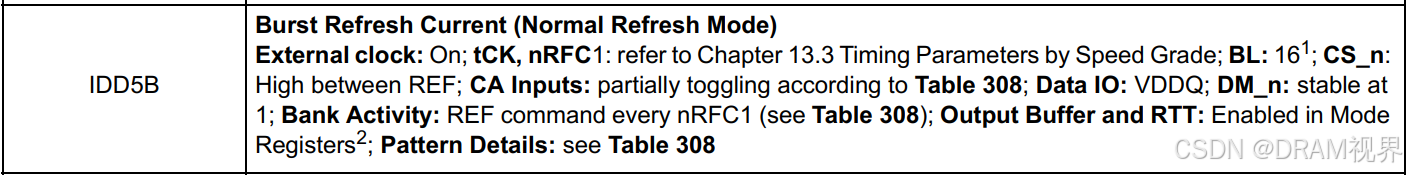

IDD5B: Burst Refresh Current

严格意义来讲,这种pattern sequence是不满足spec要求的。spec要求最多只能连续8笔REF command可以以tRFC的时间间隔来发送。但是IDD5B的sequence,是一直以tRFC的间隔来发送REF command.这个是一个很worse的condition来评估refresh带来的功耗。但是也能间接的来看refresh带来的潜在的电流消耗可能存在的风险。

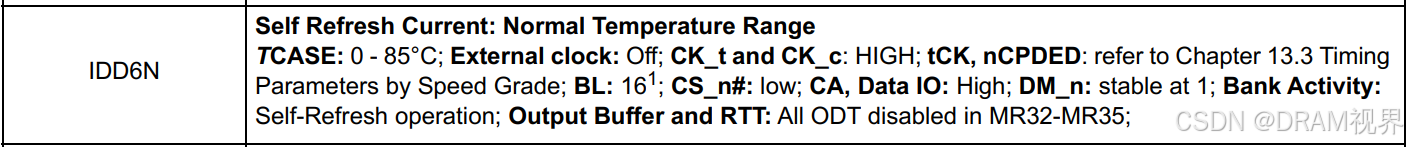

IDD6N:self-refresh current

之前的文章介绍过了。一种低功耗模式下的电流消耗。这部分的电流消耗基本是内部refresh操作带来的。不信你看,外部的clock都off了。

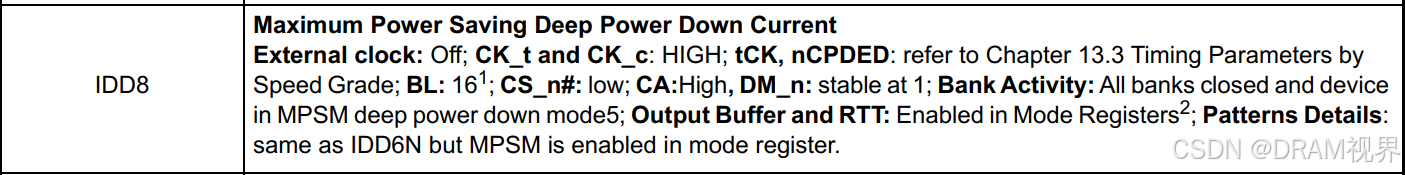

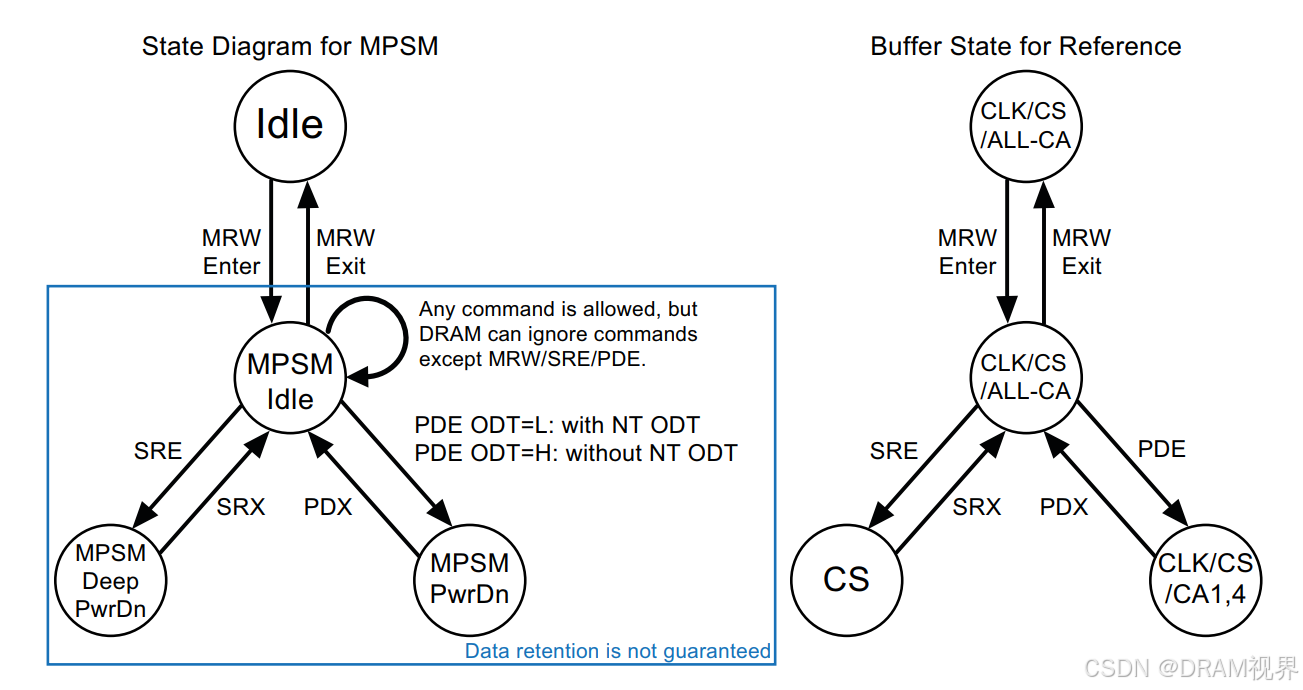

IDD8: MPSM Deep Powerdown Current

其实这个MPSM mode总感觉很鸡肋。不过DDR5在DDR4的基础上做了完善。鸡肋的原因是MPSM断电断的太多,又不能保证retention,退出又太麻烦,时间太长。频繁进出不划算,不频繁进出又有retention风险。

不过DDR5进行了完善,可以在MPSM里面进入Powerdown或者SR.目前不确定真实系统有多少会考虑MPSM,截至目前,不太有了解到有系统会采用这个feature

一般通过IDD来做分析的时候,会结合IDD/IDDQ来做,并对不同的IDD的分类做加减combine来得到更多的信息。在DDR5上,DIMM上引入了PMIC,所以IDD的潜在的constrain是PMIC是否能扛得住。有时候的过载会触发PMIC的保护预警机制,或者PMIC的response无法抗住太大的power loading,这些潜在的风险也会导致问题极度难以debug跟分析。DRAM的IDD是各家的竞争力的重要参数,对于服务器,功耗太大会导致风扇的问题,还有电费的问题,对于消费类电子,直接影响到续航能力。

135

135

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?