目录

引言

最近在比较不同的工艺之间的差别,主要研究了下TSMC 12nm的库文件。

由于比较care power,做了一轮power opt(vt swap)。但vt swap之后,power除了leakage下降了点,switching和internal反而还上升了点。仔细查了log,cell确实换了,vt type没换,只是沟道宽度从16 nm变成了24 nm。这是一个很违反直觉的结果,于是展开研究了一下。

1. TSMC 12/16 nm

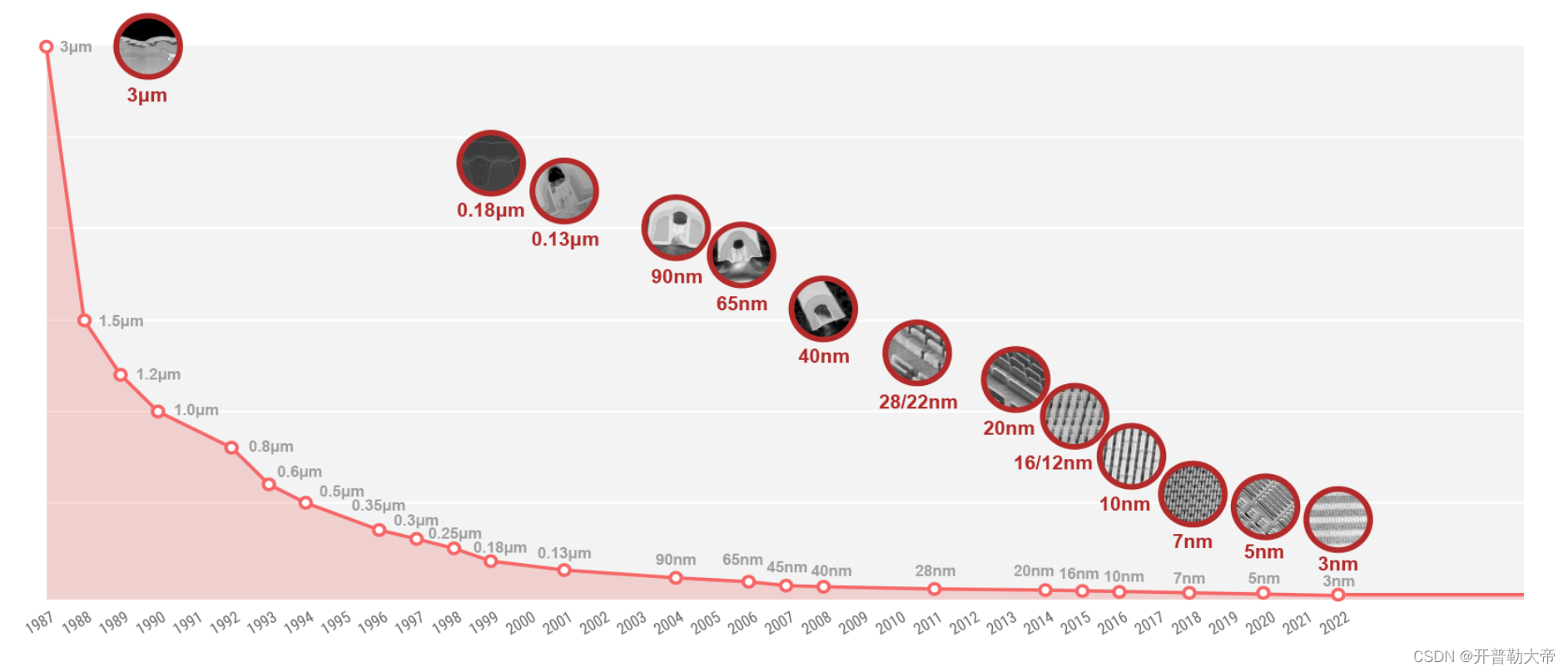

在工艺节点小于28 nm后,这些foundary纷纷不讲武德,仿佛工艺后面的数字只是一个代号跟实际器件的沟道宽度没什么关系。更有甚者,intel的10 nm工艺直接被叫成intel7。敢情是14 nm+++++被喊怕了,要赶超友商就直接跳过了10这个代号。当然,也不得不承认,intel7确实有着能打TSMC7的实力(个人观点,仅从消费者角度看intel和AMD的CPU对比)。

TSMC 12nm库可简单的从track上分一下组,分别是6T, 6T_Turbo (12T), 7.5T, 9T。从沟道宽度上来划分是16、20和24 nm(是的,你没有看错,似乎跟12 nm没有半毛钱关系)。这里,我们讨论的是CPD库(CPODE,Continuous Poly on Diffusion Edge),非CPD不在讨论范围内。

| REF_NAME | SIZE X | SIZE Y | X | Y |

|---|---|---|---|---|

| BUFFD0BWP16P90LVT | 0.360 | 0.576 | - | - |

| BUFFD0BWP16P90CPDLVT | 0.270 | 0.576 | 75.00% | 100.00% |

| BUFFD10BWP16P90LVT | 1.350 | 0.576 | - | - |

| BUFFD10BWP16P90CPDLVT | 1.440 | 0.576 | 93.75% | 100.00% |

现在应该不难理解为啥TSMC12/16nm联系紧密了,因为部分Cell的X尺寸上,通过CPD技术成功的降至了16nm的75%,那么使用该技术的Cell能做出16 nm*75%的密度,即12 nm。当然并非所有的Cell都是能达到75%这么好的效果,这就跟为啥库文件不仅有16 nm,还有20和24nm一样。亮肌肉当然选最好的命名,(看把intel都吓得10 nm改成Intel7了,二次嘲讽)。以上纯属个人见解。

2. Abnormal Result

首先简单介绍下项目的VT情况,全程禁用LVT,仅长tree使用LVT,因此98%的Cell为SVT。VT Swap后,有约70%的Cell从GateLength 16nm被换成了24nm。

本Design的VT Swap方向和Leakage OPT,如下代码所示。

set vt_priority { \

BWP6T24P96CPD BWP6T20P96CPD BWP6T16P96CPD \

BWP6T24P96CPDLVT BWP6T20P96CPDLVT BWP6T16P96CPDLVT \

BWP6T24P96CPDULVT BWP6T20P96CPDULVT BWP6T16P96CPDULVT \

}

fix_eco_power -verbose

-power_mode leakage

-pba_mode path

-pattern_priority $vt_priority

-cell_type {sequential combinational}

-setup_margin 0.02

-start_end_type reg_to_reg

-methods size_cell

接下来展示结果(TT25):

| Stage | Leakage | Internal | Switching | Total |

|---|---|---|---|---|

| before vtswap | 0.0012 | 0.1374 | 0.1078 | 0.2464 |

| after vtswap | 0.0011 | 0.1394 | 0.1095 | 0.25 |

| Ratio | 91.67% | 101.46% | 101.58% | 101.46% |

是不是很神奇这就真的是Leakage优化,其他两个都变差了。

带着疑问和不解,我问了资深的工程师。让我先看看单颗cell的power情况,然后可能还要查表。

3. Single Cell Power Analyze

和常规报power一样,要先把一些setting给set上。

set power_enable_analysis true

set power_default_toggle_rate 0.1

set power_default_static_probability 0.5

set power_clock_network_include_register_clock_pin_power false

reset_switching_activity

set_switching_activity -static_probability 0.5 -toggle_rate 0.1 -type registers -base_clock "*" -hierarchy

set_switching_activity -static_probability 0.5 -toggle_rate 0.1 -type clock_gating_cells -base_clock "*" -hierarchy

set_switching_activity -static_probability 0.5 -toggle_rate 0.1 -type black_boxes -base_clock "*" -hierarchy

set_switching_activity -static_probability 0.5 -toggle_rate 0.1 -type memory -base_clock "*" -hierarchy

set_switching_activity -toggle_rate 0.1 -clock_domains * [all_inputs]

之后,我们选好instance,对单颗instance进行分析。

report_power {your_instance_name} -cell_power

结果大概长这样(TT25):

加点手法整理一下(TT25):

| Stage | ref_name | Input Trans | Output Load | Internal | Switching | Leakage | Total |

|---|---|---|---|---|---|---|---|

| before vt_swap | BUFFD1BWP6T16P96CPD | 0.06118306 | 0.01255221 | 3.10E-09 | 2.96E-08 | 2.76E-11 | 3.27E-08 |

| after vt_swap | BUFFD1BWP6T24P96CPD | 0.07119579 | 0.01305465 | 3.26E-09 | 3.08E-08 | 1.08E-11 | 3.41E-08 |

| Ratio | / | 116.37% | 104.00% | 105.03% | 104.16% | 39.28% | 104.19% |

不难看出以下变化:

- Trans和Load均变大。通过through这个instance的timing path分析得知,该insts前面的cell也有很多从16换到了24,应该与这个有关。

- Leakage得到了有效的降低,但Internal和Switching却有略微增大。然而,观察具体数值来看,虽然Leakage降低了60%+,但是对比其他两者小了2-3个数量级,因此在Total上power有略微增加。

很好,第二点变化十分符合宏观规律(2. Abnormal Result),那么我们现在只需要验证不同沟道宽度的同类型Cell的pin cap关系即可。

当发现report_timing显示的有效位数不够用时,可以加上option: (-signi 8)。这样数字的小数点就能精确至八位。

4. Library Verify

为了弄清楚,沟道宽度对pin cap的影响,直接查找了BUFFD1BWP6T…P96CPD所在的TT25下的lib:

加点手法,直观感受下:

| Channel Width (nm) | Capacitance@TT25 (pf) | Ratio |

|---|---|---|

| 16 | 3.8662E-04 | 100.00% |

| 20 | 3.9926E-04 | 103.27% |

| 24 | 4.2019E-04 | 108.68% |

根据power basic的知识,同一VT下,我们有以下规律:

- Leakage与cell的沟道宽度成负相关趋势;

- toggle_rate一定时,Switching(F·C·V2)与cap值成正比;

- Internal(V·ISC)跟input transition成正相关。

因此,结合条件分析,从更16 nm换成24 nm后,Leakage减小,而Switching和Internal均会增大。这个规律适用于我们找的这个BUFF例子,也与我们整个Design的宏观规律一致。

后续验证了Samsung的S8工艺,与本文得出的结论是一致的。

结论

- 在做VT Swap时,VT的更换顺序(越往前优先级越高):SVT,LVT,ULVT;如果十分Care Leakage,则Gate Length的更换顺序:24,20,16。

- 特别地,如果一颗Cell,从BWP6T16P96CPDLVT更换至BWP6T24P96CPD,则Leakage会获得最大的收益;从BWP6T16P96CPDLVT更换至BWP6T16P96CPD,则Dynamic会获得最大收益。

- 同一Cell Type,同一条件下,沟道宽度越大,Leakage越小,而Switching和Internal都会变大。因此,做完Leakage OPT后,Total Power不一定更好。

以上结论仅供参考,具体由Design决定。

536

536

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?