1、简介

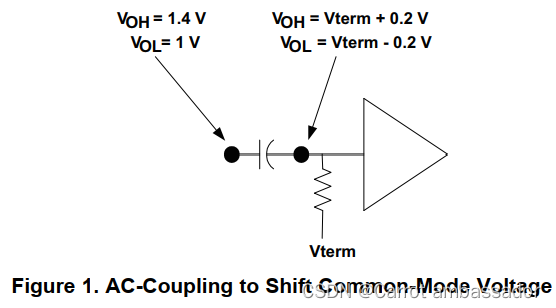

AC耦合是用来改变链路上收发端共模电压的一种耦合方式。如下图,输出信号在经过交流耦合电容之后,直流分量无法通过,就只剩交流分量,再再接收端加上需要的直流偏置,部分芯片内部已经集成了偏置电路。

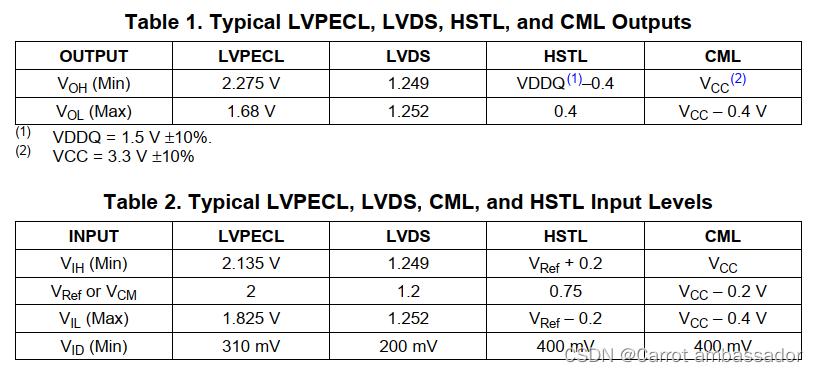

常见的高速接口收发端电平标准如下表。

2、LVPECL

2.1 LVPECL-LVPECL

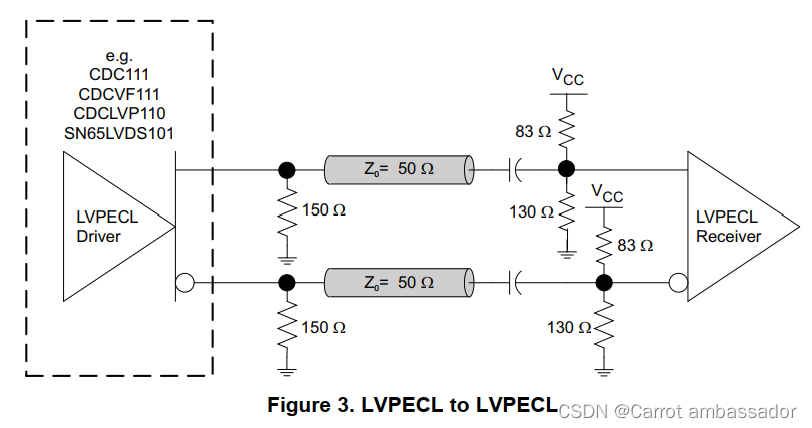

下图为LVPECL收发的AC耦合方式,发送端150Ω(140-220Ω之间,看芯片推荐值)的下拉电阻是为了给发直流电流提供路径(需要从LVPECL发送端的结构分析);接收端的上下拉电阻的其中一个目的是阻抗匹配(50Ω),另一个是为了分压为接收信号提供2V的直流偏置,接收端的电阻一般都是已经集成好的了,正常设计中只需要加发送端的下拉电阻和交流耦合电容就可以了,正常电容值为10nF。

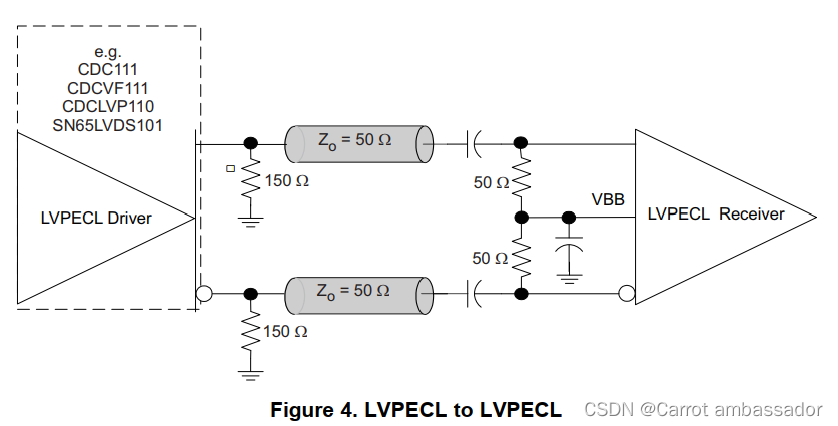

如下图的设计方式也很常见,发送端与上面一致,接收端用带电容的端接,主要作用是为了消除共模噪声,VBB由接收器提供。

2.2 LVPECL-LVDS

如下图为LVPECL发送LVDS接收的设计方式。发送端下拉电阻作用和阻值与前面一致。接收端的100Ω耦合电阻是为了给LVDS接收器提供足够的摆幅(350mV),对于内部已经集成了的就不用了,但是通常需要加10k的上下拉,提供1.65V的直流偏置,。

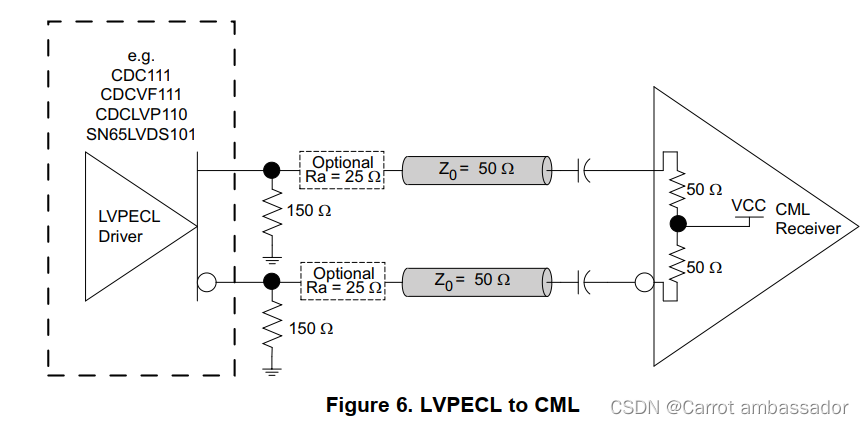

2.3 LVPECL-CML

如下图为LVPECL 发送CML接收。发送端下拉电阻与前面一致,需要注意的是当LVPECL超出CML接收器的承受范围时需要增加Ra电阻衰减LVPECL输出(如LVPECL摆幅为750mV,但是CML的摆幅为400mV)。

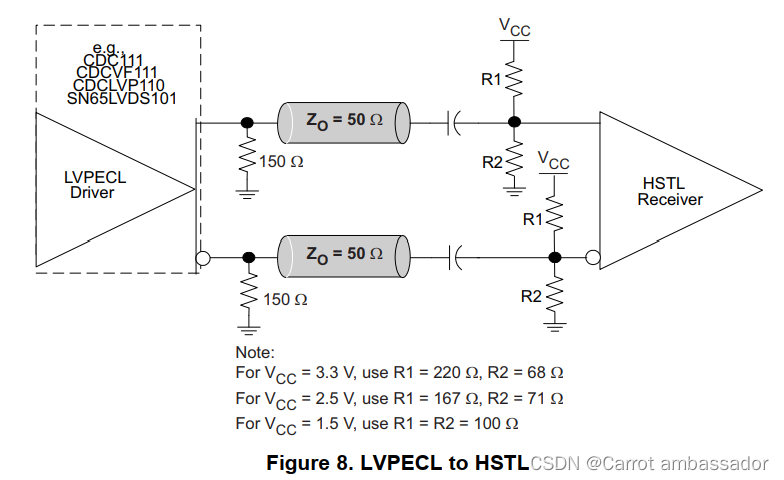

2.4 LVPECL-HSTL

如下图为LVPECL 发送HSTL接收。发送端下拉电阻与前面一致,接收端上下拉电阻其中一个作用是提供50Ω的端接,另外为HSTL接收器提供直流偏置电压(0.75V)。

3、LVDS

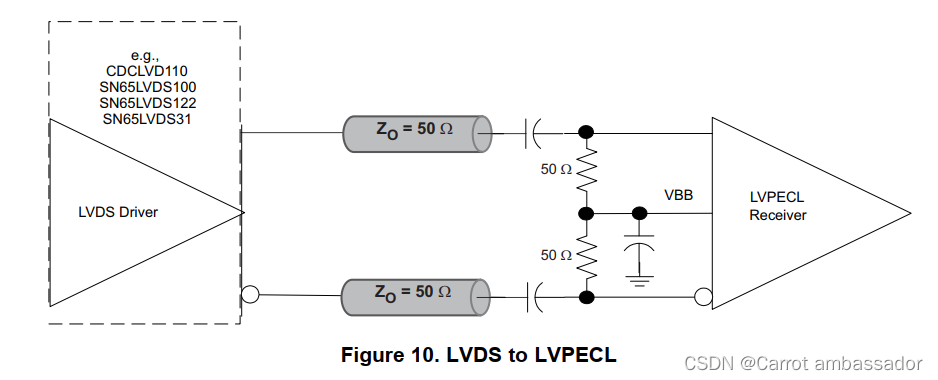

3.1 LVDS-LVPECL

如下图为LVDS 发送LVPECL接收。由于发送和接收端的电平不匹配,因此需要增加偏置电压,但是如果芯片支持VPECL接收,一般内部都集成了。

、 如下图的连接方式同上面的一致,都是为了消除共模干扰。

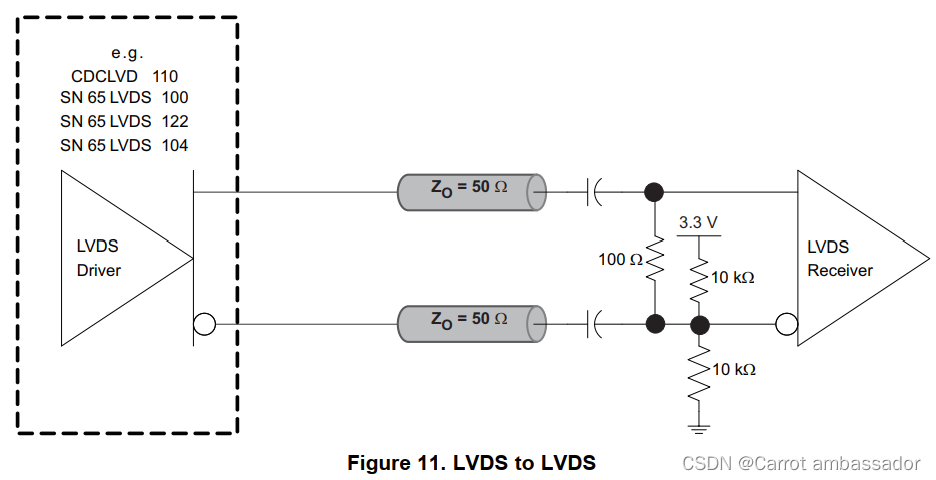

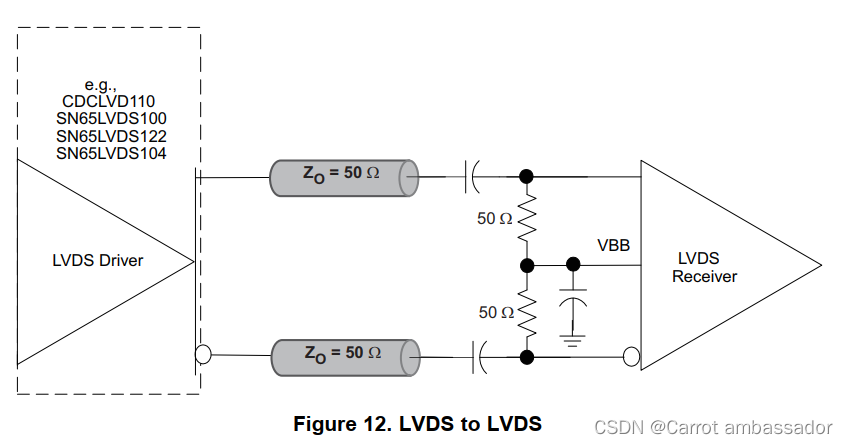

3.2LVDS-LVDS

LVDS接收时尤其要注意接收器内部是否集成100Ω的端接电阻,没有必须加上,已经集成了则不能加。

如下图的设计方式是为了消除共模干扰。

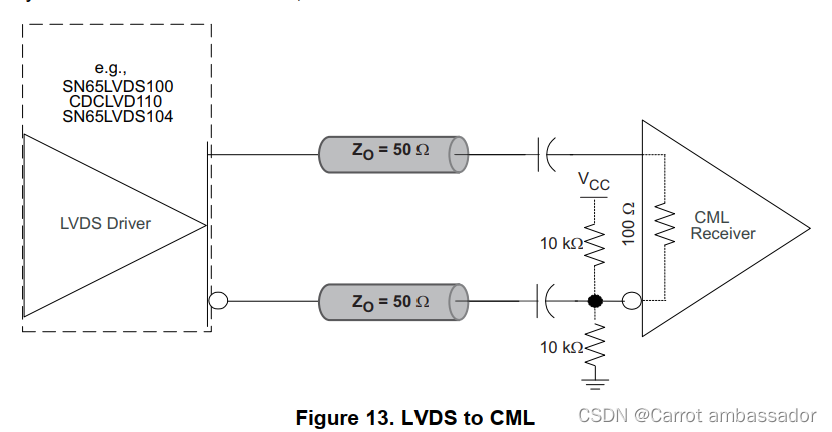

3.3LVDS-CML

对于CML接收器,很多内部都已经集成了100Ω的端接电阻

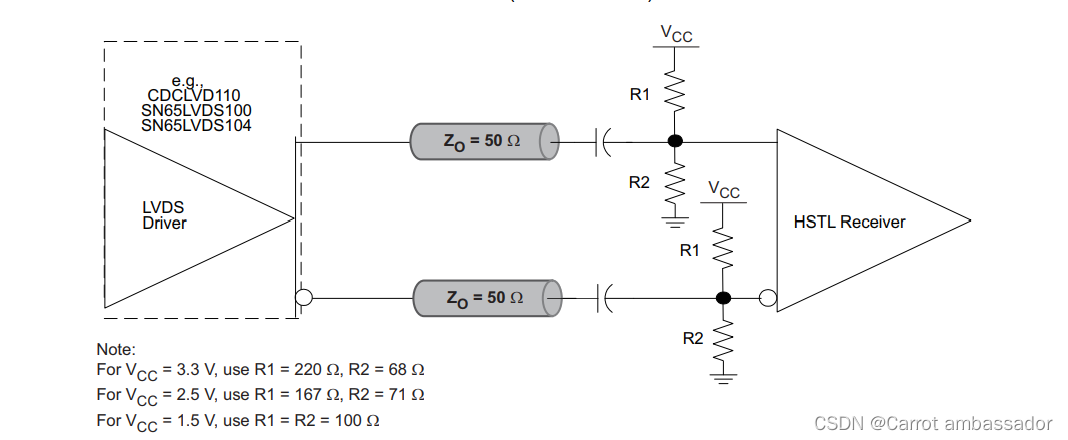

3.4 LVDS-HSTL

HSTL接收同2.4中一样,需要提供0.75V的直流偏置。

4、CML

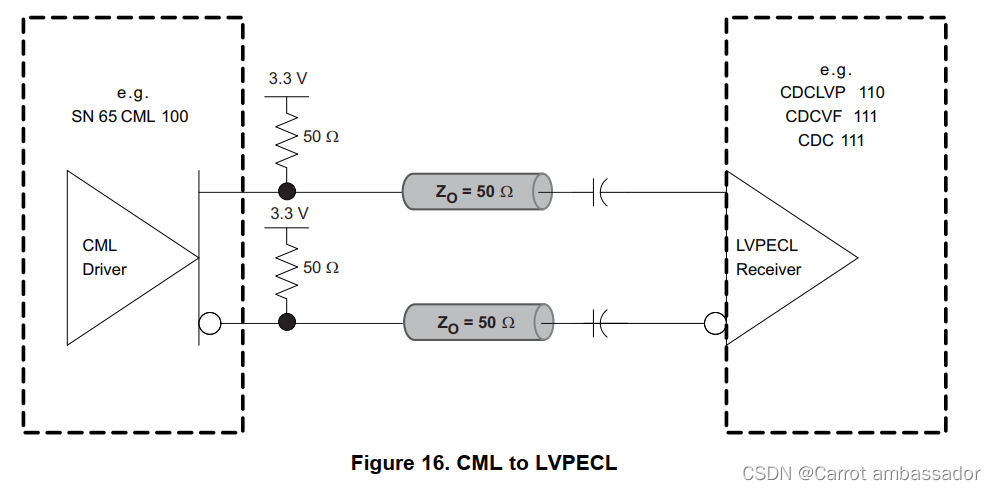

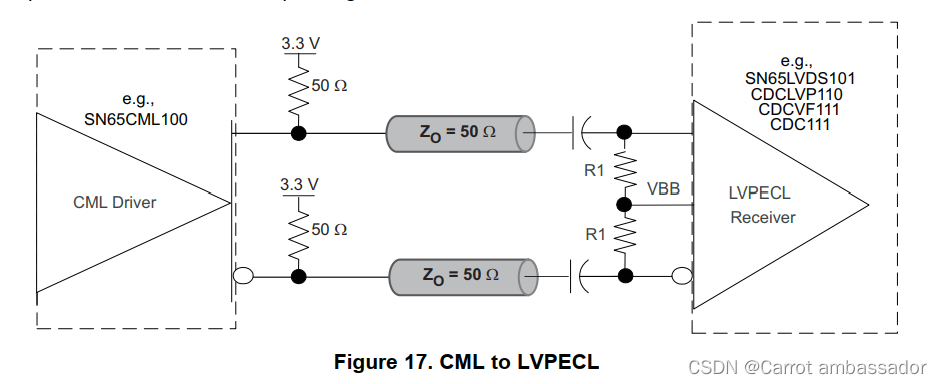

4.1 CML-LVPECL

下图为CML发送LVPECL接收。接收端默认内部集成了直流偏置,发送端提供50Ω的上拉端接阻抗匹配,另外需要由于发送器的结构需要提供源(内部集成就不需要了,多数情况链路上串两个交流耦合电容就行)。

下图为减少共模干扰的方式。

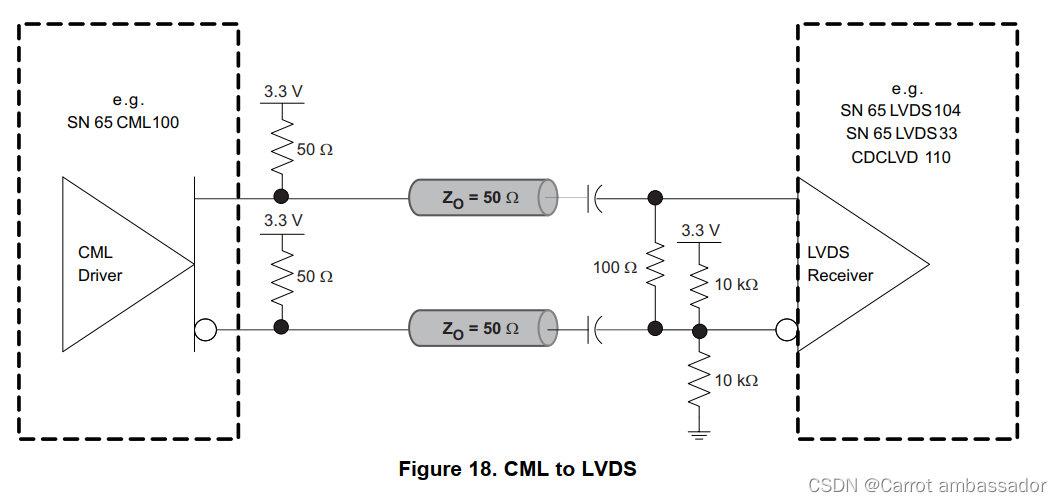

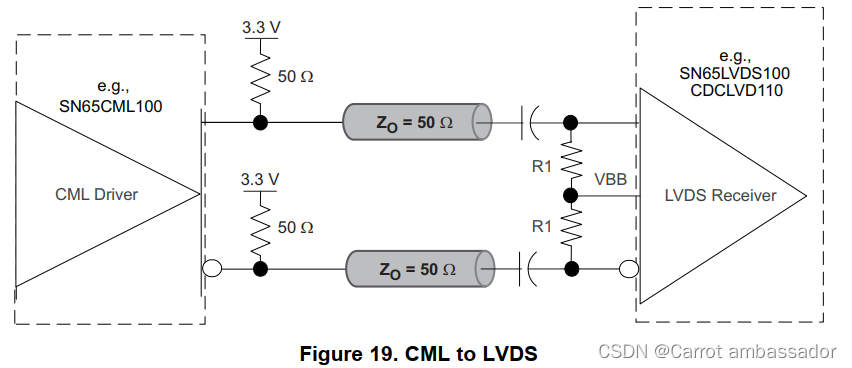

4.2CML-LVDS

LVDS接收,需要加100Ω的端接。

下图为减少共模干扰的方式。

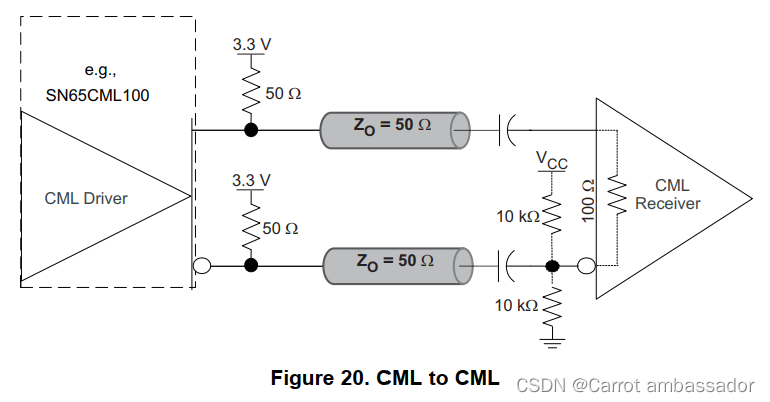

4.3CML-CML

下图为CML发送CML接收,现在收发器多数只需要加交流耦合电容就行。

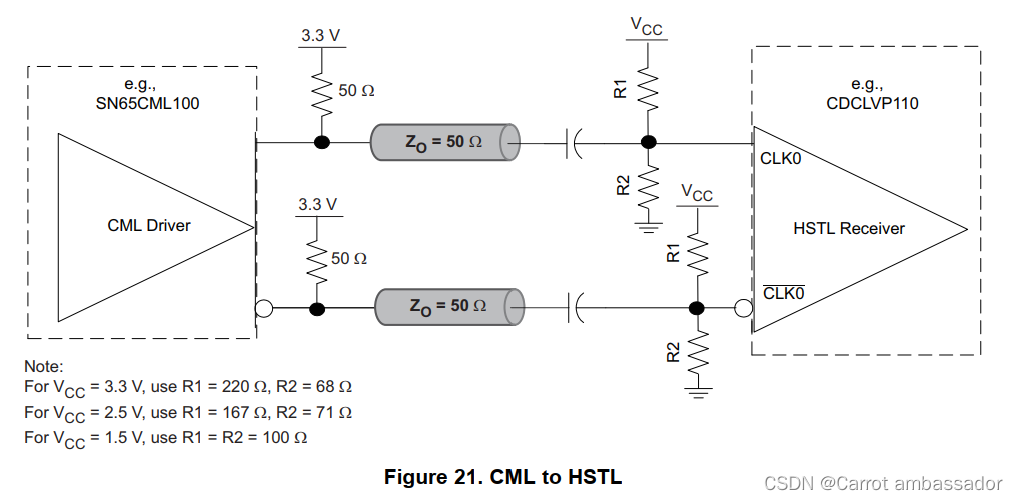

4.4CML-HSTL

下图为CML发送HSTL接收,接收端的直流偏置需要。

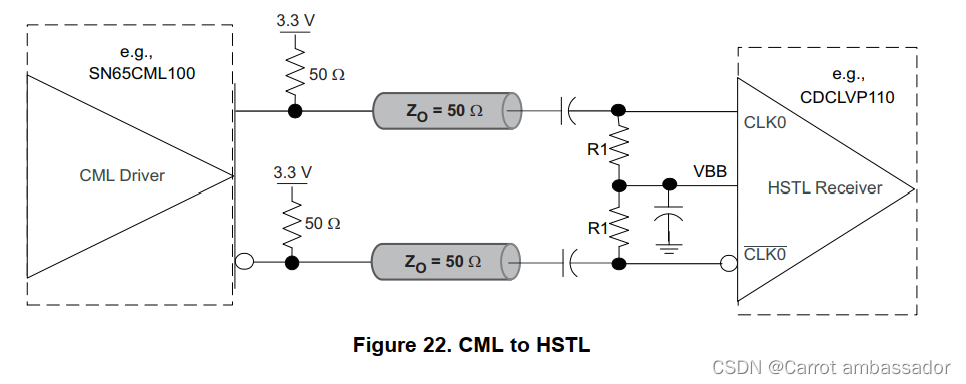

下图为减少共模干扰的方式。

5、HSTL

5.1HSTL-LVPECL

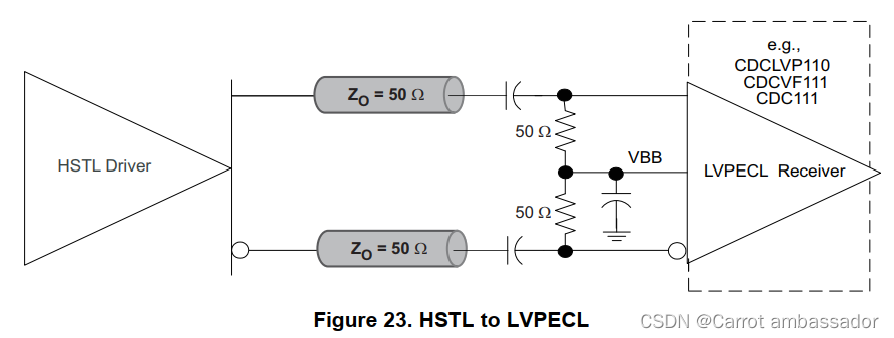

下图为HSTL发送LVPECL接收,接收端偏置电压由接收器提供。

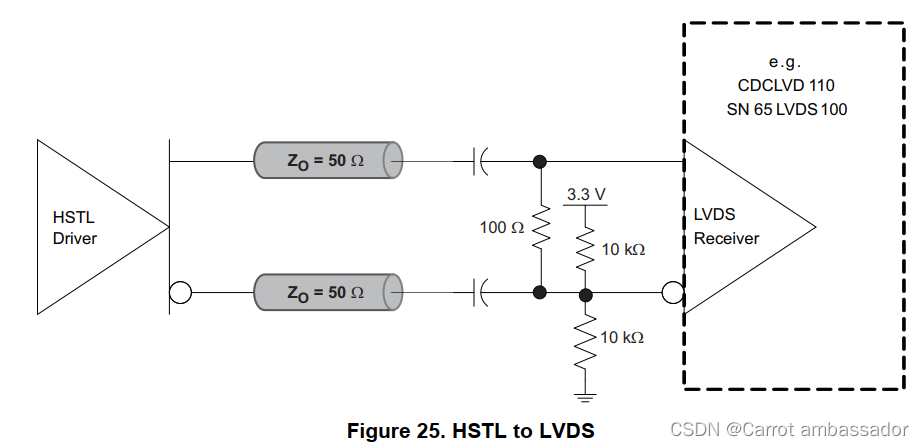

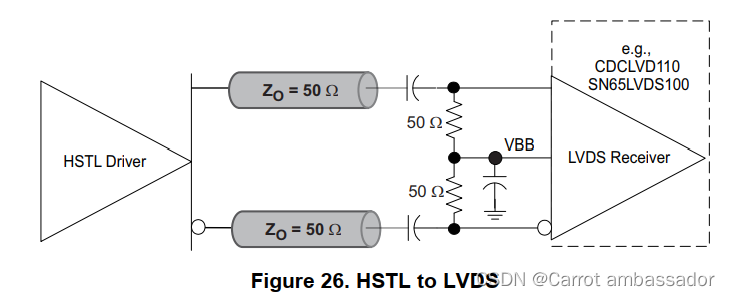

5.2HSTL-LVDS

下图为HSTL发送LVDS接收,接收端没有集成100Ω端接,需要外加。

下图为减少共模干扰的设计方式。

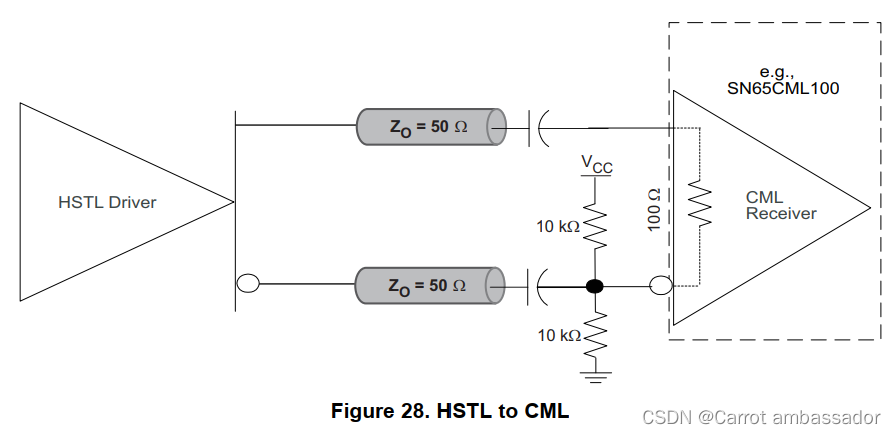

5.3HSTL-CML

下图为HSTL发送CML接收,接收端集成100Ω端接。

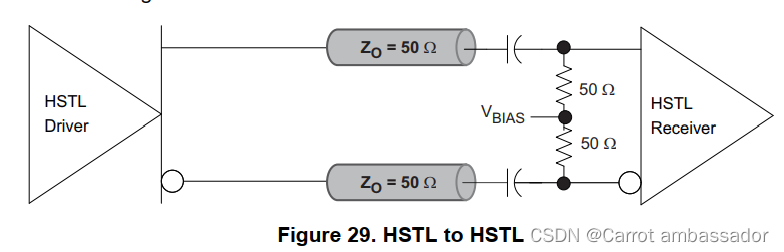

5.4HSTL-HSTL

下图为HSTL发送HSTL接收,需要提供直流偏置和端接。

--内容来源于TI

交流耦合看《AC-Coupling Between Differential LVPECL, LVDS, HSTL,CML》

直流耦合看《DC-Coupling Between Differential LVPECL, LVDS, HSTL, and CML》

2177

2177

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?