本节以设计和封装功能类似74LS161和74LS00的IP核为例,介绍基于Vivado的IP核封装流程。

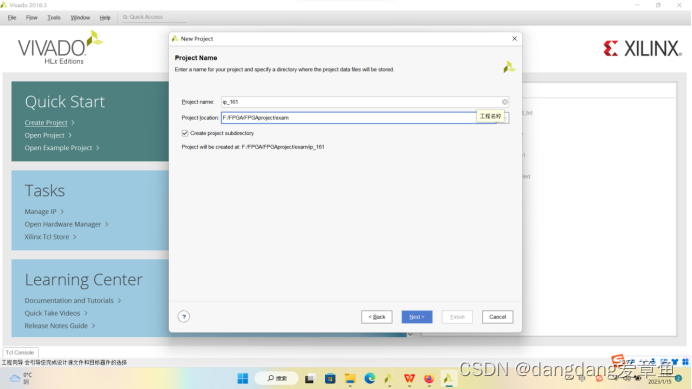

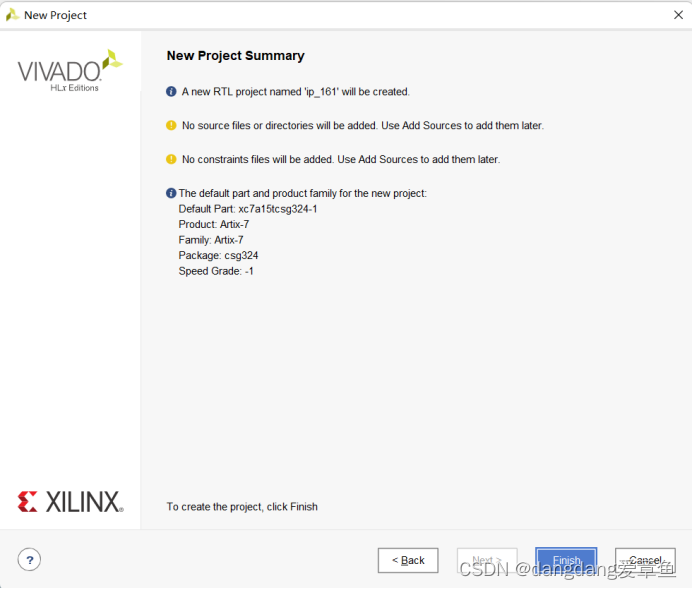

(1)创建工程

与流水灯设计一样创建,打开Vivado2018.3,单击Quick Start栏中的Create Project。启动工程向导,创建一个新工程,将其命名为ip_161,存于F:\FPGA\FPGAproject\exam文件夹下;

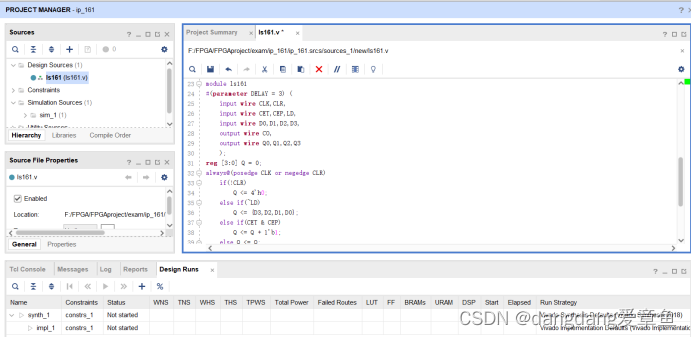

(2)设计源代码

74ls161源代码:

module ls161

#(parameter DELAY = 3) (

input wire CLK,CLR,

input wire CET,CEP,LD,

input wire D0,D1,D2,D3,

output wire CO,

output wire Q0,Q1,Q2,Q3

);

reg [3:0] Q = 0;

always@(posedge CLK or negedge CLR)

if(!CLR)

Q <= 4'h0;

else if(~LD)

Q <= {D3,D2,D1,D0};

else if(CET & CEP)

Q <= Q + 1'b1;

else Q <= Q;

assign #DELAY Q0 = Q[0];

assign #DELAY Q1 = Q[1];

assign #DELAY Q2 = Q[2];

assign #DELAY Q3 = Q[3];

assign CO = ((Q == 4'b1111)&&(CET == 1'b1)) ? 1 : 0;

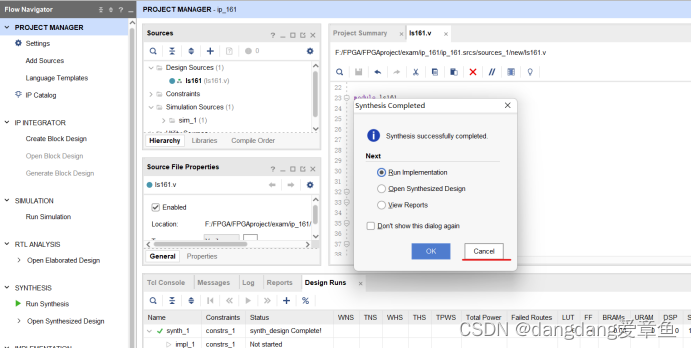

endmodule然后对当前工程进行综合,在弹出的Synthesis Completed对话框中单击Cancel按钮,表示不再继续进行后续操作。

(3)创建IP核

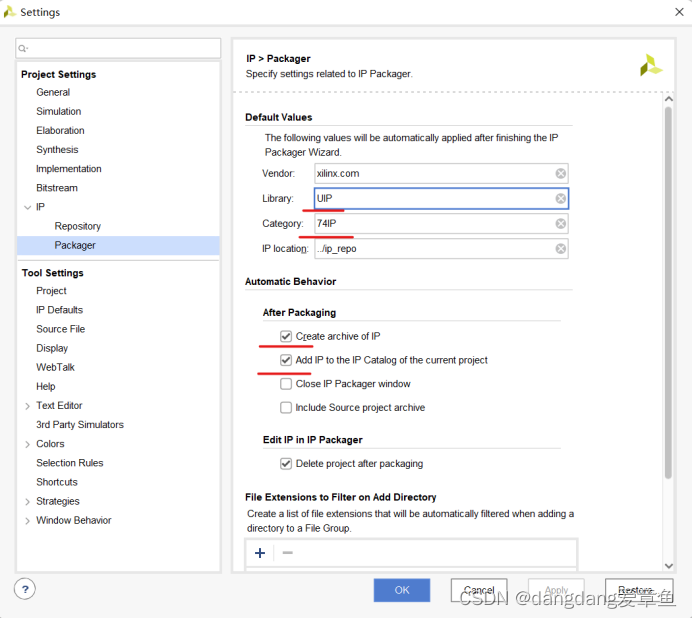

1)在Flow Navigator栏中的Project Manager下单击Settings,弹出的Settings对话框,在窗口左侧选择IP下面的Packager,在标签页中定义IP核的库名和目录。

此处Library(库名)处填写UIP;Category处填写74IP,勾选下面前两项,其他默认。点击Apply,再点击OK。

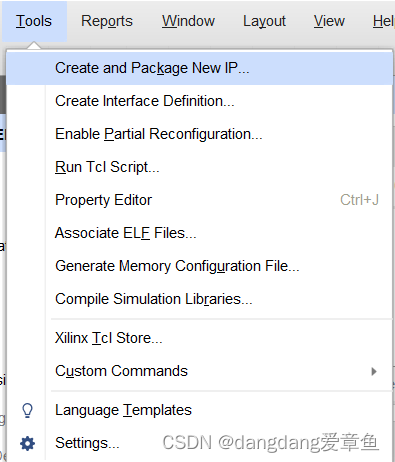

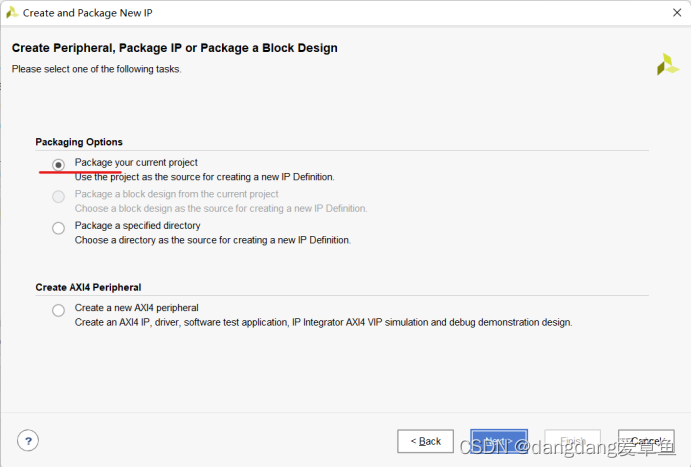

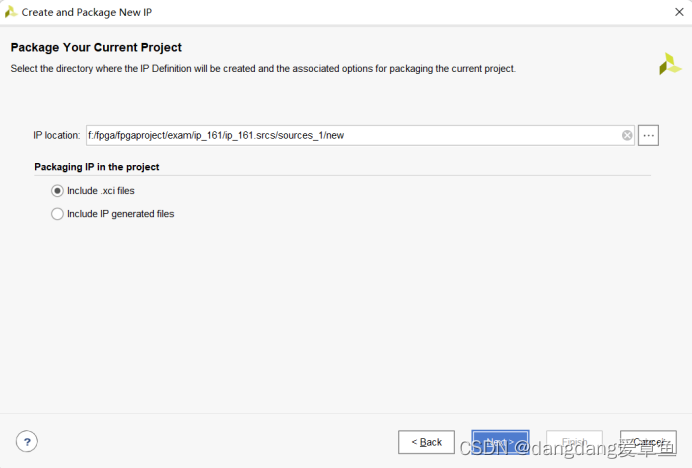

2)在Vivado主界面中选择菜单Tools中的Create and Package New IP,启动创建和封装IP的过程;按照下面的步骤进行IP核的创建。

(4)封装IP核

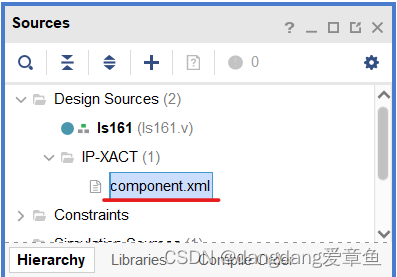

1)完成IP核的创建后,出现了一个xml文件,其中保存了封装IP核的信息;

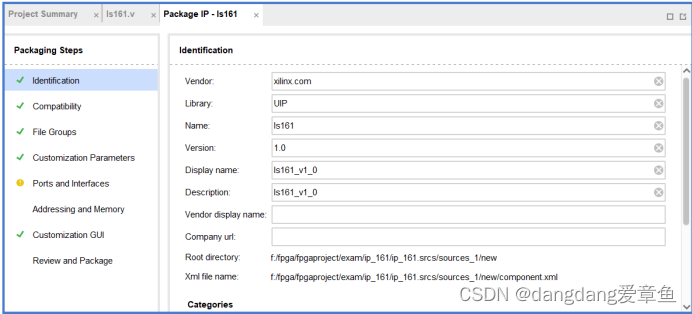

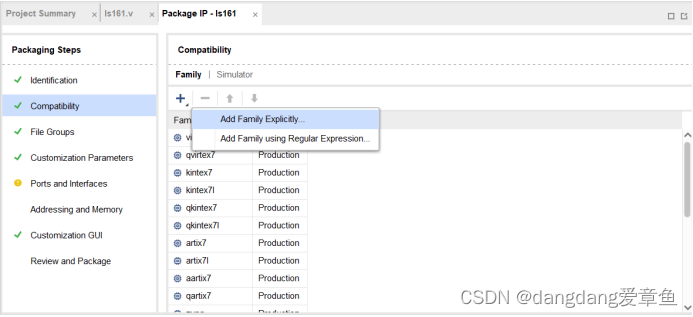

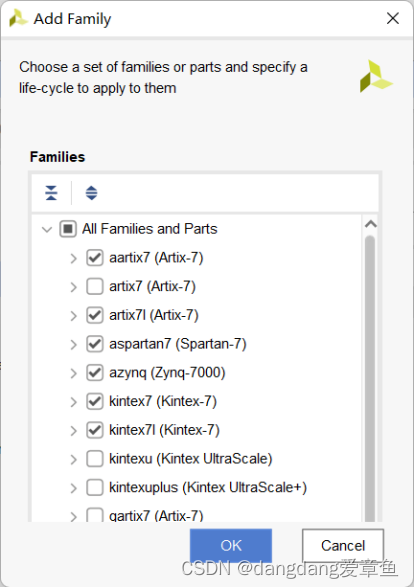

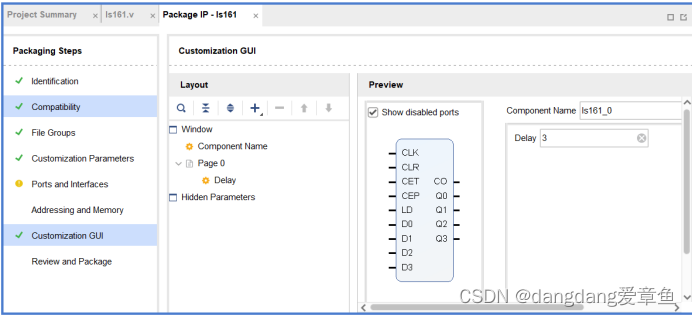

2)在Flow Navigator栏中的Project Manager下单击Package IP按钮,单击Identification可以查看并修改IP核相关信息,Compatibility页面显示了IP核支持的FPGA系列,可以继续添加IP核支持的器件,勾选如图artix7的其他器件系列,单击OK;单击Customization GUI可以预览IP核的信号接口。

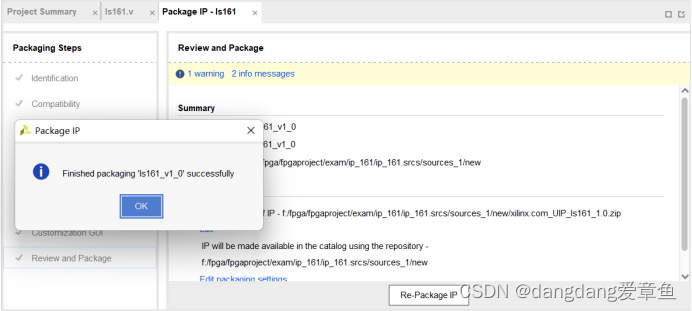

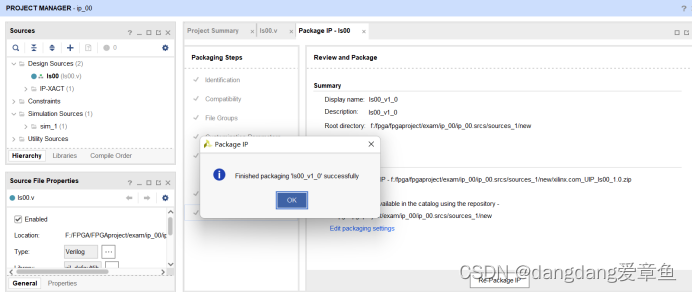

3)点击Review and Package页面可以查看IP核最终信息,确认无误后点击下方的Package IP按钮,完成ls161的封装。

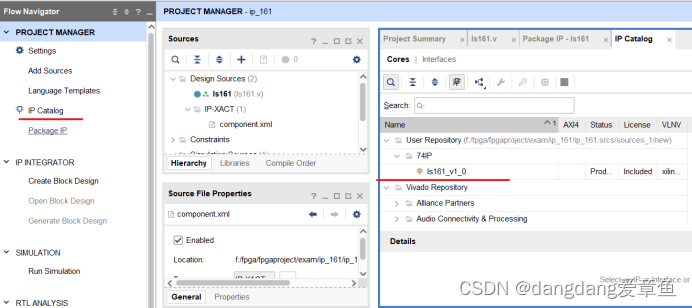

点击左侧导航栏中的IP Catalog,在右侧找到刚刚创建和封装好的IP核,说明创建封装好了,可以进行调用。

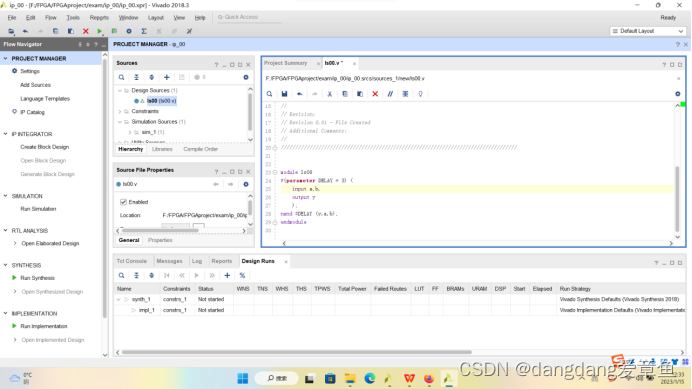

(5)创建和封装另一IP核764ls00,采用上面相同的步骤进行封装。

ls00源代码为:

module ls00

#(parameter DELAY = 3) (

input a,b,

output y

);

nand #DELAY (y,a,b);

endmodule

至此,创建和封装了两个IP核74ls161和74ls00。

该文介绍了如何使用Vivado2018.3创建和封装类似于74LS161计数器和74LS00门电路的IP核。首先创建工程,然后编写74LS161和74LS00的Verilog源代码,接着进行综合但不进行后续操作。之后设置IP核的包装器,定义库名和类别,并创建IP核。最后,封装IP核,检查和确认信息,完成74LS161和74LS00的IP核创建过程。

该文介绍了如何使用Vivado2018.3创建和封装类似于74LS161计数器和74LS00门电路的IP核。首先创建工程,然后编写74LS161和74LS00的Verilog源代码,接着进行综合但不进行后续操作。之后设置IP核的包装器,定义库名和类别,并创建IP核。最后,封装IP核,检查和确认信息,完成74LS161和74LS00的IP核创建过程。

1051

1051

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?