目录

1.芯片测试点分解

(1)得到测试点的过程叫分解,是将规格,场景,寄存器表单,接口信号,设计方案等多个维度和输入件的一个个展开,层层拆解出“通过如何测试可以证明设计是对的”这样一个逻辑关系式(xxx的激励,xxx的配置,xxx的处理,得到xxx的结果)

(2) 得到testcase的过程更多叫转换或者翻译,将测试点的关系式转换成文字形式的testcase,转换成实际用例。

(3)从逻辑信息上讲,或者从关系式上,testcase的信息应该等于测试点,不应该超出测试点中体现的关系式,所以叫覆盖。

(4)测试点的描述和测试用例表单的基本描述套路相同,就是描述上面的逻辑关系式“xxx的激励,xxx的配置,xxx的处理,得到xxx的结果"。只是测试点是讲逻辑关系,测试用例是实际映射到可以执行的实物。

2.芯片EDA验证几个概念澄清

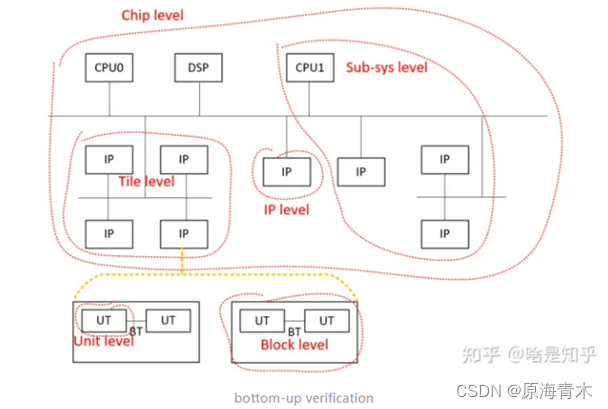

根据芯片规模划分,目前eda验证大概分为ut验证/bt验证/it验证/st验证。bt和ut验证属于模块级验证,st验证属于集成验证,IT验证介于二者之间。

- UT:unit level test( 单一功能单元)

- BT:block level test( 几个功能单元组成的功能块),

- IT:IP level test(寄存器,多个功能块),

- ST:sub-sys level test(sys bus和若干IP组成,一般含有处理引擎)

一个SOC项目的验证往往是以bottom-up(自底向上)的方式进行,从最底层的UT到BT,到IP level test(IT,寄存器,多个功能块),到tile level test(TT,若干IP和local bus组成),到ST,到最顶层的chip level test(CT,由一个或多个处理引擎,若干sys bus,所有IP)。随着层级的增加,验证的方法也由遍历到随机到局部随机到定向的转变。UT和BT因功能的差异一般采用独立的UVM环境,而IT,TT,ST和CT一般采用统一的UVM环境,测试激励可以复用。

本文详细阐述了芯片测试中的测试点分解过程,以及EDA验证中的UT、BT、IT和ST等不同层级的概念,强调了测试用例与测试点的关系,并讨论了验证方法在不同层级的变化。

本文详细阐述了芯片测试中的测试点分解过程,以及EDA验证中的UT、BT、IT和ST等不同层级的概念,强调了测试用例与测试点的关系,并讨论了验证方法在不同层级的变化。

1366

1366

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?