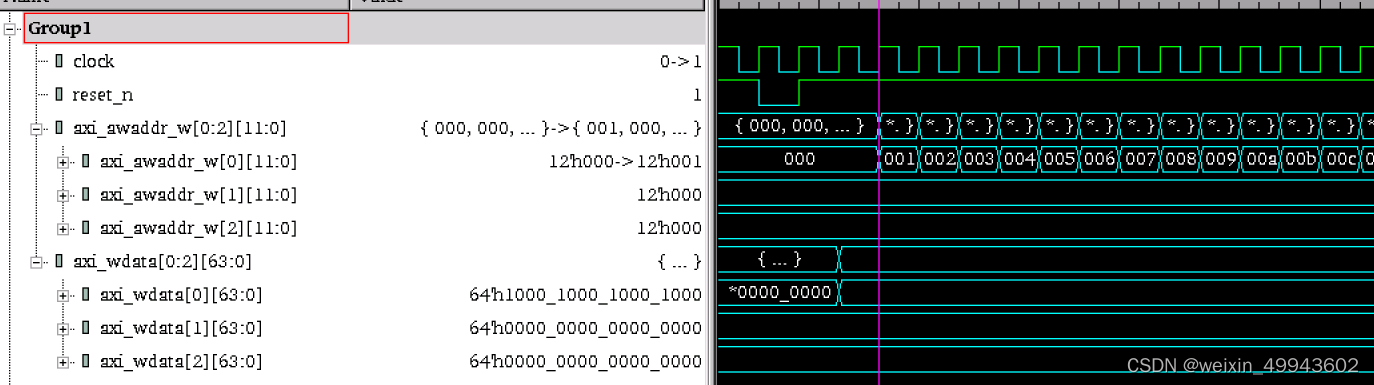

第一段代码仿真出错,后续的axi_wdata并未更新,monitor了一下data0和data1,这两个变量在仿真时间0时刻初始化为2‘h00和2'h10,而不是在等到复位后再等一个时钟才初始化,后续循环中并未更新,说明变量初始化和对赋值进行赋值有所不同。

initial begin: init_ram

int i, j, k;

wait (!reset_n)

@(posedge clock);

for (i = 0; i < 3; i++) begin : ram_loop

for (j = 2 * i; j < 16; j+=6) begin : row_loop

for (k = 0; k < 16; k++) @(posedge clock) begin : column_loop

bit [7:0] data0 = (j << 4) + k;

bit [7:0] data1 = ((j + 1) << 4) + k;

axi_wdata[i] <= {4{data1, data0}};

axi_wen[i] <= 1'b1;

end

end

end

end

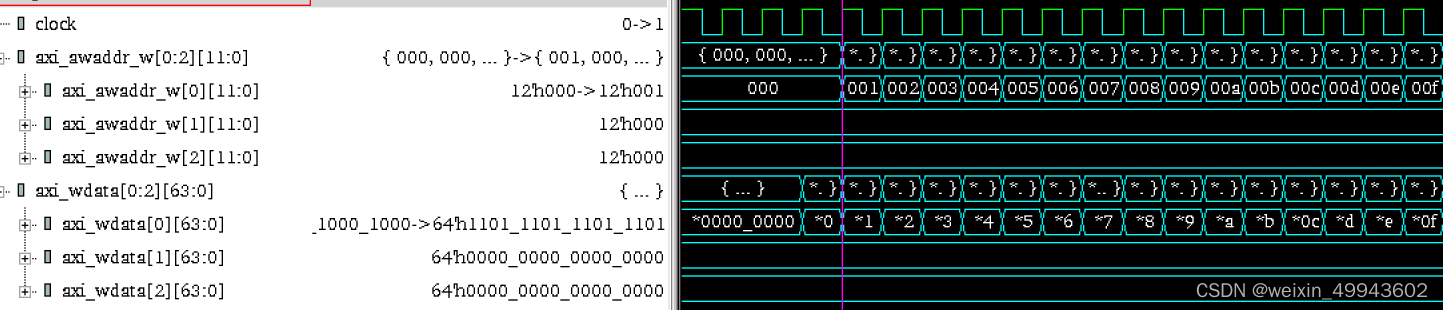

第二段代码仿真正常,begin end块中同一优先级的仿真事件顺序执行,先给data0赋值,然后data1赋值,然后计算axi_wdata的右式,最后计算axi_wen的右式。

initial begin: init_ram

int i, j, k;

wait (!reset_n)

@(posedge clock);

for (i = 0; i < 3; i++) begin : ram_loop

for (j = 2 * i; j < 16; j+=6) begin : row_loop

for (k = 0; k < 16; k++) @(posedge clock) begin : column_loop

bit [7:0] data0, data1;

data0 = (j << 4) + k;

data1 = ((j + 1) << 4) + k;

axi_wdata[i] <= {4{data1, data0}};

axi_wen[i] <= 1'b1;

end

end

end

end

8442

8442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?