数字IC设计学习笔记

序列检测

1. 基于状态机(FSM)的序列检测

1. 基于状态机(FSM)的序列检测)

-

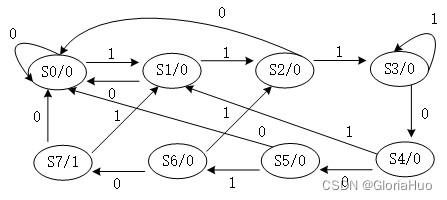

状态转移图

序列检测:1110010

-

Verilog代码

module det_seq(

input clk,

input rst,

input in,

output wire out,

output wire [2:0] state

);

parameter s0=3'd0;

parameter s1=3'd1;

parameter s2=3'd2;

parameter s3=3'd3;

parameter s4=3'd4;

parameter s5=3'd5;

parameter s6=3'd6;

parameter s7=3'd7;

reg [2:0] state_c;

reg [2:0] state_n;

//current state

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

state_c <= s0;

end

else

state_c <= state_n;

end

//next state

always@(*)

begin

state_n = s0;

case(state_c)

s0: begin

if(in==0)

begin

state_n = s0;

end

else begin

state_n = s1;

end

end

s1:begin

if(in==0)

begin

state_n = s0;

end

else begin

state_n = s2;

end

end

s2:begin

if(in==0)

begin

state_n = s0;

end

else begin

state_n = s3;

end

end

s3:begin

if(in==0)

begin

state_n = s4;

end

else begin

state_n = s3;

end

end

s4:begin

if(in==0)

begin

state_n = s5;

end

else begin

state_n = s1;

end

end

s5:begin

if(in==0)

begin

state_n = s0;

end

else begin

state_n = s3;

end

end

s6:begin

if(in==0)

begin

state_n = s7;

end

else begin

state_n = s2;

end

end

s7:begin

if(in==0)

begin

state_n = s0;

end

else begin

state_n = s1;

end

end

default: state_n = s0;

endcase

end

//output

assign out = (state_c==s7) ? 1:0;

assign state = state_c;

endmodule

【注】:个人学习笔记,如有错误,望不吝赐教,这厢有礼了~~~

1176

1176

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?