文章目录

参考文献

[1]Synopsys逻辑综合及DesignCompiler的使用

[2]DC综合流程

[3]DC综合——学习笔记

[4]博客园——IC_learner

前言

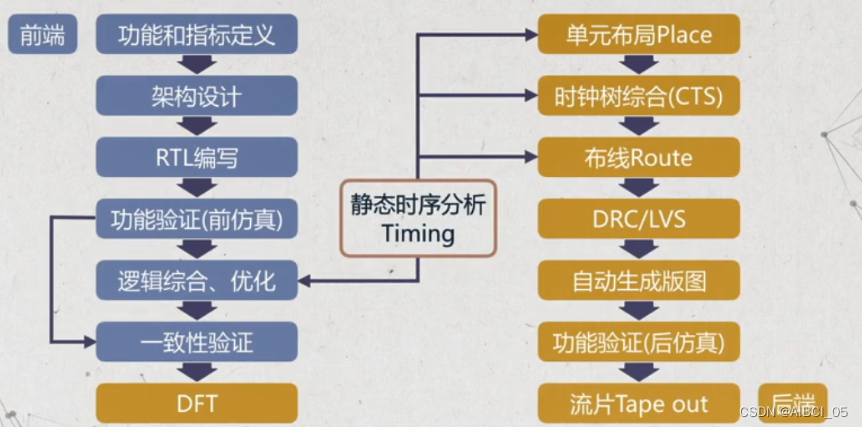

数字IC前端常用的综合工具是Synopsys的DC(Design Compiler)。虽然大多数情况下是使用脚本进行操作,但是干巴巴的脚本命令对于初学者来说无疑是天书,因此我觉得有必要对DC的图形化操作有一定的了解,这也能增加工程师对脚本命令的理解。下图为数字芯片的设计流程,其中DC用于逻辑综合、优化阶段。

图源文献[1]

DC是什么?

DC就是Design Compiler,直白来说就是芯片过程中的一个编译器。那为什么平时叫他综合而不是编译呢?这是因为DC对应着芯片设计流程中的synthesis(综合)。概括地说:综合就是把行为级的RTL代码在工艺、面积、时序等约束下转换成对应的门级网表,这无非就是将RTL代码编译成实际电路的过程。

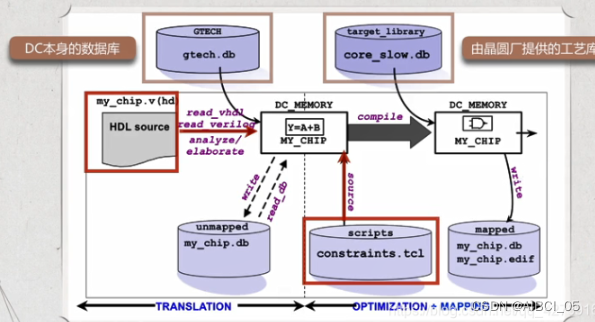

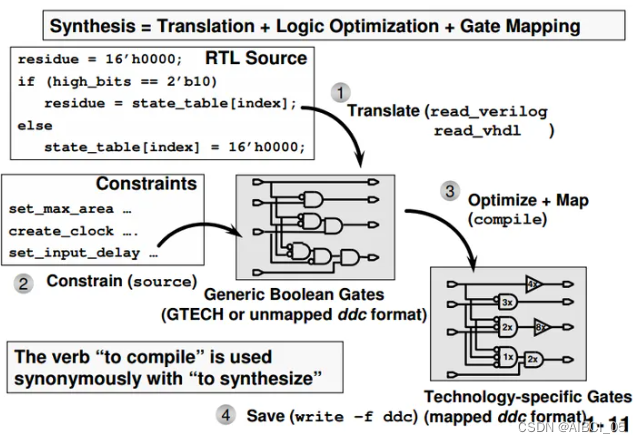

综合主要包括三个阶段:转换(translation)、优化 (optimization)与映射(mapping)。转换阶段综合工具将高层语言描述的电路用门级的逻辑来实现,对于DC来说,就是使用gtech.db库中的门级单元来组成HDL语言描述的电路,从而构成初始的未优化的电路。优化阶段是综合工具对已有的初始电路进行分析,去掉电路中的冗余单元,同时会根据工程师提供的约束条件对初始电路进行优化,使得电路在满足逻辑功能的前提下,尽可能得往工程师约束的条件靠近(比如说面积最小等)。映射是综合工具将优化之后的电路映射到由制造商提供的工艺库上,这里的工艺库就是target_library,最后生成网表文件用于后端设计。

图源文献[1]

该图更为清晰和直观得描述了综合的三个过程。

DC的操作步骤

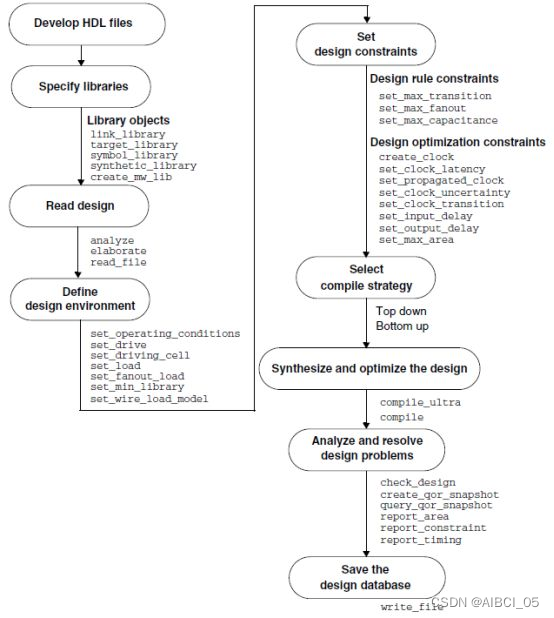

下图给出了DC进行逻辑综合时的基本步骤。

1. Develop HDL files

准备设计文件,DC的输入文件是HDL文件

2. Specify libraries

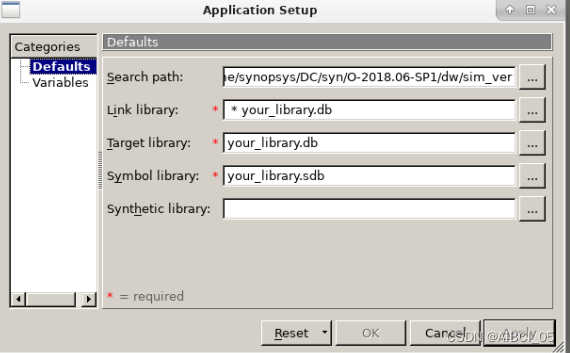

指定库文件,包括搜索路径(search_path)、链接库(link library)、目标库(target library) 、符号库(symbol library)、综合库(synthetic library)。

search_path

综合工具只会从该指定的路径去寻找各种库文件。

Link library & target library

Link library 和 target library 统称为 technology library(即工艺库,习惯称之为综合库),technology library 由半导体制造商提供,包含相关 cell 的信息及设计约束标准,其中:

Target library: 在门级优化及映射的时候提供生成网表的 cell,即DC用于创建实际电路的库。

Link library: 提供设计网表中的 cell,可以跟target_library使用同一个库,但是 DC 不用 link library中的 cell 来综合设计。包含target_library,在此基础上再加上IO库文件,IP库文件等

注意 :在 link_library 的设置中必须包含" * “,” * “表示 DC 在引用实例化模块 或者单元电路时首先搜索已经调进DC memory的模块和单元电路,如果在link library 中不包含” * ",DC 就不会使用 DC memory 中已有的模块,因此,会出现无法匹配的模块或单元电路的警告信息(unresolved design reference)。

当 DC 读入设计时,它自动读入由 link library 变量指定的库。当连接设计时,DC 先搜寻其内存中已经有的库,然后在搜寻由 link library 指定的库。

Symbol library

Symbol library 提供 Design Vision GUI 中设计实现的图形符号,如果使用脚本模式而不使用 GUI,可不指定 Symbol library 。

Synthetic library

虽然直译为综合库,但是常称为IP库,为Designware library。特殊的IP库需要授权(例如多级流水线乘法器),标准IP库由DC软件商提供,无需指定。

这里只指定搜索路径(search_path)、链接库(link library)、目标库(target library)即可。

3. Read design

读入设计就是将编写好的HDL代码载入内存。

4. Define design environment

定义设计环境,定义对象包括工艺参数(温度、电压等)、I/O特性(负载、驱动、扇出)。

5. Set design constraints

设置设计约束,包括设计规则约束(DRC,design rule constraints)和优化约束(optimization constraints),DRC由工艺库决定,在设计编译过程中必须要满足,用于使电路能按照功能要求正常工作。优化约束由工程师指定,为DC要达到的时序和面积优化目标。DC在不违反设计规则约束的前提下,尽可能满足优化约束。

6. Select compile strategy

选择编译策略。对于层次化设计,DC由top_down和bottom_up两种编译策略。

在top_down策略中,顶层模块和子模块一起编译,所有的环境和约束针对顶层设计,虽然此种策略自动考虑到相关的内部设计,但是此种策略中所有模块需要同时占用内存,硬件资源损耗打,不适合大型设计。

在bottom_up策略中,子模块单独约束,当子模块成功编译后,会被设置为dont_touch属性,不允许之后的编译过程修改,子模块编译完成后再向上编译父模块,直至顶层模块编译完成。由于该策略不需要所有模块同时占用内存,因此适用于大规模设计。

7. Synthesize and optimize the design

执行综合和优化,可以利用一些选项指导编译和优化过程。

8. Analyze and resolve design problems

分析及解决设计中存在的问题。DC在编译过程中会产生一系列报告,如时序、面积、约束、功耗等报告,工程师需要通过这些报告进行分析和解决设计中存在的问题。

9. Save the design database

保存设计数据。DC不会自动保存综合后的设计数据,因此需要手动保存网表、报告等数据文件。

实战

下面将通过DC的GUI界面体验一下综合的流程。

1. 准备工作

在设计目录下新建6个文件夹分别为netlist(保存网表文件)、report(保存报告文件)、rtl(保存RTL代码)、sdc(保存约束文件)、sim(保存仿真环境)、tb(保存测试文件)。并将编写的rtl代码全部放入rtl文件夹。

当然这些文件可以根据自己的喜欢新建和命名。

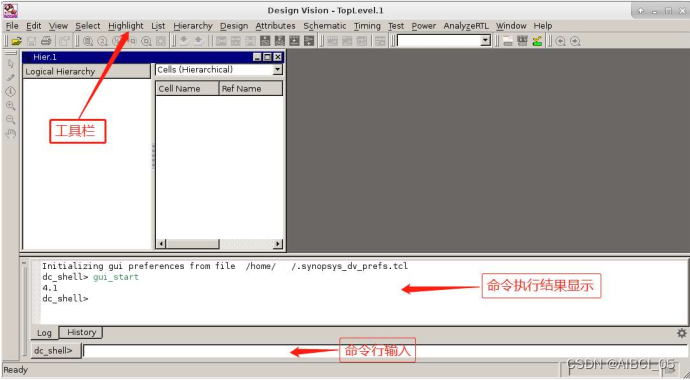

2. 打开DC

本文只介绍DC的GUI操作。在设计目录下打开终端,输入design_vision或者是dc -gui即可打开DC的GUI界面。

design_vision

# 或者dc -gui

3.Specify libraries——指定库文件

点击工具栏File,点击Setup,设置库文件。

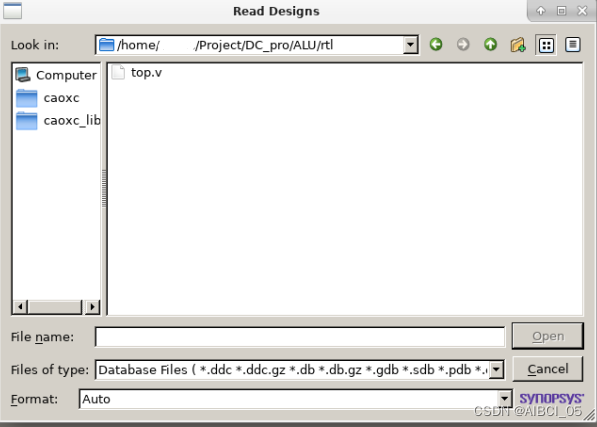

4.Read design——读取设计文件

点击工具栏File,点击Read,选择需要的设计文件。在下方的Log 框中出现successfully 字样表明读入文件成功。

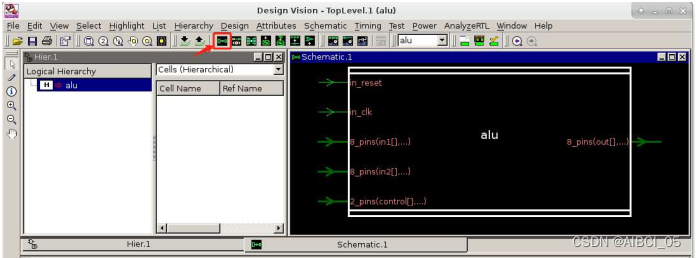

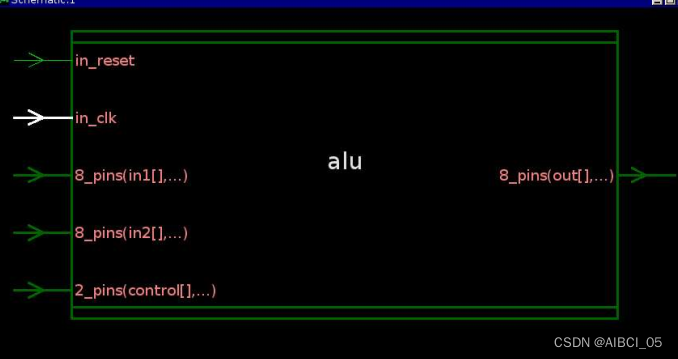

选中alu,点击红框处,可以查看电路的symbol图。

5.Define design environment——定义设计环境

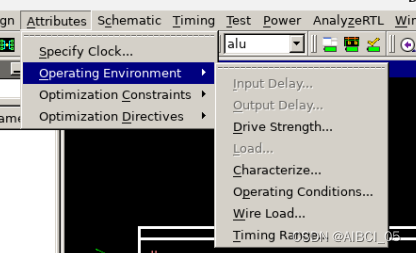

点击工具栏的Attributes,点击Operating Environment可以定义所需要的环境。

6.Set design constraints

DC中的约束有很多种,下面以常用的时钟约束和面积约束为例说明。

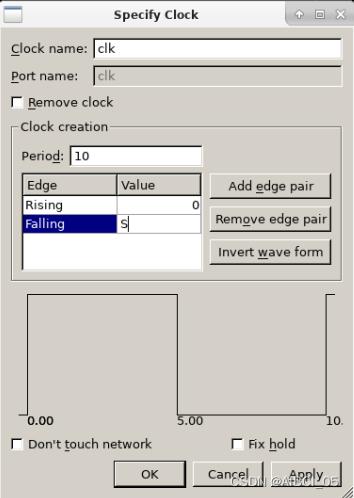

时钟约束

由于时钟约束是对clk端口进行约束,因此需要在symbol图上选中clk端口。

再点击工具栏Attributes,点击Specify Clock,在弹出窗口进行时钟的Clock name、Period、Rising、Falling的设置,单位默认为ns。

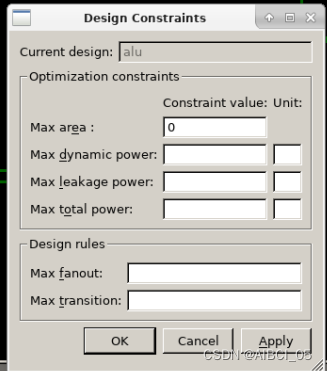

面积约束

点击工具栏Attributes,点击Optimization Constraints,点击Design Constraints。设置Max area 的值为0,表明让DC 向电路面积为 0 的方向来优化电路。当然,面积为0是达不到的。

另外其他约束可根据自己的需求进行设置。

7. Synthesize and optimize the design——综合设计

点击工具栏Design,点击Compile Design,保持默认即可,点击OK。在Log 框中出现Optimization Complete 字样表明优化完成。

8. Analyze and resolve design problems——查看报告并分析

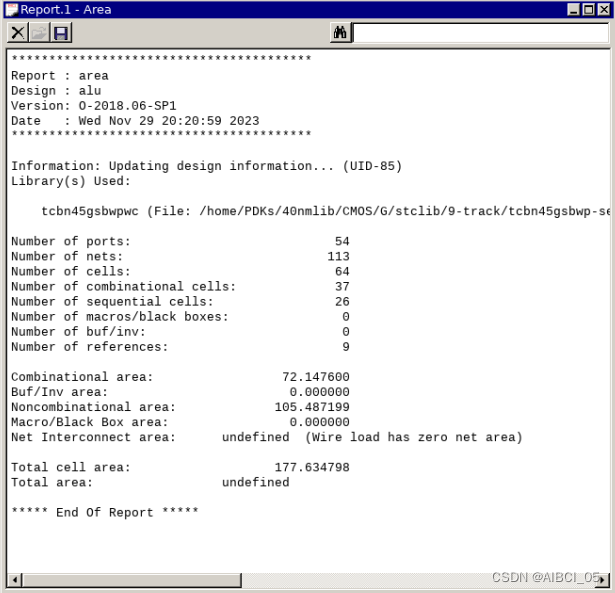

面积报告

工具栏选择Design,点击Report Area,点击OK。可以看到弹出窗口为面积报告,Total cell area为最终的面积,单位为平方微米。可以点击左上角的保存键,保存在report文件夹中。

约束报告

工具栏选择Design,点击Report Constraints,勾选all violators 选项(勾选

show all violators),意思是只报告没有达到前面设置的约束。点OK。可以点击左上角的保存键,保存在report文件夹中。

时序报告

工具栏选择Design,点击Report Timing Path,点OK。可以得到时序报告,报告的是最大延迟路径。可以点击左上角的保存键,保存在report文件夹中。

9. Save the design database

保存网表文件

工具栏选择File,点击Save As,保存路径选择netlist目录,文件类型选择WEILOG(v) 点Save。保存成.v文件即网表文件。该网表文件用于后面的版图设计。同时也可以通过点击工具栏的File,点击read,再选择该网表文件,就可以在DC中看到本次设计。

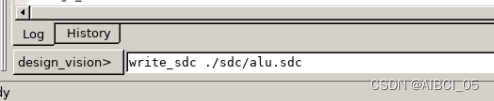

保存约束文件

sdc文件记录的是本次设计所有的约束条件。保存方法为在GUI界面的命令行窗口输入,点击回车后,log窗口返回1即为保存成功。。

write_sdc ./sdc/alu.sdc

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?