题目描述:

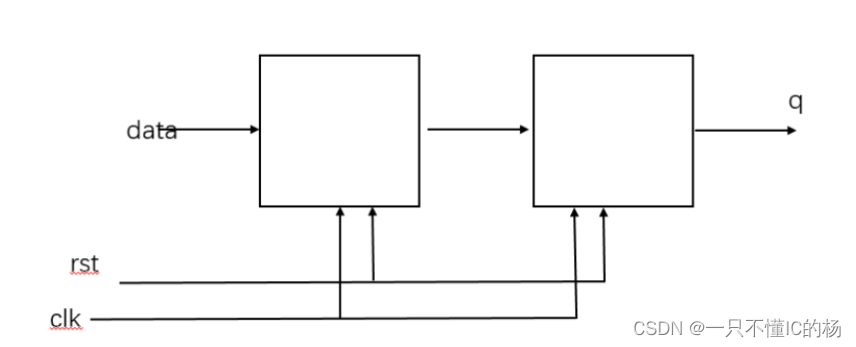

用verilog实现两个串联的异步复位的T触发器的逻辑,结构如图:

信号示意图:

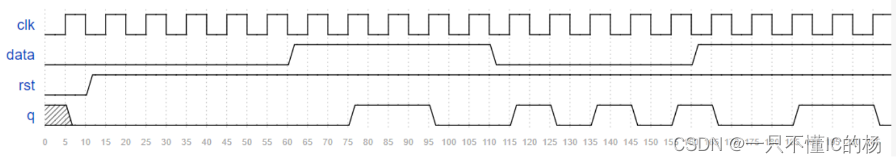

波形示意图:

输入描述:

输入信号 data, clk, rst

类型 wire

在testbench中,clk为周期5ns的时钟,rst为低电平复位

输出描述:

输出信号 q

类型 reg

题解:

解析:

T触发器:时钟触发到来时输入为1时,输出翻转,输入为0时,输出保持;

本题是两级触发器,前一级触发器的输出是后一级触发器的输入;

通过这个逻辑可以发现,除了使用条件语句之外,也可以使用异或逻辑;

另外:条件语句本质可以用三目运算符替代,但是在always语句钟少用三目运算符;

代码:

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,//rst 低电平复位

output reg q

);

reg q0;

always@(posedge clk&nbs***bsp;negedge rst)begin//异或逻辑

if(!rst)begin

q0<=1'b0;

q<=1'b0;//时序逻辑:非阻塞赋值;

end

else begin

q0 <= data^q0;

q<= q0^q;

end

end

/*always@(posedge clk&nbs***bsp;negedge rst)begin //条件语句

if(!rst)

q0<=0;//时序逻辑:非阻塞赋值;

else begin

if (data==1)begin

q0<=~q0;

end

else begin

q0<=q0;

end

end

end

always@(posedge clk&nbs***bsp;negedge rst)begin

if(!rst)

q<=0;//时序逻辑:非阻塞赋值;

else begin

if (q0==1)begin

q<=~q;

end

else begin

q<=q;

end

end

end*/

endmodule

467

467

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?