1.废话:这题学到两方面,一是复习巩固了下 T触发器 知识(胡扯,其实就是自己全忘了,压根 都不记得啥是T触发器);二是 纠正了自己verilog编写的误区,慎用非阻塞赋值,尤其是在always 时序块中;

2.正题

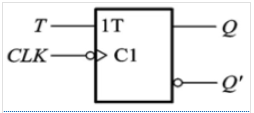

① 题目描述:

如上,不用细说了,实现上述串联 T触发器即为本题目标;

② T触发器

定义:在数字电路中,凡在时钟脉冲控制下,根据输入信号T取值的不同,具有保持和翻转功能的触发器,即当T=0时能保持状态不变,当T=1时一定翻转的电路。

示意图:

Q' = Q^T; 注:Q 与 T 是同一个时刻,Q' 是下一个时刻的Q值;

③ 慎用非阻塞赋值

`timescale 1ns/1ns

module Tff_2 (input wire data,

clk,

rst,

output reg q);

//*************code***********//

reg q1;

always@(posedge clk or negedge rst) begin

if (!rst)

q1 <= 1'b0 ; // q1 = 1'b0 ;

else if (data == 1'b0)

q1 <= q1 ; // q1 = q1 ; 最简洁写法: q1 <= q1^data

else if (data == 1'b1)

q1 <= ~q1; // q1 = ~q1 ;

else

q1 <= 1'b0; // q1 = 1'b0 ;

end

always@(posedge clk or negedge rst) begin

if (!rst)

q <= 1'b0 ; // q = 1'b0 ;

else if (q1 == 1'b0)

q <= q ; // q = q1 ;

else if (q1 == 1'b1)

q <= ~q; // q = ~q1 ;

else

q <= 1'b0; // q = 1'b0 ;

end

//*************code***********//

endmodule

情况描述:一开始没想那么多,因为 if-else if语句中没有多条并行执行,就偷懒用了 非阻塞赋值,即 // 后面的情况,仿真结果出错,改成非阻塞赋值,即通过仿真,结果正确。

附上几个评论,挺有警示作用。

467

467

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?