项目场景&问题描述:

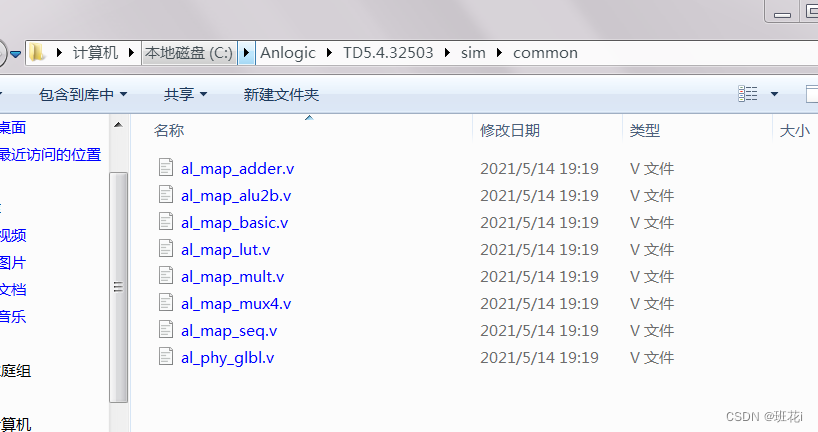

对TD的FIFO IP核进行仿真时,参照了这位大佬的 把TD的仿真库导入modelsim的文章

但是

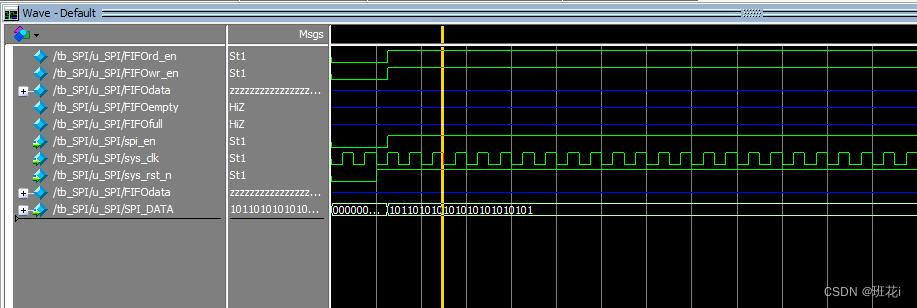

无论怎么输入信号(图中的FIFOrd_en、FIFOwd_en、sys_clk、DATA等)

输出信号始终为高阻态Hizzzzzzzzzzzzzzzzz (图中的FIFOdata、FIFOempty、FIFOfull)

其他IP核也是。。。。。。。。。。。。。。。。。

这不是手写FIFO能解决的事。。。

原因分析:

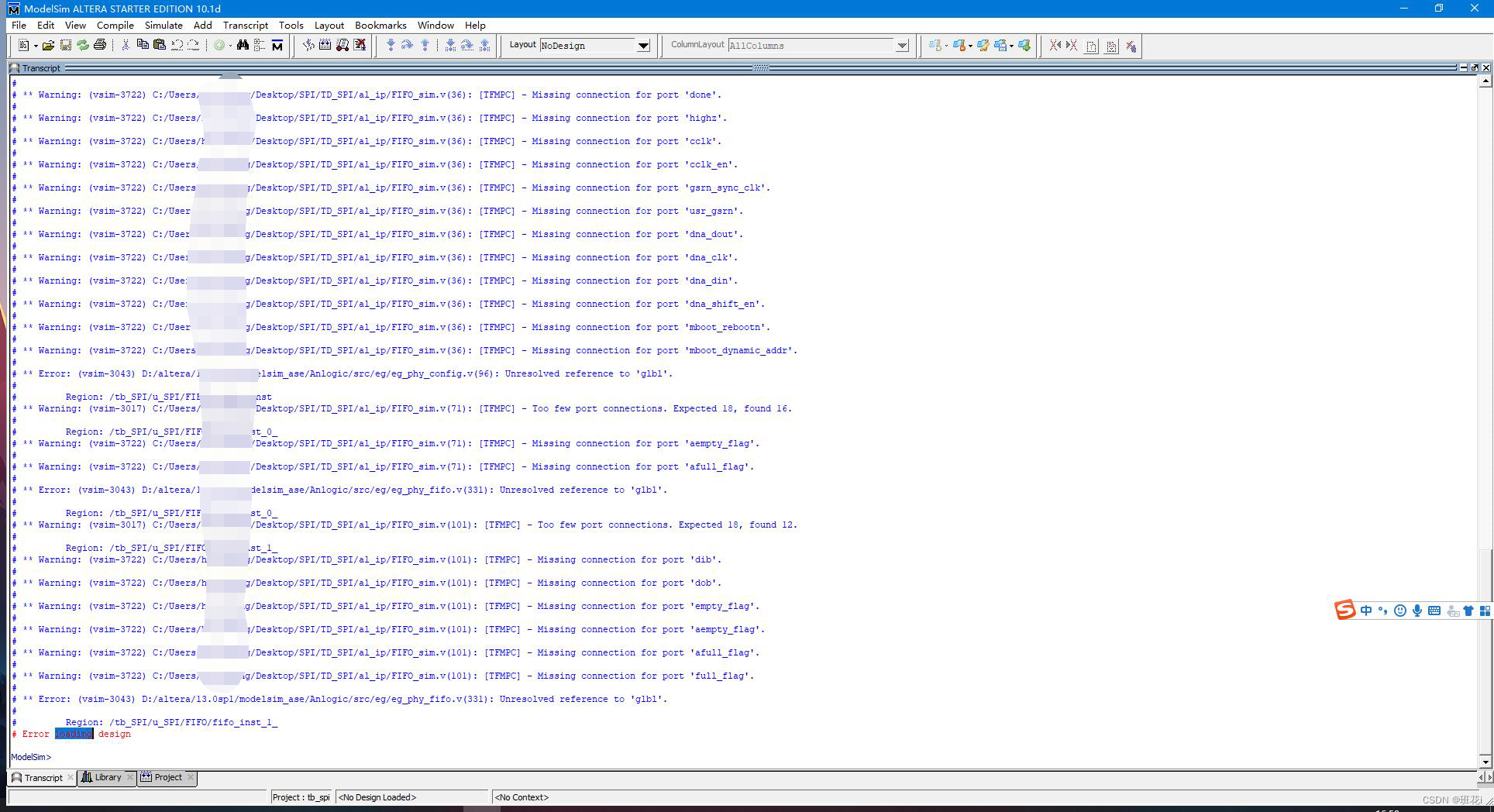

modelsim的具体报错

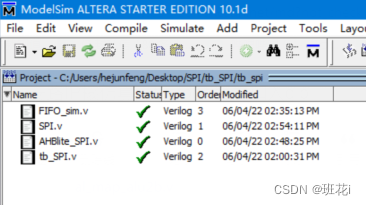

当编译

的时候,能start simulation

但是其实只应该加入FIFO_sim.v,这时候start simulation的报错如下

解决方案:

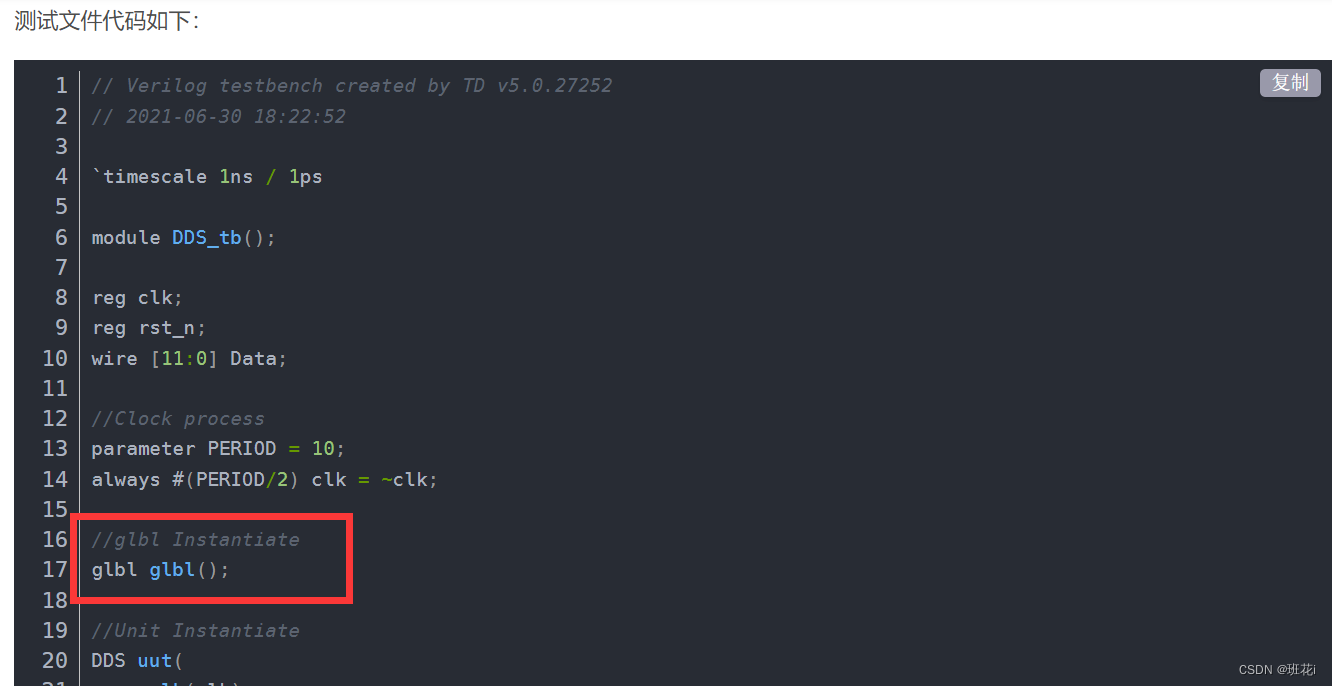

testbench需要调用glbl !!!!!!!!!!!!!!!!!!!!

//glbl Instantiate

glbl glbl();

见 文章的testbench的17行

另外一些细节:

1.最好把这个库一起导入EG4_ver,具体见文章

基于FPGA的DDS在Modelsim与TD的联合仿真(三)

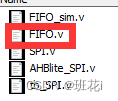

2.仿真的时候不用你的IP核的.v文件了,用_sim.v即可

比如我就用FIFO_sim.v而非是FIFO.v了

218

218

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?