VREF current generator(VRCG)判决电压发生器

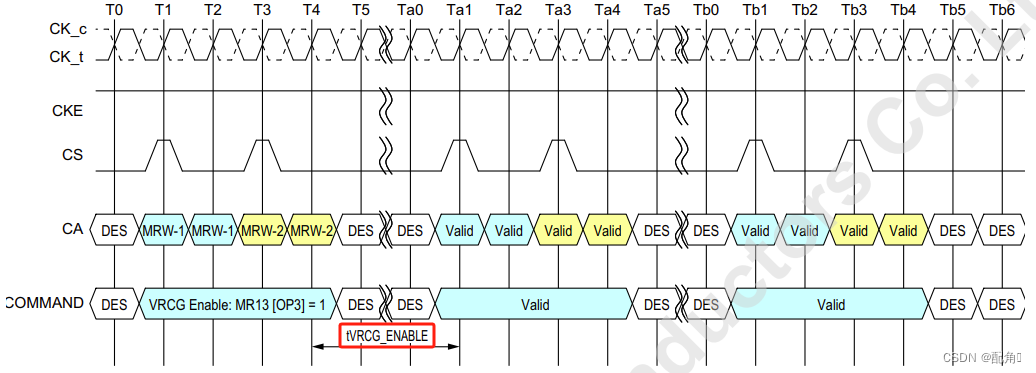

模式寄存器13的OP3是可以配置判决电压VREF的high current模式,这个high current模式可以减少在训练过程中或者切换FSP-OP时设置判决电压的时间,LPDDR4由SDRAM内部完成判决电压的训练,通过配置寄存器完成,在配置这个field时候需要满足两个参数要求,下图为配置为1时:

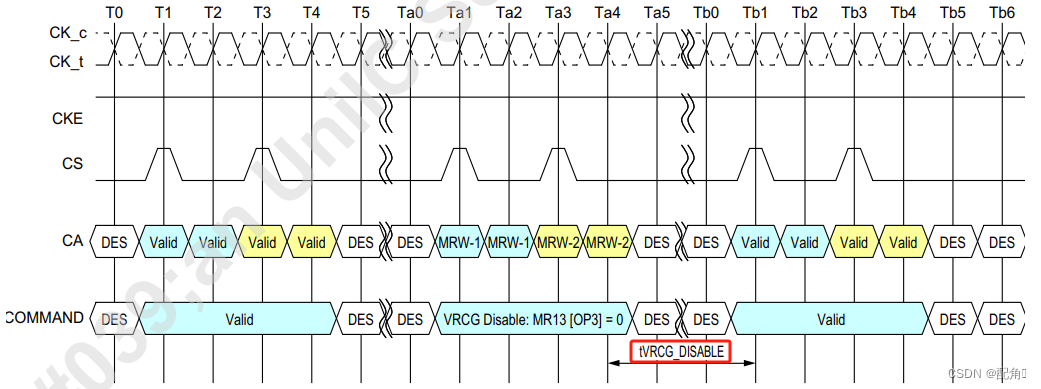

下图为配置为0时:

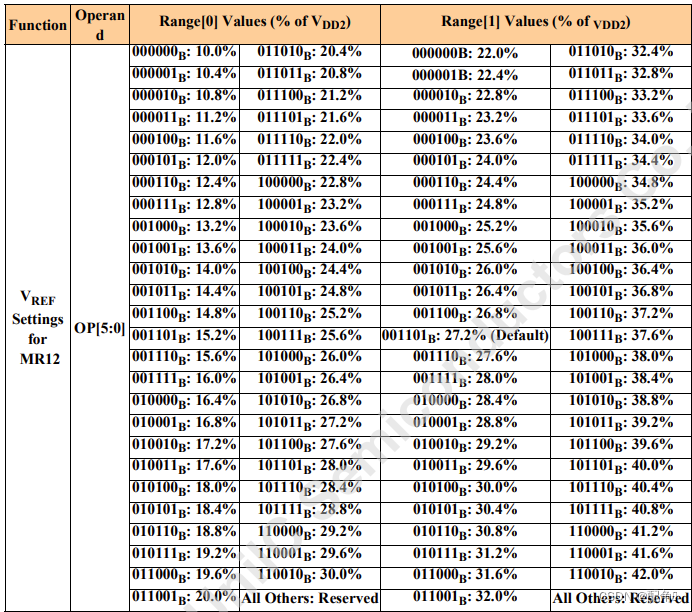

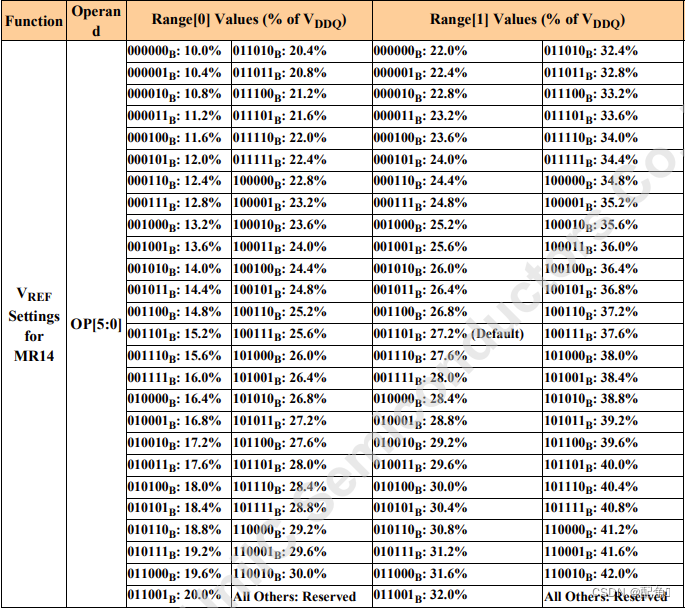

CA和DQ均有判决电压设置值和判决电压范围,其中判决电压范围有两种可选,range[0]为VDD2/Q的10%-30%,而range[1]为VDD2/Q的22%-42%,其中具体判决值由6bit寄存器可配。

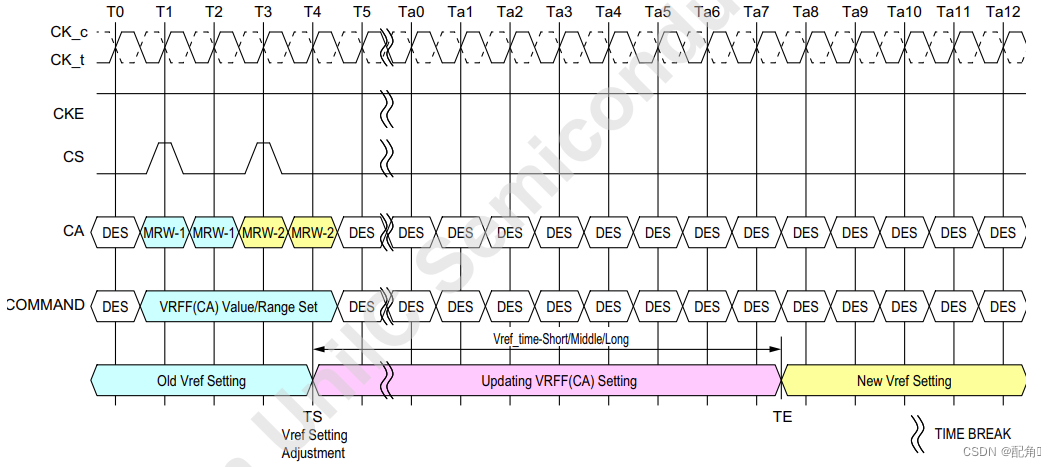

当更新判决电压设定时,需要满足如下时序:

MRW命令后需要等待VREF_time-short, Middle and long之后才会更新新的设置值。

865

865

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?