SDRAM:同步动态ram

SDR:1倍预取,即io速率和内部工作速率一致

DDR:2倍预取,改进了io采样方式为双沿采样,相比SDR,增加内部存储单元容量为原来的一倍,同样的内部工作速率,取出2倍SDR的数据,经过并串转换分配到io口,此时io时钟频率相比于sdr不变

DDR2:4倍预取,继续翻倍存储阵列,内部工作速率不变的情况下,一次取出4倍于sdr的数据,经过并串转换,同时io时钟频率翻倍,结合双沿,io速率达到sdr的4倍,实现4倍预取

DDR3:8倍预取,同理,io时钟频率最终提升至sdr4倍,结合双沿实现8倍预取

DDR4:号称16倍预取,内部结构还是以bank为基本单位,但是增加了bank group的概念,容量实现了提升,尚没弄清楚是如何提升带宽实现16倍预取的。

从上面ddr的发展历程,实际上sdram内部工作频率基本没什么变化,通过双沿和io时钟速率的提升实现带宽的提升。

LPDDR4:low power ddr4

基本颗粒类型(以下六种):

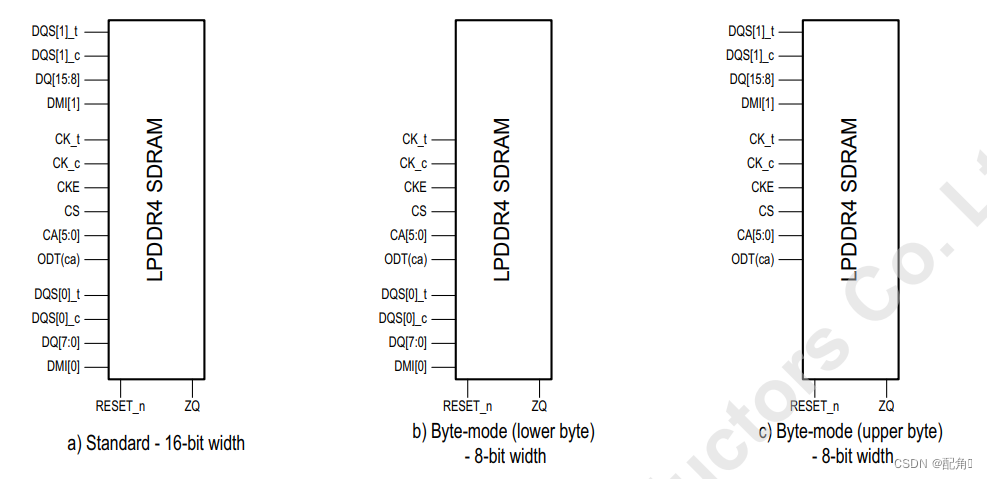

双通道:

单通道:

两个单byte模式均可以拼接成一个标准模式。

ZQ wiring:

当共用zq校准电阻时,必须确保zq校准命令到任意一个die是不是重叠的,否则可能会导致不同的个die同时进行zq校准而它们可能share同一个zq resistor。甚至对于双通道die也要保证zq校准start命令可以独立的到达两个channel。

die pad口定义:

| CK_t_A CK_c_A CK_t_B CK_c_B | input | 差分时钟,通道独立(双通道所有pad均通道高独立),all CA命令在CK_t上升沿采样 |

| CKE_A CKE_B | input | 时钟使能 |

| CS_A CS_B | input | chip选择 |

| CA[5:0]_A CA[5:0]_B | input | 命令/地址(command/address) |

| ODT(ca)_A ODT(ca)_B | input | 同寄存器联合决定CA ODT功能的开关 |

| DQ[15:0]_A DQ[15:0]_B | I/O | data bus |

| DQS[1:0]_t_A DQS[1:0]_c_A DQS[1:0]_t_B DQS[1:0]_c_B | I/O | data strobe signal,以字节为单位,数据每字节1bit。read时由dram产生,并且边沿和数据对齐;write时由controller产生, |

| DMI[1:0]_A DMI[1:0]_B | I/O | 数据mask/invert信号,以字节为单位,数据每字节1bit mask/invert信号 |

| ZQ | 校准pin,连接240欧姆±1%电阻 | |

| VDDQ VDD1 VDD2 | supply | 电源 |

| VSS VSSQ | GND | 地 |

| RESET_n | input | 复位,低有效 |

单通道同,不再赘述

不同die的容量:

每个通道包含8个bank,容量分别有1、2、3、4、6、8、12、16Gbit;

因此双通道die容量有2、4、6、8、12、16、24、32Gbit。

实际上对于双通道die有标准模式(×16)和字节模式(×8),这两种die其容量都是一样的。因此在封装时可以根据需求进行die的mix。

lpddr4是16倍预取。

×16 mode(以channel为例):

| 1Gb | 2Gb | 3Gb | 4Gb | 6Gb | 8Gb | 12Gb | 16Gb | |

| array pre-fetch | 256(16*16) | 256 | 256 | 256 | 256 | 256 | 256 | 256 |

| 列数 | 64 | 64 | 64 | 64 | 64 | 64 | 64 | 64 |

| page size(行容量) | 2048B | 2048B | 2048B | 2048B | 2048B | 2048B | 2048B | 2048B |

| 行地址 | ||||||||

| 列地址 | C0-C9 | C0-C9 | C0-C9 | C0-C9 | C0-C9 | C0-C9 | C0-C9 | C0-C9 |

列地址只有10个bit,由于16倍预取,地址[3:0]可以tie 0,因此只有6个bit用于列地址,即64列,因此page size就是256bit*64=2048B。行地址位宽需要满足最终容量,16Gb需要17bit行地址。

对于×8 mode,pre-fetch即16*8bit,page size是128bit*64=1024B。

CA bus只有6bit,lp4为了减少pin脚数量,采用1、2、4个clk去传输CA,且在clk上升沿传输。

参考command truth table。

本文概述了SDRAM(包括SDR、DDR、DDR2、DDR3和DDR4)的发展历程,重点在于预取机制如何通过提高IO时钟频率和内部操作来提升数据传输速度。同时介绍了LPDDR4的低功耗特性,以及diepad口、ZQ校准和CMDbus的细节。

本文概述了SDRAM(包括SDR、DDR、DDR2、DDR3和DDR4)的发展历程,重点在于预取机制如何通过提高IO时钟频率和内部操作来提升数据传输速度。同时介绍了LPDDR4的低功耗特性,以及diepad口、ZQ校准和CMDbus的细节。

1729

1729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?