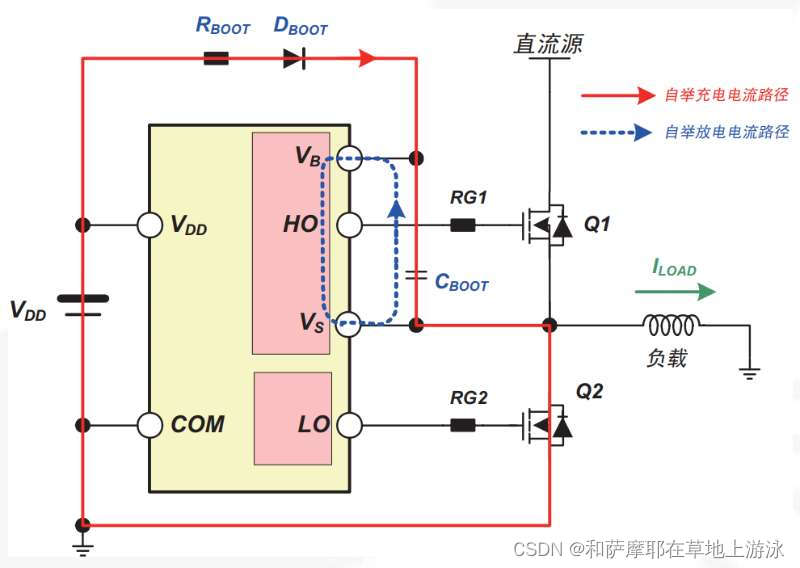

1.工作原理

Q1与Q2不能同时导通,否则会出现短路,炸管

Q1关断,Q2导通时,回路如红线所示,Cboot两端电压小于Vdd,电源给Cboot充电,电容电压近似为Vdd

Q2关断,Q1导通时,若没有Cboot,则Q1无法构成回路,类似“悬浮”状态,Cboot加在芯片VB和VS端,相当于电流源,放电,构成回路。Q1导通,Vds压降近似为0,所以此时Vs≈Vin,瞬间被抬高。自举电容两端电压不能突变,即并联着的Vb-Vs压差不变,为Vdd。因此,要想满足Q1导通,即Vb>Vs,则Vb电压为Vdd+Vin,仍满足Vb-Vs=Vdd+Vin-Vin=Vdd>Vt>0,导通。

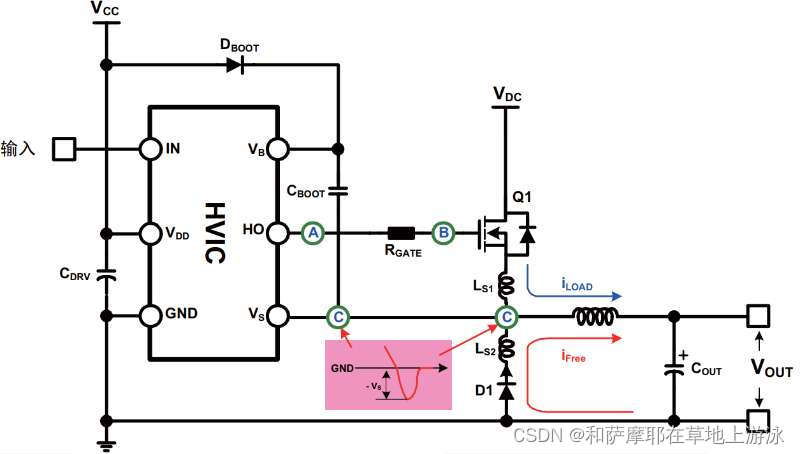

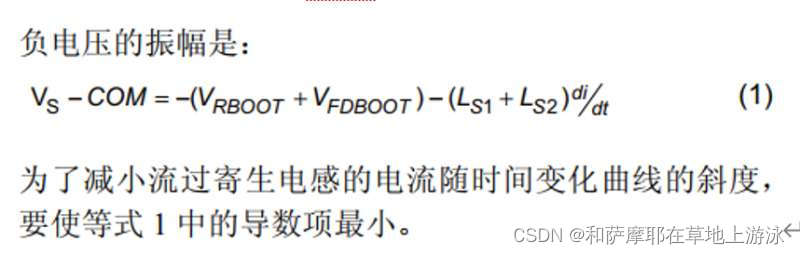

2.高端mos关断时会出现瞬态负压

原因:高端mos关断时,由于负载电感电流不能突变,因此Q2的内部续流二极管工作,构成地-Q2续流二极管-Lload-地的回路,由于D1正向偏置,因此C点电位<地,即Vs为负压,此时Vdd会瞬间给Cboot充电,而Cboot上的压降最高可达Vdd+Vs幅值,若Vs过大,则电容可能会被击穿

3.负压会造成的问题

(1)电容过压被击穿,理由如2,幅值为Ls*di/dt(所以要限流,还有布线时让自举电容靠近IC,减小Ls与电容的谐振干扰)

(2)信号丢失:Vs过大,超过最大额定值,栅极驱动电路会造成损害,出现信号丢失

(3)闭锁:高端栅极驱动电路一般都含有寄生二极管,Dbs导通时会出现下冲电压,累积到Cboot上,加大Cboot压降,使得自举电容被过度充电

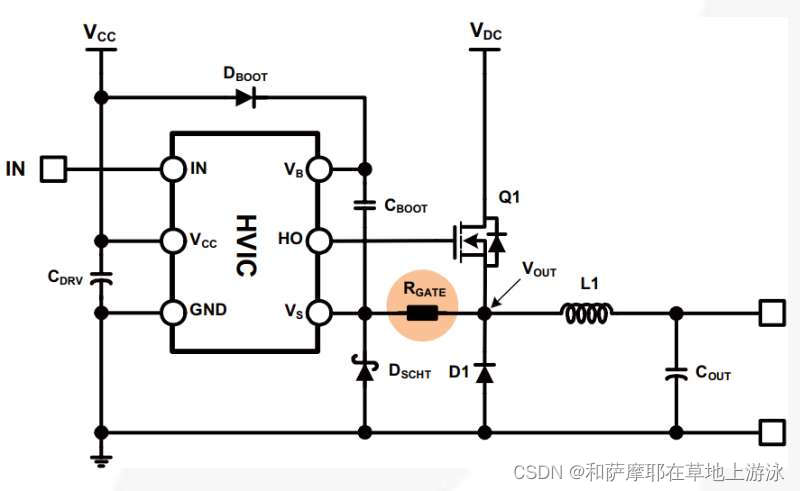

4.补偿措施

(1)加Rboot

作用:限流,延长充电周期

缺点:电阻过大会使得与Vbs导通时间不匹配,不能解决(可以缓解)过压问题,减缓了再冲电过程

计算:t=Rboot*Cboot/D 要与低端mos的导通时间Ton匹配

怎么匹配:D2导通时间Ton要差不多等于Cboot时间常数的5倍(根据衰减规律,差不多5倍充满电),计算时要注意时间常数和占空比D有关,时间常数=Rboot*Cboot/D。但要是接Rvs的话 时间常数里R就会变 具体看Rvs和Rboot的串并联关系(一般为串

注意:这里的R指的是Cboot连接的单口网络的等效戴维南电阻,并不直接是Rboot

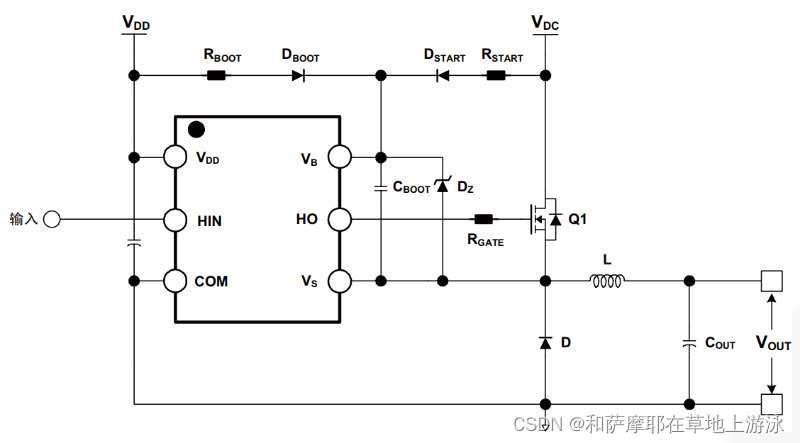

(2)自举电容并联一个稳压二极管(但一般不加,因为pcb位置不够

防止MOS管产生的浪涌电流造成损坏,同时让电容两端电压更稳定

(3)重布置栅极电阻,在地和VS之间加一个肖特基二极管(0.7V压降)

负电压的放大倍数正比于寄生电感和开关器件的关断速度,di / dt ;它由栅极驱动电阻,RGATE和开关器件的输入电容,Ciss决定。寄生电感在PCB布局时要注意走线宽一点,自举电路要靠近IC且回路面积要小,过孔少一点,线尽量转45/135°角;输入电容没办法改变,但是可以通过在栅源极并联电容来改变实际的Ci,通过增大容量来延缓开关时间;Rgate可以做调整,电阻增大,电流减小,变化率减小,从而减小负电压。但问题是增大电阻会增加电阻损耗,而增大电容会影响死区时间,若死区时间过短,则会炸管。因此,在实际应用时,应综合考虑电阻电容的取值。

栅极电阻Rgate决定了mos的导通和关断时间,所以会限制肖特基二极管在VS被拉到负压时的电流

Cboot两端各连一个二极管,使得自举电容不会出现过电压(Vs负压被钳位在肖特基的正向压降值-0.7V,因为续流二极管的电流大小要满足负载回路的电流大小,因此续流二极管上的电压一般也会比较大,所以Vs的负压过大就会导致电容被损坏)

5.其他应用-输出电压在输入电源加载到转换器前就已经存在时

满足一些电压大小关系时,Vdd不会给Cboot初充电,而是由Vdc(也就是Vin)给Cboot充电,如果说Q1导通时间太短,那么Cboot就充不满电,加一个Rstart来使得电流有一个极小值,从而使得效率变大。正常工作时,Vdz=Vcboot>Vdd,我的理解是要不就会使得Dboot导通,Vdd给自举电容充电

6.器件选型

(1)自举电容

允许的最大电压降(不是耐压!):ΔV=Vdd-Vf(Dboot压降)- Vrboot(自举电阻两端的压降)-Vcesat(下管S2的导通压降)-Vgsmin(最小栅极驱动电压) 回路,KVL

容值:推荐容值是100nF到570nF,但实际使用时要根据电路来选择,比如容值过大时会使得充电时间大于低端mos导通时间,从而使得电容充不满电

可以粗略算一下:C=I*ΔT/ΔV

I是芯片直流电源电流典型值,ΔT是高端开关的导通时间(根据Fsw和占空比算),实际使用电容应大于计算出来的这个值

(2)自举电阻

该电阻值(一般5~15Ω)不能太大,否则会增加VBS时间常数。最初给自举电容充电时,可能出现很大的峰值电流。这可能会干扰其他电路,因此建议用低阻抗的自举电阻限流

自举电阻太小限制:

(i)充电电流过大在小功率输出应用触发采样电阻过流保护

(ii)过小的自举电阻可能会造成更高的dVbs/dt,从而产生更高的Vs负压

限流原因↑

(iii)充电电流过大容易导致充电阶段Vcc电压过低,造成欠压保护。

(iv)容易造成自举二极管过流损坏。

(3)自举二极管

自举二极管必须快,因为它的工作频率和IGBT是一样的,另一方面,它必须有足够大的阻断电压,至少和IGBT的阻断电压一样大。这就意味着600V的IGBT,必须选择600V的自举二极管

总结:

1.由于上管的开启需要自举电容对其放电,为了保证上端的正常开关,需要调节PWM,给自举电容预留一段充电时间(propagation delay times)。

2.自举电容取值一般以无感或低感的电容为好,另外PCB布局上充放电回路要尽量短,减少走线的寄生电管,避免产生LC振荡;去耦电容和栅极电阻的布局和布线要尽可能地靠近栅极驱动集成电路。

3.自举二极管Dboot一般考虑导通电流和反向耐压值。自举二极管用于自举电容的充电,当上管开启时,它承受着MOS管漏极相等的电压,所以二极管反向承受电压要大于供电电压。如果VS为负压,反向耐压则>Vin+负压 的电压之和。一般选用反向耐压和反向恢复时间性能都较好的快恢复二极管。开关二极管

4. 如果使用了铝电解电容做为自举电容,就应再用一个瓷电电容(选低ESR的)。如果自举电容是瓷电或钽电容,自己做为就地耦合也就足够了。Vdd和COM间的电容,同时支持低端mos和自举电容的再充电,因此容值要是自举电容的十倍以上。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?