一、解决思路

负压的放大倍数正比于寄生电感和开关器件的开关速度di/dt,它由栅极电阻和开关器件的输入电容Ciss决定。因此,为了减低负压,可以减少寄生电感,或限流来降低寄生电感的影响;可以加大栅极电阻延长关断开启时间;可以在栅源极并联电容,降低米勒电容对电路的影响。但加大栅极电阻会增加电路损耗,影响电路长时间工作的稳定性;电容和电阻数值的改变会延长开启和关断时间,可能会影响死区时间,让mos炸管。

并联栅源电容后会让尖峰电流更快地经过,但并联电容会出现一个右半平面零点,减小相位裕量,使得系统稳定性变差。解决这个零点的办法有三个,一个是让零点和第二极点抵消(这个好用),一个是让零点和谐振频率相等,还有一个是让零点和十倍频率相等,从而完全抵消掉右半平面零点的影响。但是电路器件过多,谐振频率很难求(阻抗相等得谐振频率),而且有很多寄生电感,因此我选择用第一种办法。

二、理论计算

重点是选取电容电阻的数值,电阻经验值是10Ω,电容经验值是2.2nF,但由于PCB走线和测量温度等其他因素的存在,不同板子的寄生电感不同,因此还是要实际测试。下面是通过理论计算来嵌定电容电阻的取值范围,从而更加方便调试选值。不过仅供参考。

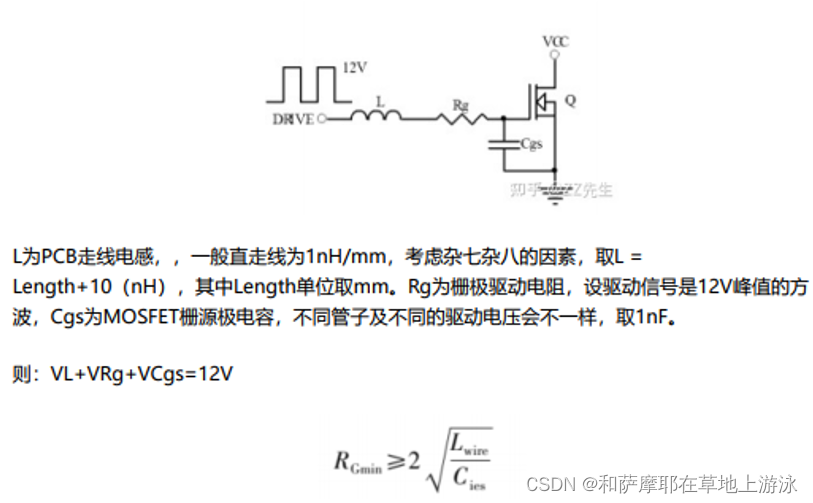

1.电阻范围——最大值考虑导通时间的影响(损耗),最小值考虑对震荡的解决效果

(1)最小值:

PCB过孔近似的寄生电感:L=5.08h[ln(4h/d)+1],其中L指PCB过孔的电感,h是PCB过孔的厚度,d是孔的内径。从式中可以看出,PCB过孔的内径对电感的影响较小,而对电感影响最大的是PCB过孔的厚度/长度。

(2)最大值:

栅极电阻对上升时间的影响可以这样考虑:上升时间可以用2xRgxCgs,通常上升时间小于导通时间的二十分之一时,MOSFET的开关导通损耗不至于会太大造成发热问题,因此当MOSFET的最小导通时间确定后,Rg最大值就确定了,一般Rg在取值范围内越小越好。

估值:Rg=Vcc/Ipeak 且Rg要大于Rsink,目的是在延长导通时间时减小对死区时间的影响。

2.电容范围

由RC=1/(6-10)f来大概确定C的值,f一般几十到几百k,C一般在10nF以内。

也可以通过让C=(1/3-1/5)CL来确定(但CL一般不知道,所以还是拿频率求一下

3.电容电阻关系——右半轴零点和第二极点抵消

零点位置Z=1/(1/gm-Rg)*Cgs gm=ID/VG

第二极点Pb=1/Resr*Cb Resr是输出电容的等效电阻,Cb是旁路电容

二者相等,得出RC关系

三、波形分析及调整思路

Δ对于单管电路:LS Turn On时

1.在HS加Cgs电容:主要解决非开关动作一侧的正向浪涌

开启时:

①抑制LS的正向Vgs浪涌;

②相电压下降更慢

③Id的开启浪涌减小

关断时:

①稍稍抑制LS的负压

②相电压变得更稳

缺点:关断开启时间延长,损耗加大

总结:在查看波形时,若LS源极对地的负压可接受,且相电压除过冲点外震荡不强,其他波形没有很差时,尽量选小的Cgs并联电容

经验值为2.2nF,一般不超10nF(看MOSFET的Cgs参数,若Cgs和并联电容相差太大,如Cgs为15nF,并联的为2.2nF,则波形改善效果不大

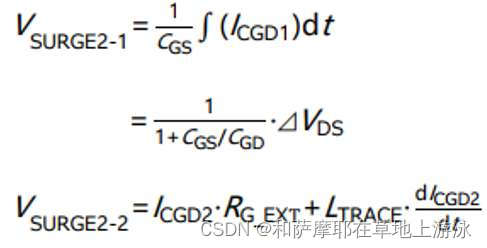

2.减小HS的反向电阻:主要解决LS开通时HS的Vgs电压尖峰,使其不超3V,防止同时导通

LS开通时,HS续流,电流从Cgd流向Cgs(1式)和反向电阻(2式),2式的R/I均为反向电阻/电流。减小反向电阻来改善尖峰值。其实Ltrace是最重要的参数,因此在PCB布局时要格外注意,尽量减小寄生电感

Δ对于单管电路:LS Turn Off时

减小HS栅极电阻:主要抑制LS关断时HS产生的负压尖峰,但不明显

Δ注意:Vgs正向峰值也会加大,而且HS能承受的负压尖峰值往往更大,故一般将降低Vgs正向峰值电压为首要目标

总结:

- 加Cgs电容,减震荡;改Rgate,稍改善负压

- 波形重点看:LS栅极对地负压<5V(看器件手册)

一管导通时另一管震荡幅值不超Vth(3V左右,看器件手册Vth)

相电压除过冲点外震荡较小,平稳

- 除米勒电容外,寄生电感对电路的影响也很大,因此PCB布局时要注意过孔数量少一点,电容靠近MOSFET。R=2*(L/C)1/2,寄生电感过大时,要加大R

Δ对于多管并联,减小震荡的办法:

- 增大外部栅极电阻

- 栅极插入磁珠

1219

1219

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?