目标:

- 了解数字IC设计的流程;

- 数字IC设计流程中各阶段主要工作;

- 数字IC设计流程中各阶段主要EDA工具;

1. 集成电路产业链:

集成电路设计公司→晶圆厂→封测厂→组装厂→成品整机。

2. 数字IC设计流程

数字IC设计又可以分为ASIC设计和FPGA/CPLD设计

- ASIC(Application Specific Integrated Circuit,专用集成电路):需制作掩膜,设计时间长,硬件不能升级,芯片面积小性能可以得到较好的优化等

- FPGA/CPLD(Field Programmable Gate Array,现场可编程门阵列 / Complex Programmable Logic Device,复杂可编程逻辑器件):不需后端设计/制作掩膜,可编程,设计时间较短,方便升级优化硬件,芯片面积大性能不够优化等

2.1 基本流程:

确定项目需求

- 物理指标:制作工艺、裸片面积、封装

- 性能指标:速度、功耗

- 功能指标:功能描述、接口定义

系统级设计

- 用系统建模语言对各个模块进行描述

前端设计

- RTL设计、RTL仿真、硬件原型验证、电路综合

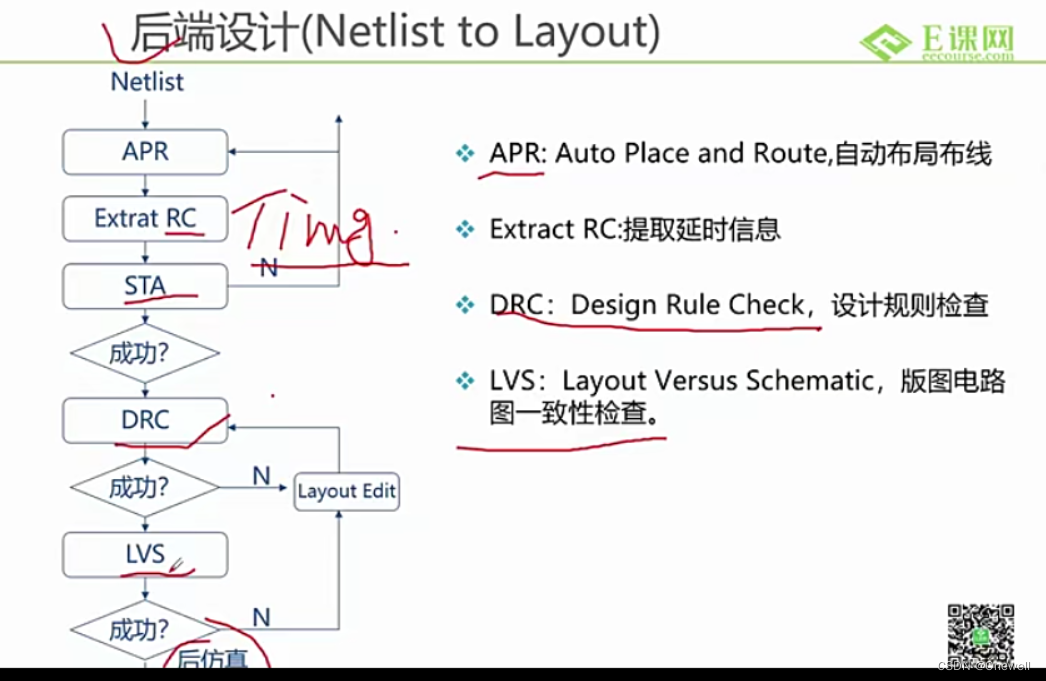

后端设计

- 版图设计、物理验证、后仿真等

2.2 数字IC设计流程

典型ASIC设计流程:逻辑设计→物理设计(RTL2GDSII)

逻辑设计:芯片架构→RTL设计→功能仿真→综合→形式验证→STA→DFT

物理设计:布局布线→寄生参数提取→STA→设计规则检查、版图一致性检查→GDSII

2.3 各阶段主要工作及EDA工具

芯片架构:根据项目需求确定架构,输出设计规格说明书(design spec)

RTL设计:利用硬件描述语言对电路进行寄存器传输级(RTL)的描述

RTL仿真:检验RTL设计代码是否实现了spec描述的功能,也称为前仿真,综合后再进行的仿真称为后仿真(时序仿真)——工具VCS、NC、Modelsim

逻辑综合:把RTL设计代码映射到特定的工艺库上,添加约束文件,输出成门级网表Netlist——工具DC

形式验证:从功能上对综合后的网表进行验证,保证综合过程中没有改变原先HDL描述的电路功能,常用的就是等价性检查方法——工具Formality

静态时序分析:STA,在时序上对电路进行验证,检查电路是否存在建立时间和保持时间的违例——工具PT

DFT:扫描链插入,使设计中的所有寄存器可以通过设计的输入输出进行控制和观察,用于在芯片生产之后测试芯片的良率

布局布线:布局(确定各种功能电路的摆放位置),时钟树的插入(时钟信号的布线),布线(普通信号的布线)——工具ICC、Innovus

寄生参数提取:提取延迟信息

静态时序分析:加入了布局布线延迟,更真实的时序分析 ——工具PT

版图验证:DRC设计规则检查/LVS版图一致性检查——工具Calibre、Hercules、Diva/dracula

参考资料:【详细】芯片设计全流程(包括每个流程需要用到的工具以及需要参与的工作人员)_Cheeky_man的博客-CSDN博客_ic设计流程图

806

806

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?