问题描述

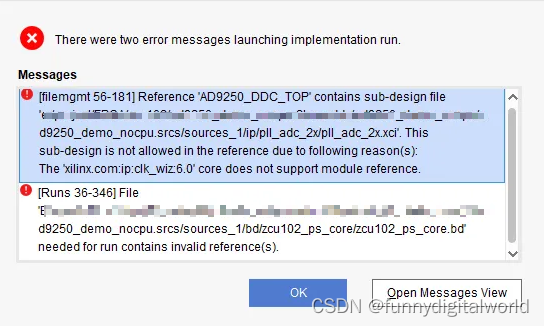

[filemgmt 56-181] Reference 'AD9250_DDC_TOP' contains sub-design file 'e:/project/FPGA/zcu102/ad9250_demo_nocpu-2lane-ddc/ad9250_demo_nocpu/ad9250_demo_nocpu.srcs/sources_1/ip/pll_adc_2x/pll_adc_2x.xci'. This sub-design is not allowed in the reference due to following reason(s):

The 'xilinx.com:ip:clk_wiz:6.0' core does not support module reference.

问题原因

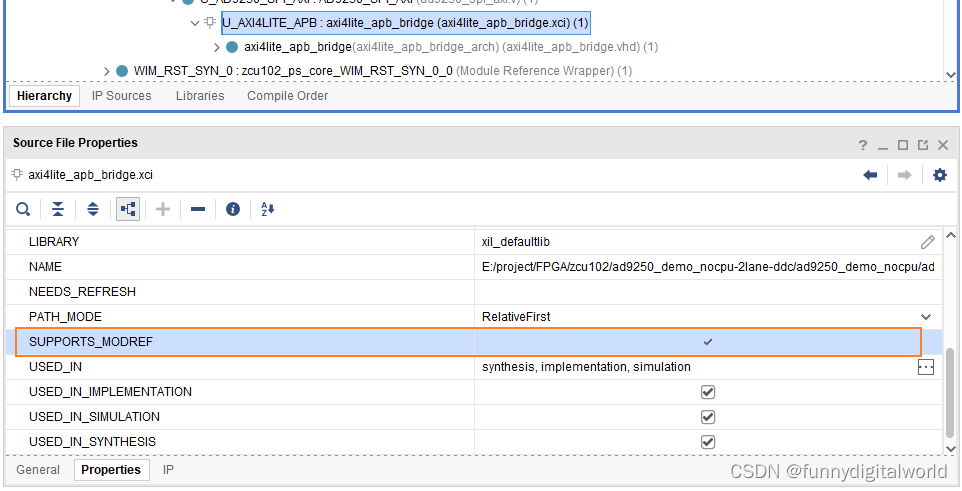

生成的PLL通过代码例化的方式又加到Block Design中,PLL不支持这种例化方式。

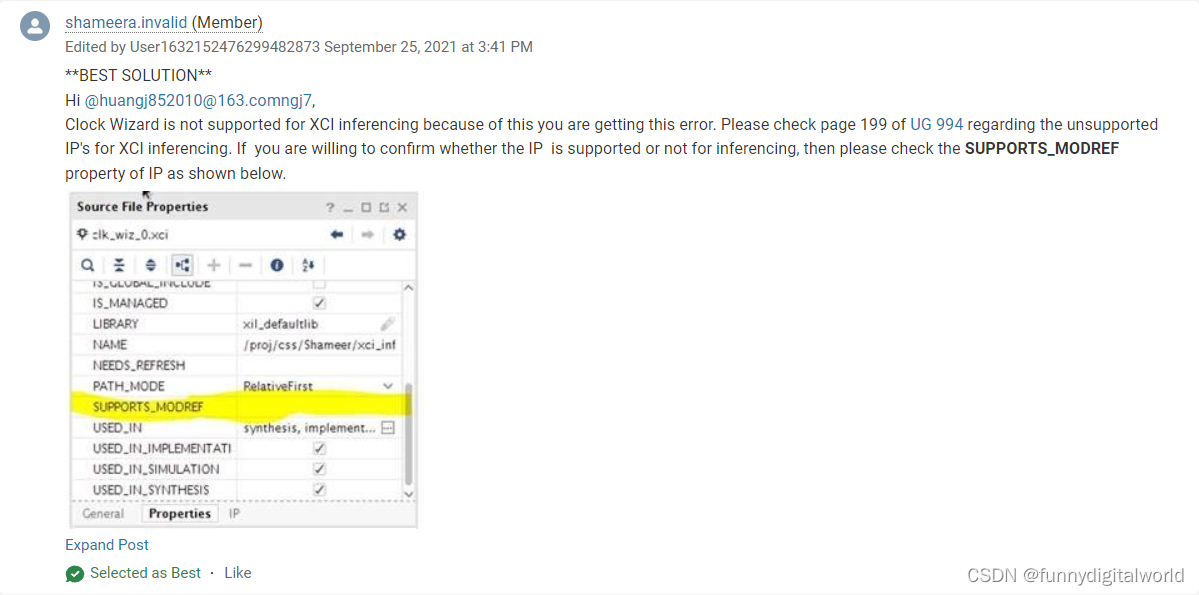

参考 : https://support.xilinx.com/s/question/0D72E000006cLfRSAU/detail?language=en_US

查看IP的SUPPORTS_MODREF属性,打钩情况下才可以支持这种例化方式。

解决方法

将例化PLL的代码打包成IP,再通过IP的是否加入Block Design中。

4004

4004

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?