半加器

半加器可以实现一位二进制的加法运算

A,B为一位二进制输入,C为向高位的进位,S为本位的输出

真值表为

| A | B | C | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

C=A&B S=A^B(异或)

代码为

module h_adder(A,B,S,C);

input A,B;

output S,C;

assign S=A^B;

assign C=A&B;

endmodule一位全加器

C:来自低位的进位, Ci:向高位进位 S:当前位的输和

| C | A | B | Ci | S |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Ci=AB+BC+AC; S=A^B^C (^异或的意思)

代码为

module add_full(A,B,C,Ci,S);

input A,B,C;

output S,Ci;

assign S=A^B^C;

assign Ci=(A&B)|(B&C)|(A&C);

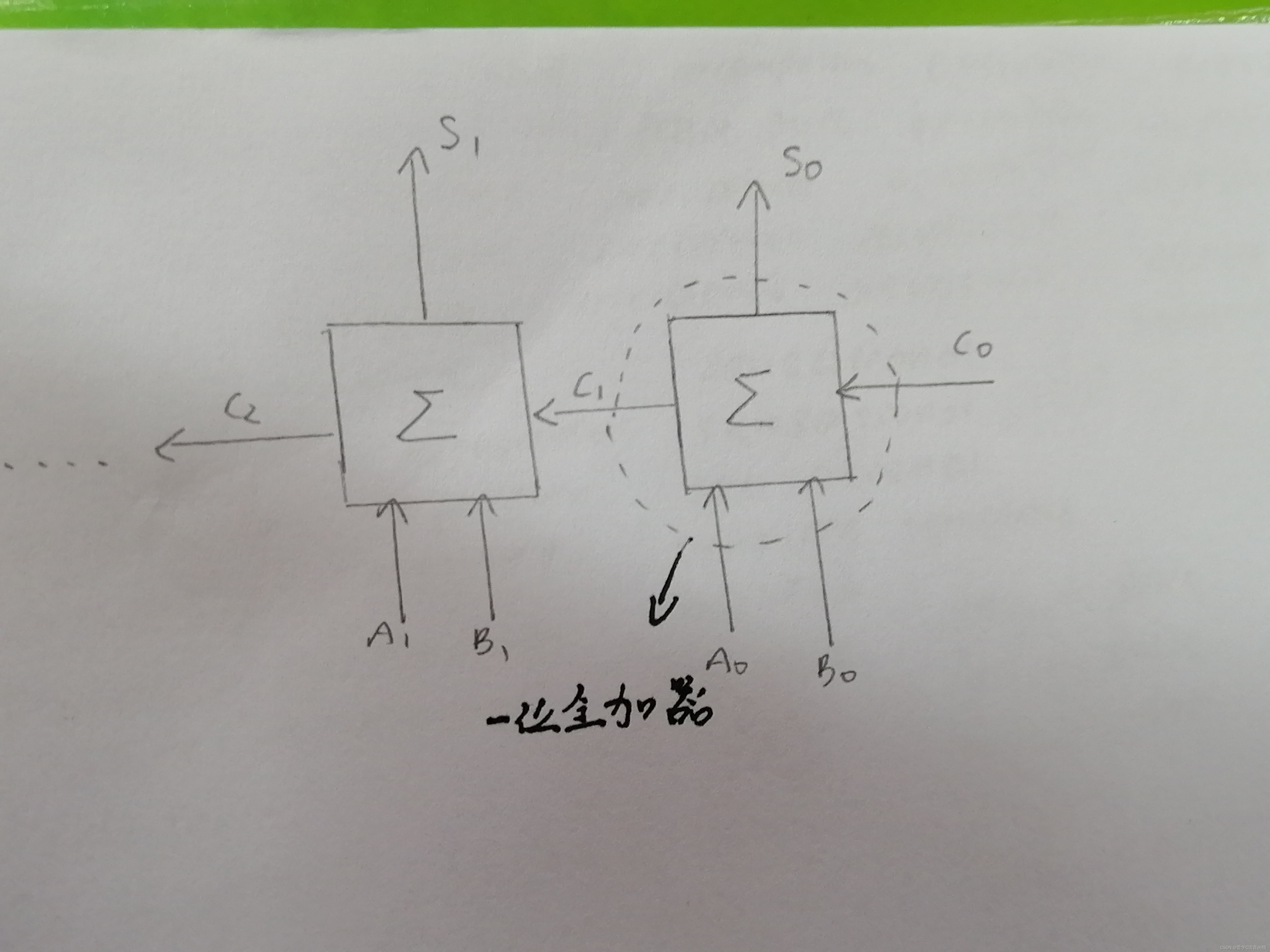

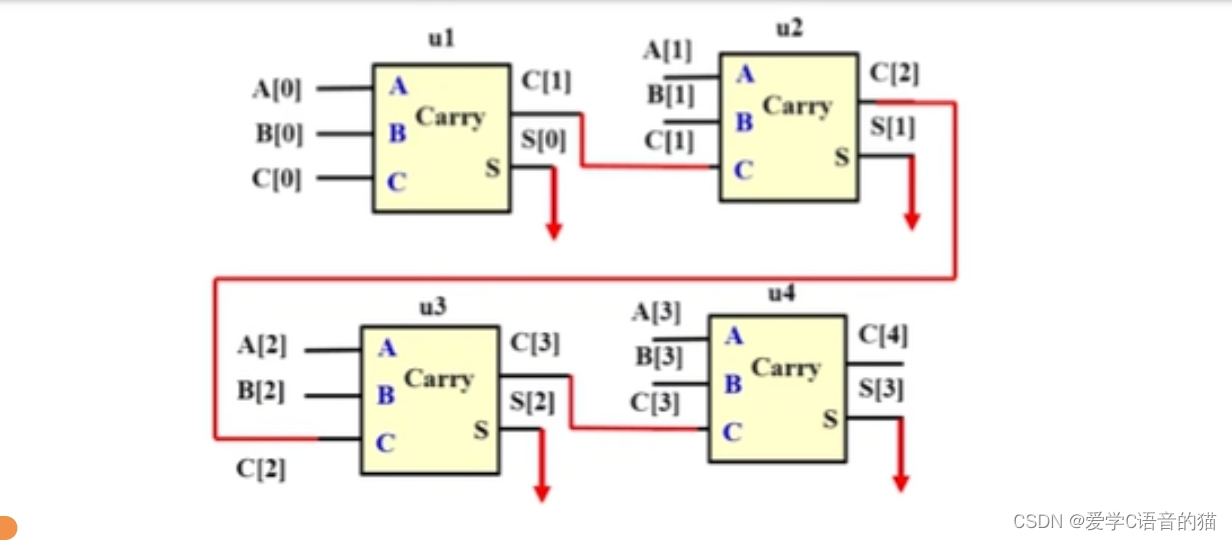

endmodule一位全加器例化成四位全加器

假设A=A0A1A2A3, B=B0B1B2B3

由图可见,四位全加器有四个一位全加器构成,一位全加器构成底层模块,四位全加器调用每一位全加器构成顶层模块

代码为

module add_full4(A,B,C,S);

input [3:0] A,B;

output [3:0] S;

output [4:0] C;

add_full u1(A[0],B[0],c[0],C[1],S[0]),

u2(A[1],B[1],c[1],C[2],S[1]),

u3(A[2],B[2],c[2],C[3],S[2]),

u4(A[3],B[3],c[3],C[4],S[3]);

endmodule例化的语法详细见 黄继业,潘松EDA技术使用教程Verilog 第六版P72,P73页

具体连线如图·所示

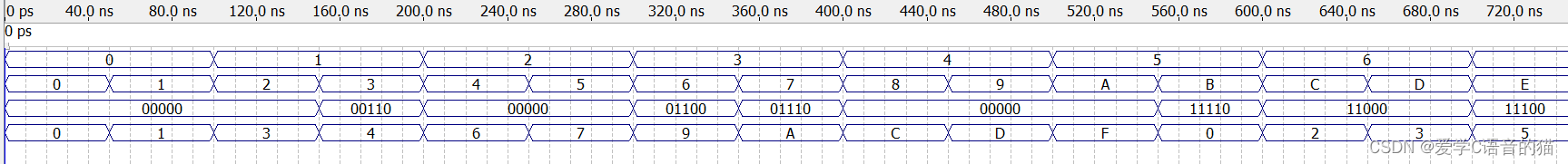

仿真图

6657

6657

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?