视频链接

时钟电路设计

晶振是数字电路的心脏,数字电路需要一个稳定的工作时钟信号,时钟电路至关重要!

1、晶振概述

晶振一般指晶体振荡器。晶体振荡器是指从一块石英晶体上按一定方位角切下薄片(简称为晶片),石英晶体谐振器,简称为石英晶体或晶体、晶振;

而在封装内部添加IC组成振荡电路的晶体元件称为晶体振荡器。其产品一般用金属外壳、玻璃壳、陶瓷或塑料封装。

2、晶振的工作原理

石英晶体振荡器是利用石英晶体的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片,在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了石英晶体谐振器,简称为石英晶体或晶体、晶振。

若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应。

3、晶体振荡器的分类

电脑中的晶体振荡器分为无源晶振和有源晶振两种类型。

无源晶振与有源晶振的英文名称不同,无源晶振为 crystal(晶体),而有源晶振则叫做 oscillator(振荡器)。

晶体是有2个引脚或者4个引脚的无极性元件,需要借助于时钟电路才能产生振荡信号,自身无法振荡起来;有源晶振有4个引脚或者6个引脚,是一个完整的振荡器,其中除了石英晶体外,还有晶体管和阻容元件,因此体积较大。

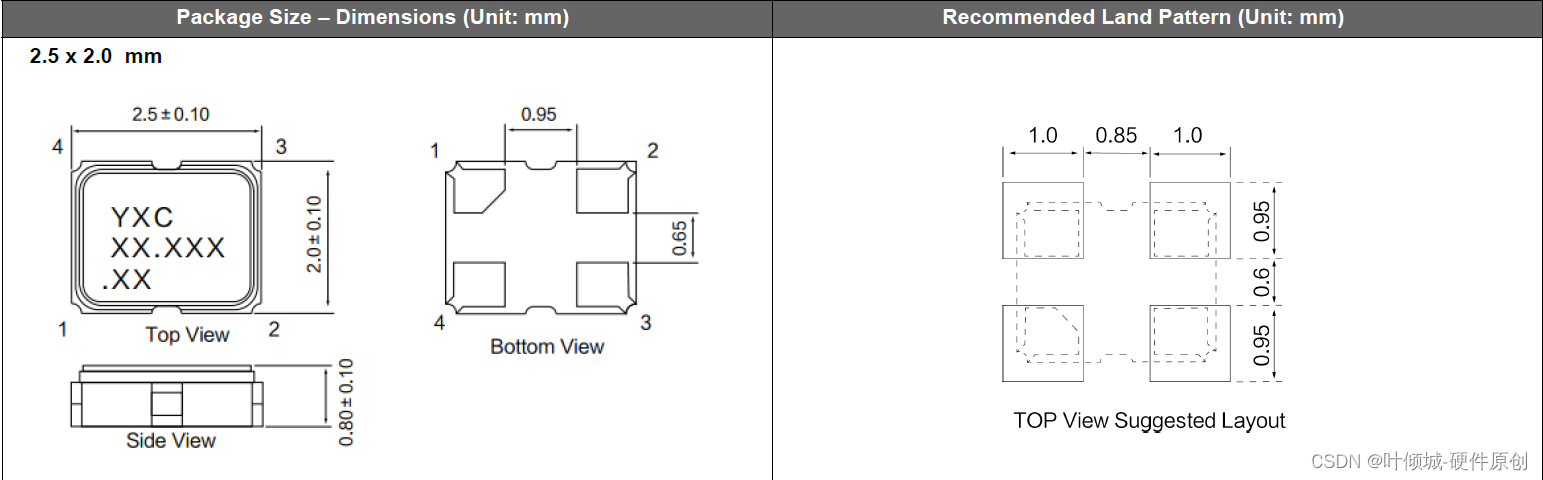

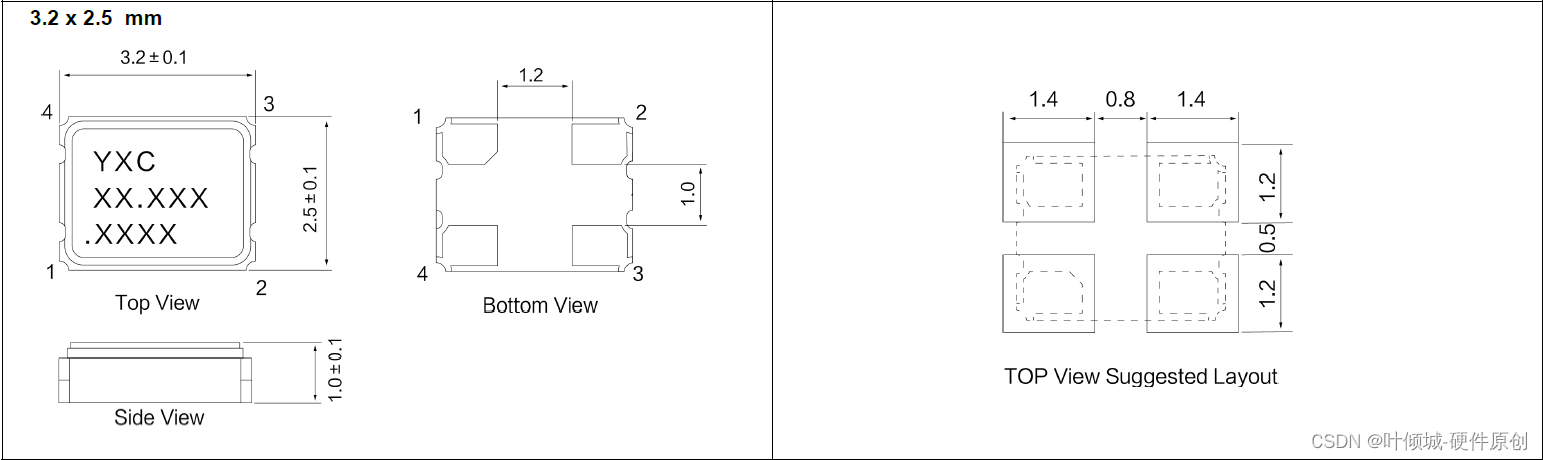

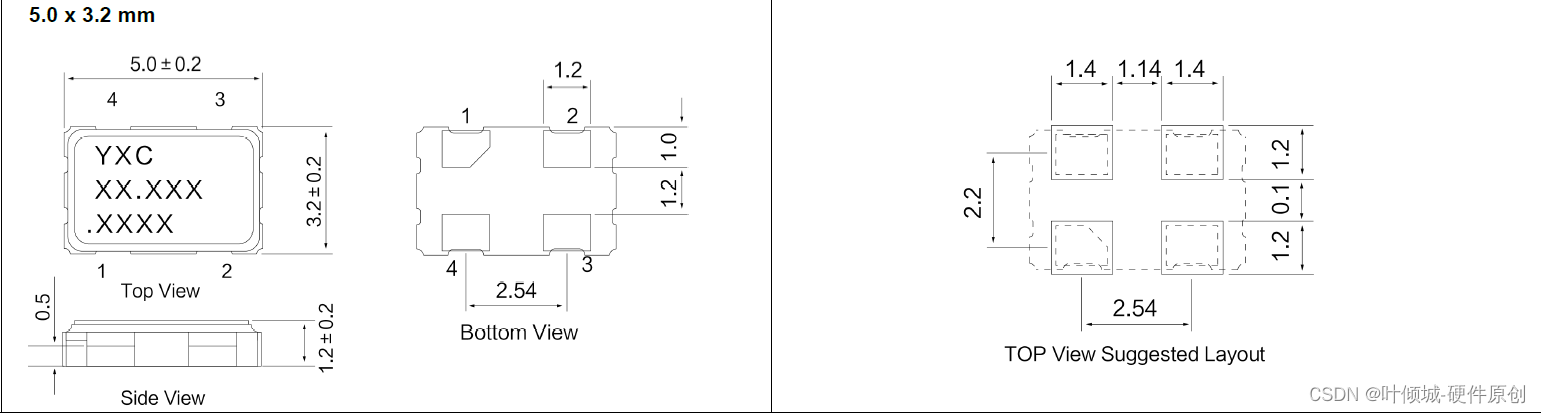

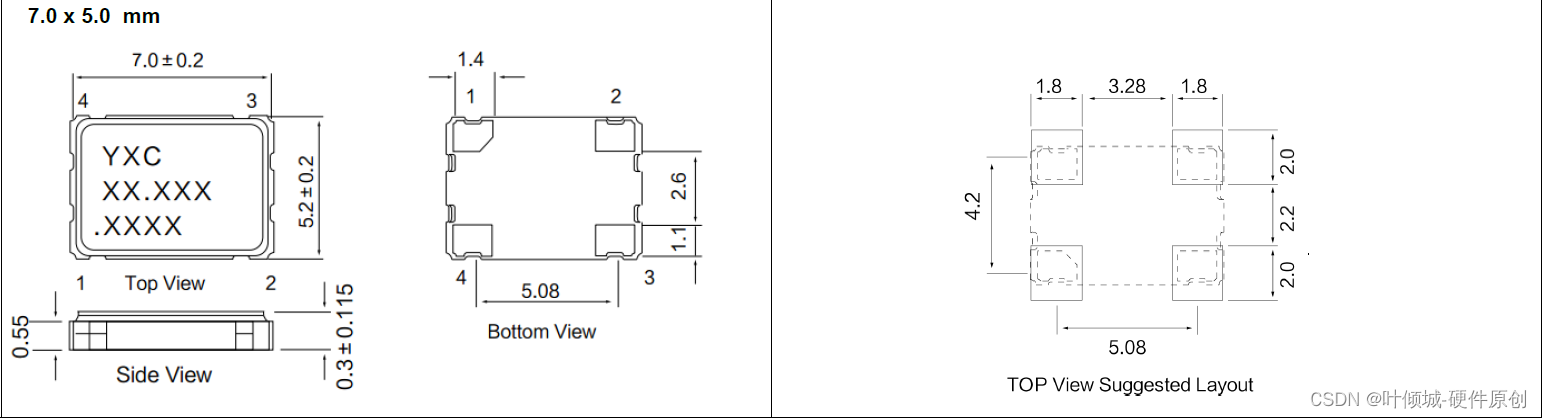

四角的晶振一般有2520贴片晶振,3225贴片晶振,5032贴片晶振。

4、有源晶振

有源晶振分为单线晶振和差分晶振;也可以说是4脚晶振和6脚晶振。

四脚有源晶振通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。

六脚的晶振基本上带一对差分时钟。

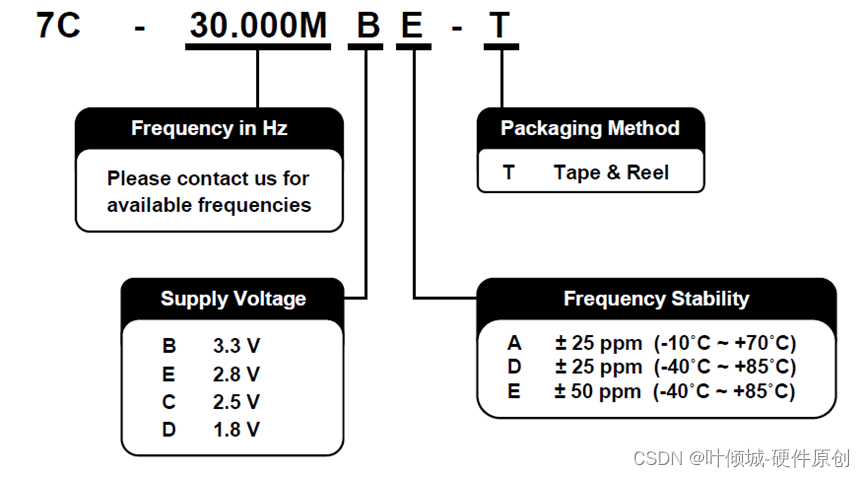

5、晶振的参数

1、负载电容值:选择与负载电容值相等的并联电容,就可以得到晶振标称的谐振频率。

2:关键参数,高端晶振可以达到10-9级别。指在规定的工作温度范围内,与标称频率允许的偏差,用PPm(百万分之一)表示。一般来说,稳定度越高或温度范围越宽,价格越高。对于频率稳定度要求±20ppm或以上的应用,可使用普通无补偿的晶体振荡器。对于介于±1至±20ppm的稳定度,应该考虑温补晶振TCXO。对于低于±1ppm的稳定度,应该考虑恒温晶振OCXO。

6、晶振电路中如何选择电容 C1,C2

7、时钟电路设计要点(★)

7.1、FPGA的顶层设计中模块化的时钟大小如何确定?

1、接口类

2、系统内部

7.2、FPGA设计要点:时钟树

7.3、晶振电路选型注意点

1、频率大小:频率越高,价格越高。频率越高,频差越大,从综合角度考虑,一般工程师会选用频率低但稳定的晶振,自己做倍频电路。总之频率的选择是根据需要选择,并不是频率越大就越好。要看具体需求。

2、频率稳定度:ppm

3、电源电压:常用的有1.8V、2.5V、3.3V、5V等。

4、输出:根据需要采用不同输出。(HCMOS,TTL,PECL,LVDS,LVHCMOS 等)每种输出类型都有它的独特波形特性和用途。对称性、上升和下降时间以及逻辑电平对某些应用来说也有具体要求。

8、原理图硬件实战

8.1 单片机晶体参考

8.2 XC7A100T的电路参考

有源差分晶振

(1)200Mhz差分时钟

下图为200Mhz差分有源晶振实物图

(2)125Mhz差分时钟

125M有源差分晶振电路,此时钟是给FPGA内部的GTP模块提供的参考输入时钟。

8.3 有源晶振的EMC设计

8.4 ZYNQ板级硬件实战

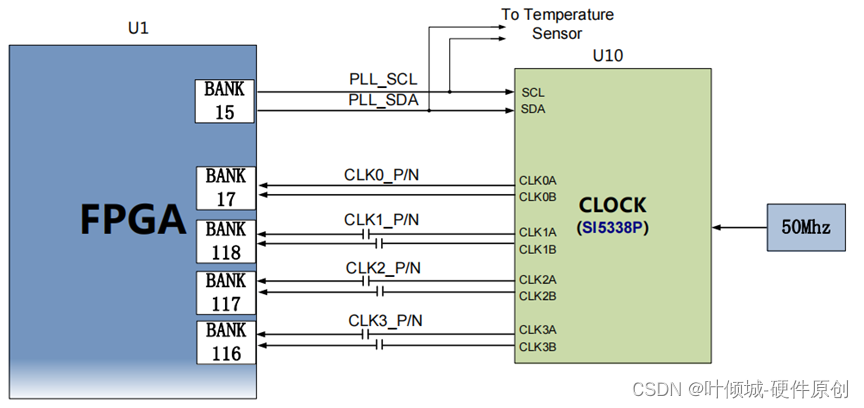

8.5 K7板级硬件实战(可编程时钟源Si5338)

8.6 K7的电路参考(可编程时钟源TI-CDCM61002)

8.7 RTC实时时钟

RTC的英文全称是Real-Time Clock,翻译过来是实时时钟芯片。

RTC芯片是一种能提供日历/时钟(世纪、年、月、时、分、秒)及数据存储等功能的专用集成电路。

晶体的作用:提供基准频率。

RTC的晶体:任何实时时钟的核心都是晶振,晶体频率为32.768kHz。

它为分频计数器提供精确的与低功耗的实基信号。它可以用于产生秒、分、时、日等信息。为了确保时钟长期的准确性,晶体必须正常工作,不能够收到干扰。

2、32768Hz=215即分频15次后为1Hz,周期=1s。

8.7.1 RTC实时时钟 SD3068

8.7.2 RTC实时时钟 PCF8563

8.7.3 RTC实时时钟 PCF8523

8.7.4 RTC实时时钟 DS1302

9 PCB设计要点

1、在PCB设计时,晶振的外壳必须接地,可以防止晶振的向往辐射,也可以屏蔽外来的干扰。

2、晶振下面要铺地,可以防止干扰其他层。

3、晶振底下不要布线,周围5mm的范围内不要布线和其他元器件,防止晶振干扰其他布线和器件。

4、晶振不要布在板子的边缘,板卡的边缘常常是有很多线缆,当线缆穿过晶振和参考接地板的电场是,线缆被干扰了。而晶振布在离边缘远的地方,晶振与参考接地板的电场分布被PCB板的GND分割了,分布到参考接地板电场大大减小了。

5、时钟线尽量要短。

1709

1709

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?