视频链接

USB HOST & SLAVE & OTG电路设计_哔哩哔哩_bilibili

USB HOST & SLAVE & OTG电路设计

1、USB HOST & SLAVE & OTG基本介绍

USB设备,从物理上的逻辑结构来说,包含了主机Host端和设备Device端。其中,主机Host端,有对应的硬件的USB的主机控制器Host Controller,而设备端,连接的是对应的USB设备。

1.1、USB HOST

USB HOST即USB主机,一般是PC机主机,实现控制功能,也可以存取数据,如电脑PC。USB HOST主机只可以和USB Slave设备连接。

1.2、USB SLAVE

USB Slave即USB设备,是从设备,属于被控制设备,可输入输出数据,如U盘、移动硬盘、鼠标、键盘、游戏手柄、打印机、读卡器等USB设备。

1.3、USB OTG

USB OTG全称是USB On-The-Go(正在进行中的意思),同时具备USB主机和USB设备的功能,属于直接控制和传输设备,既可以做USB HOST也可以做USB Slave,一般通过ID信号来控制主、从切换。

USB OTG接口可以通过检测USB_VBUS、USB_ID信号,配置为Host或者Device功能,支持USB2.0/1.1规范。

对于Host端,只需将连接线的USB_ID pin和地短接即可。

对于Slave端,USB连接线的USB_ID pin是悬空的。(设备内部上拉)。

USB HOST 与 USB OTG的区别:由软件进行强制切换或者由硬件即USB ID决定

2、USB2.0 速度识别(★)

USB设备低速,高速硬件检测机制及断开过程 - USB中文网 (USB中文网)

USB 2.0通过上下拉的电阻配置来识别低速、全速和高速。

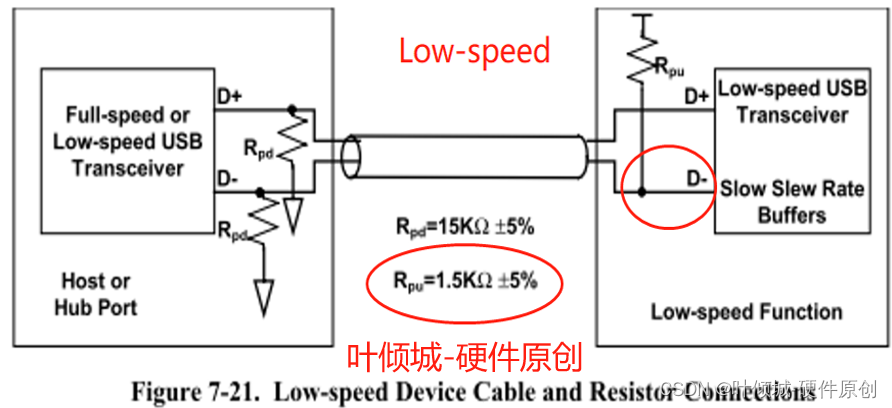

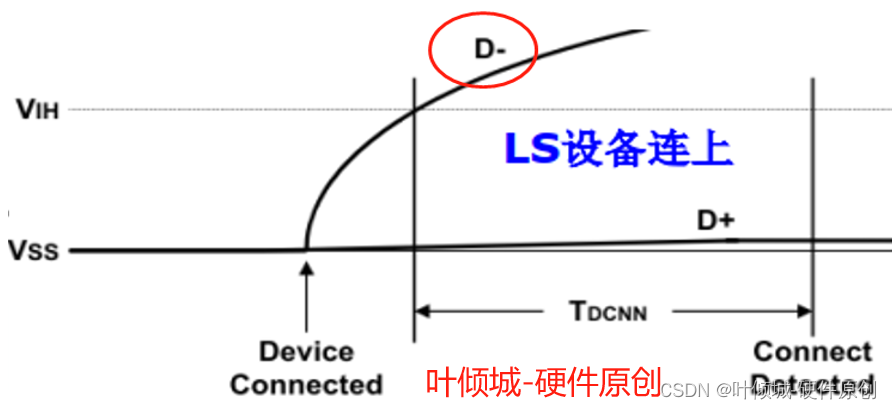

2.1、低速USB的识别

//注意:上拉电阻都是接3.3V的电平//

低速USB设备的连接

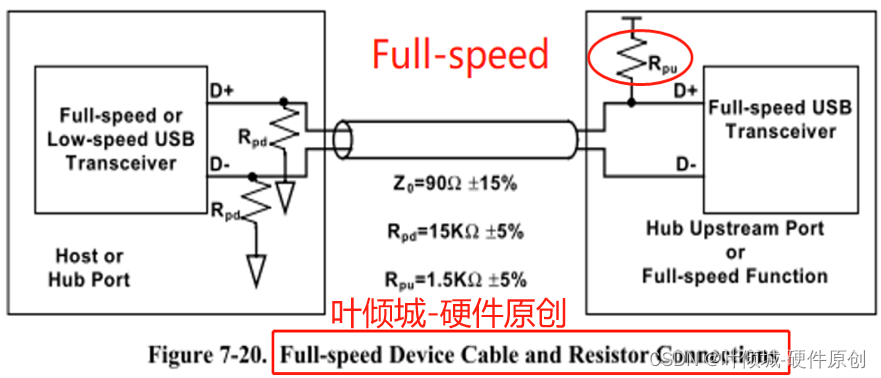

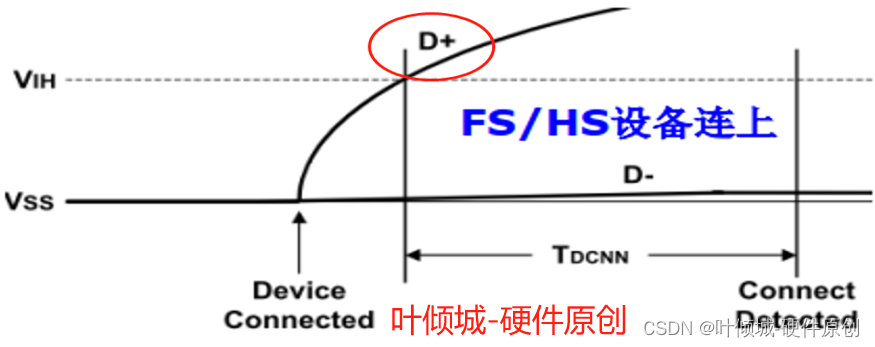

2.2、全速和高速USB的识别

全速/高速USB设备的连接

2.3、USB设备速度的检测流程

2.4、基于速度识别实战电路注意事项

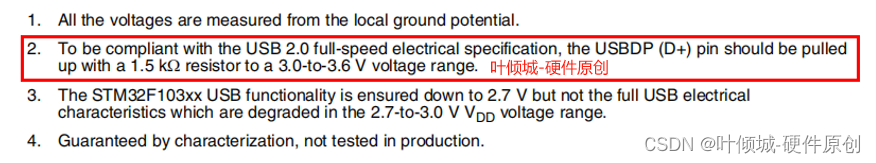

1、STM32F103系列的芯片只能做“USB DEVICE”,STM32F105和STM32F107系列才可以做“USB OTG”。

2、USB的差分信号。在USB HOST端,D+、D-各接一个15kohm的下拉电阻。

而在USB DEVICE端,这时就有高速低速设备的区别了。USB1.0、1.1、2.0协议中都有定义高低速设备以满足不同情况的需求,这些在硬件上的区别就是:

高速设备:D+接一个1.5K的上拉电阻到3.3V,D-不接;

低速设备:D-接一个1.5K的上拉电阻到3.3V,D+不接;

3、在高速USB传输时,需要考虑信号的完整性问题,即阻抗匹配。

3、USB ESD接口保护电路

USB接口支持设备的即插即用和热插拔功能。在USB接口添加静电保护器件可有效提高 USB接口的静电防护等级,降低USB端口的故障率,防止静电对USB 接口造成损害。

注意:硬件实战,需看器件手册再决定,不同版本的USB ESD保护器件。

3.1、静电防护等级

接触放电8kV以上,空气放电15kV以上

3.2、ESD的结电容

减少对USB信号的干扰。

USB1.1:ESD保护器件的结电容小于10pF。

USB2.0:ESD保护器件的结电容小于4pF。

USB3.0:ESD保护器件结电容小于0.8pF。

USB3.1 Type C:ESD保护器件结电容小于0.4pF。

3.3、注意ESD保护芯片支持的速率

注意看器件手册,支持哪个版本的USB,基本上手册中提到的,问题基本不大。

反应速度快(0.5ns~1ns)、很小的漏电流(1μA)以减小电源的损耗

4、经典的USB3320、TUSB1210BRHB(参考第35课) (★)

USB3320是一款高度集成的全功能高速USB 2.0 ULPI收发器, 基于ULPI接口,可以作为host、slave、OTG。(已详解)

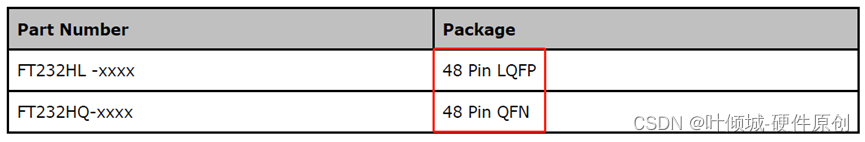

5、飞特帝亚(FTDI)---FT232HL (★)

随着FT232H USB2.0高速芯片的发布,英商飞特蒂亚公司(FTDI)进一步巩固了其在USB接口集成电路产品的地位。此款多功能的单通道USB转UART/FIFO接口设备可通过EEPROM配置为各种不同的串行或并行接口。与FTDI建设完备精良的USB设备驱动一起,这套方案使工程师可以轻松的将高速 USB连接引入新的和传统的外设设计中。

特色:

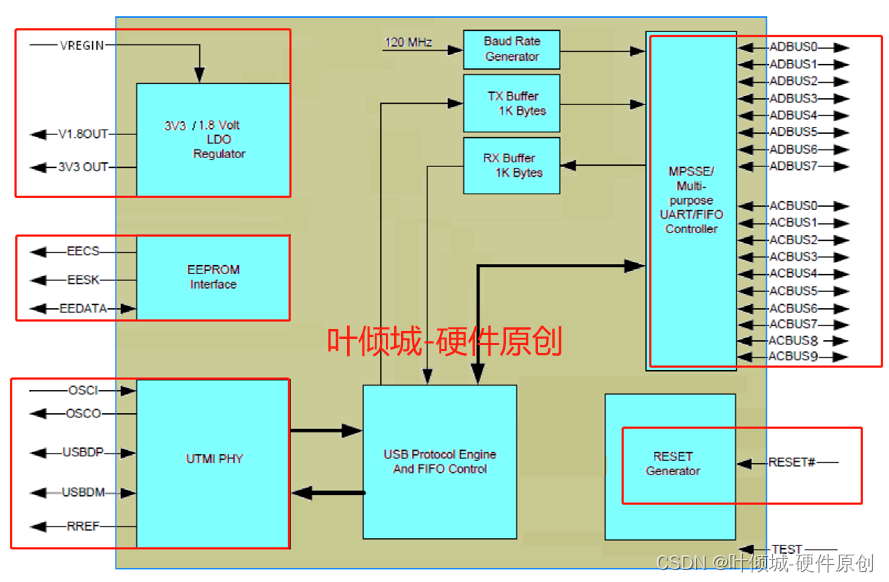

1、可以实现USB到两个串行UART、FIFO、Bit-Bang IO接口,并且还可以配成MPSSE(多协议同步串行引擎),I2C,JTAG及SPI总线。

2、芯片内部整合了上电复位电路,节约成本。

3、集成的1.8V和3.3V低压差稳压器减少了所需外部元件。

4、通过外挂的EEPROM,用于IO配置及储存USB VID和PID。

5、提供各种操作系统下的驱动程序,如Windows OS,Mac OS,WindowsCE,Linux。

5.1、结构及功能框图

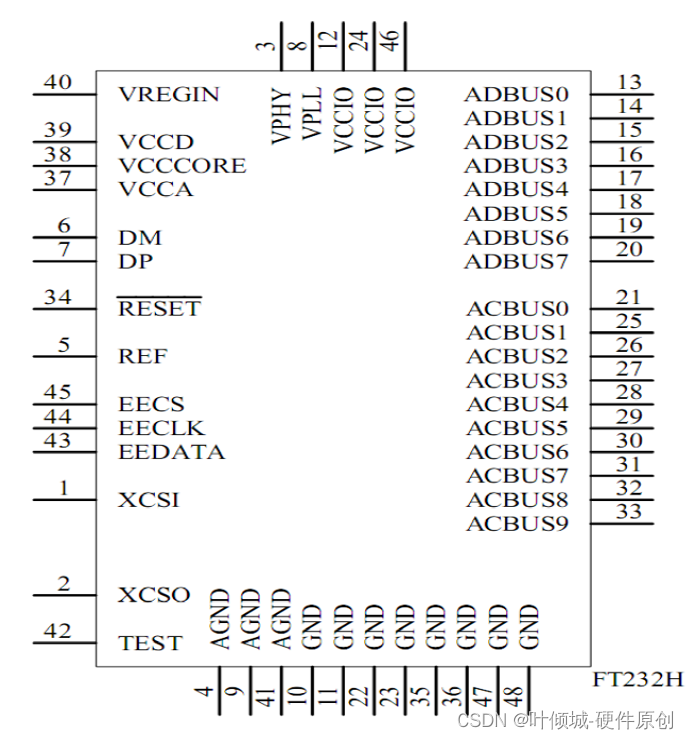

5.2、管脚定义

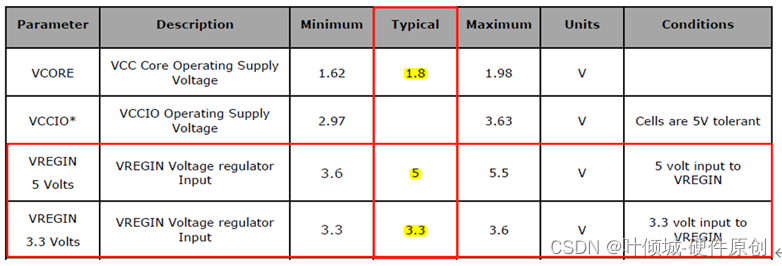

5.2.1 Power and Ground

| 管脚符号 | 类型 | 描述 |

| VREGIN | **POWER /input | +5.0V or 3V3 power supply input. |

| VCCD | **POWER output or input | +3.3V output or input. |

| VCCA | POWER/output | +1.8V output. Should not be used. |

| VCORE | POWER/output | +1.8V output. Should not be used. |

| VCCIO | POWER/input | +3.3V input.I/O interface power supply input |

| VPLL | POWER/Input | +3.3V input. Internal PLL power supply input. It is recommended that this supply is filtered using an LC filter. 3.3V输入。内部PLL电源输入。建议使用LC过滤器过滤该电源。 |

| VPHY | POWER/Input | +3.3V input. Internal USB PHY power supply input. Note that this cannot be connected directly to the USB supply. A +3.3V regulator must be used. It is recommended that this supply is filtered using an LC filter. 3.3V输入。内部USB PHY电源输入。请注意,这不能直接连接到USB电源。A 3.3V调节器必须使用。建议使用LC过滤器过滤该电源。 |

| AGND | POWER/Input | 0V Ground input. |

| GND | POWER/Input | 0V Ground input. |

5.2.2 Common Function pins

| 管脚符号 | 类型 | 描述 |

| OSCI | INPUT | Oscillator input. |

| OSCO | OUTPUT | Oscillator output. |

| REF | INPUT | Current reference – connect via a 12KΩ resistor @ 1% to GND. |

| DM | INPUT | USB Data Signal Minus. |

| DP | INPUT | USB Data Signal Plus. |

| TEST | INPUT | IC test pin – for normal operation must be connected to GND. |

| RESET# | INPUT | Reset input (active low). |

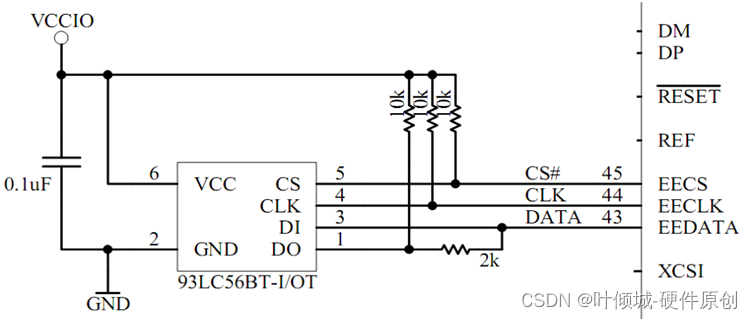

5.2.3 EEPROM Interface Group

| 管脚符号 | 类型 | 描述 |

| EECS | I/O | EEPROM – Chip Select. Tri-State during device reset.芯片选择。设备重置期间三态。 |

| EECLK | OUTPUT | Clock signal to EEPROM. Tri-State during device reset. When not in reset, this outputs the EEPROM clock.向EEPROM发送时钟信号。设备重置期间三态。当不复位时,输出EEPROM时钟。 |

| EEDATA | I/O | EEPROM – Data I/O. Connect directly to Data-in of the EEPROM and to Data-out of the EEPROM via a 2.2K resistor. Also, pull Data-Out of the EEPROM to VCCD via a 10K resistor for correct operation. Tri-State during device reset. EEPROM–数据输入/输出。通过2.2K电阻,直接连接EEPROM的数据输入和数据输出。此外,通过10K电阻器将数据从EEPROM中拉至VCCD,以确保正确操作。设备重置期间三态。 |

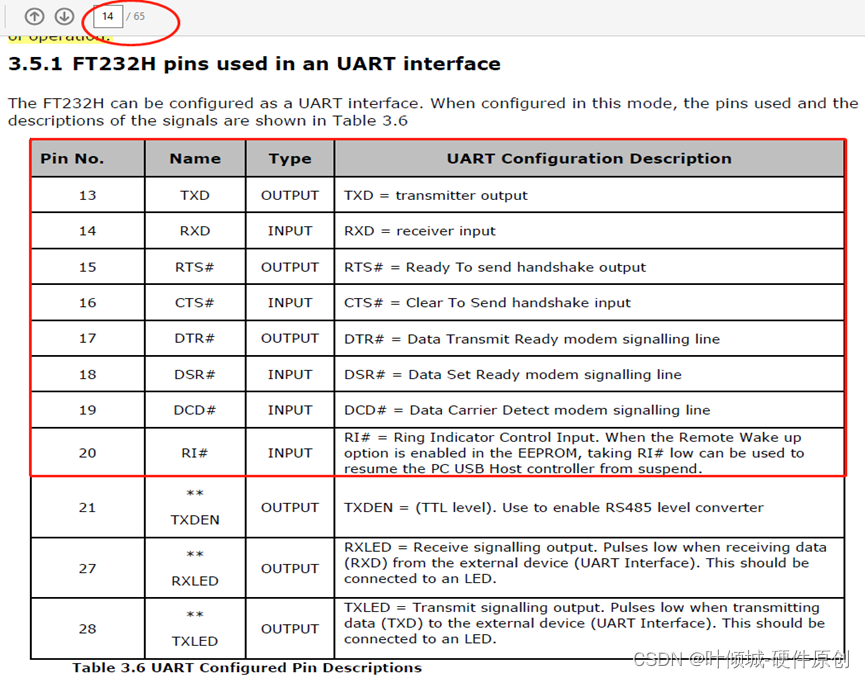

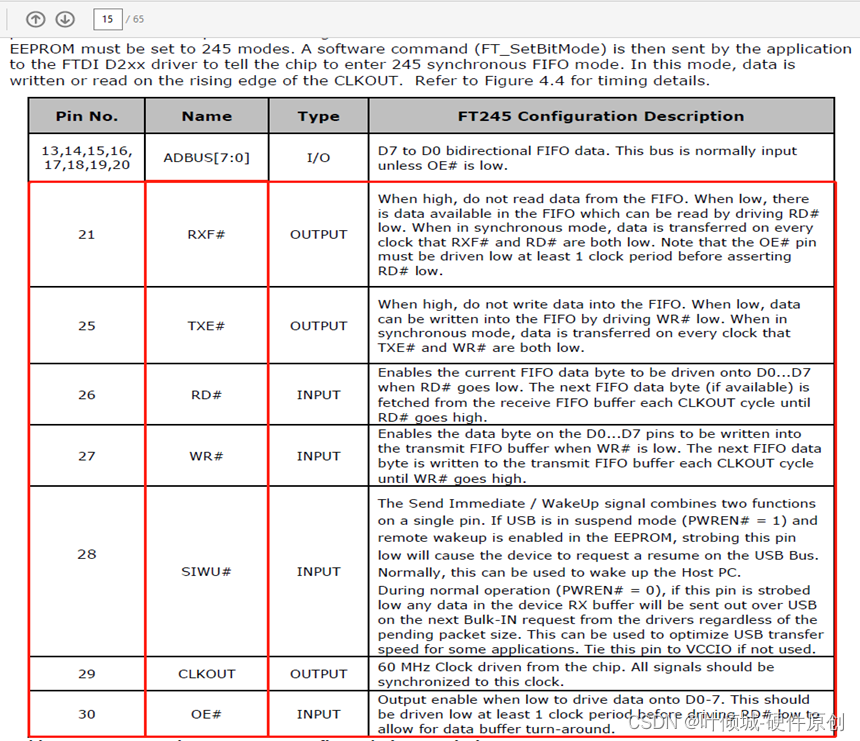

5.2.4 UART Interface and ACBUS Group

| 管脚符号 | 类型 | 描述 |

| ADBUS0 | Output | Configurable Output Pin, the default configuration is Transmit Asynchronous Data Output. (发送数据) |

| ADBUS1 | Input | Configurable Input Pin, the default configuration is Receiving Asynchronous Data Input. (接受数据) |

| ADBUS2 | Output | Configurable Output Pin, the default configuration is Request to Send Control Output / Handshake Signal. (请求发送) |

| ADBUS3 | Input | Configurable Input Pin, the default configuration is Clear To Send Control Input / Handshake Signal. (清除发送) |

| ADBUS4 | Output | Configurable Output Pin, the default configuration is Data Terminal Ready Control Output / Handshake Signal. (数据终端准备) |

| ADBUS5 | Input | Configurable Input Pin, the default configuration is Data Set Ready Control Input / Handshake Signal. (数据准备就绪) |

| ADBUS6 | Input | Configurable Input Pin, the default configuration is Data Carrier Detect Control Input. 数据载波检测 |

| ADBUS7 | Input | Configurable Input Pin, the default configuration is Ring Indicator Control Input. When remote wake up is enabled in the EEPROM taking RI# low can be used to resume the PC USB host controller from suspend. (振铃提示) |

器件手册的P14页同样有相关细节描述!

| ACBUS [0-9] | I/O | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5. |

| PWRSAV# | INPUT | USB Power Save input. |

| ACBUS[7] | I/O | ADBUS[7]就是PWRSAV# |

5.3、三种用法

5.3.1 总线供电配置运行在5V

5.3.2 5V的自供电配置(on 5V)

5.3.3 3.3V的自电配置(on 3.3V)

5.4、设计注意事项

5.5、硬件实战(★)

6、其余设计注意事项

- USB接共模电感(抑制共模干扰),有时候会在上面串一个0欧姆的电阻。(复用)

2、无论是USB2.0或者3.0。ESD保护都是需要的。

本文详细介绍了USBHOST、SLAVE、OTG的基本概念,USB2.0速度识别方法,以及STM32F系列芯片在其中的应用。还涵盖了USB接口的静电保护电路、USBESD接口、经典芯片如USB3320和FT232HL的特性,以及设计注意事项和实战技巧。

本文详细介绍了USBHOST、SLAVE、OTG的基本概念,USB2.0速度识别方法,以及STM32F系列芯片在其中的应用。还涵盖了USB接口的静电保护电路、USBESD接口、经典芯片如USB3320和FT232HL的特性,以及设计注意事项和实战技巧。

5708

5708

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?