Verilog编程基础练习

-

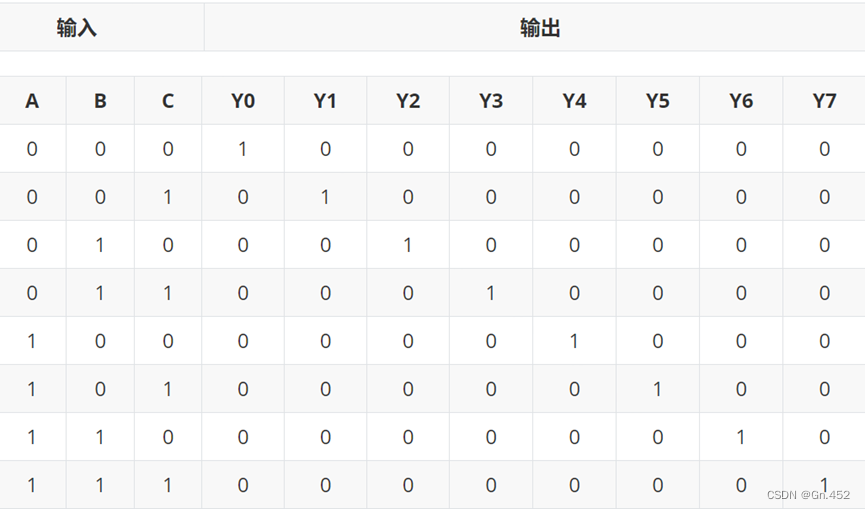

首先使用Logsim绘制一个3-8译码器电路图,列出3-8译码器的逻辑真值表。

-

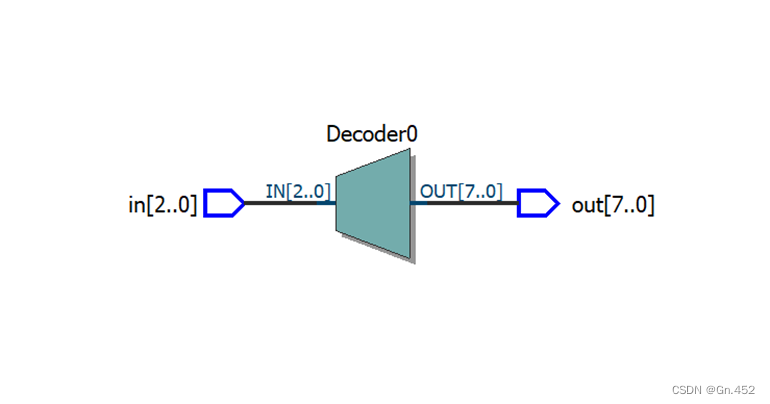

然后采用Verilog编程(if-else或者case)设计一个3-8译码器,生成RTL原理电路图;

-

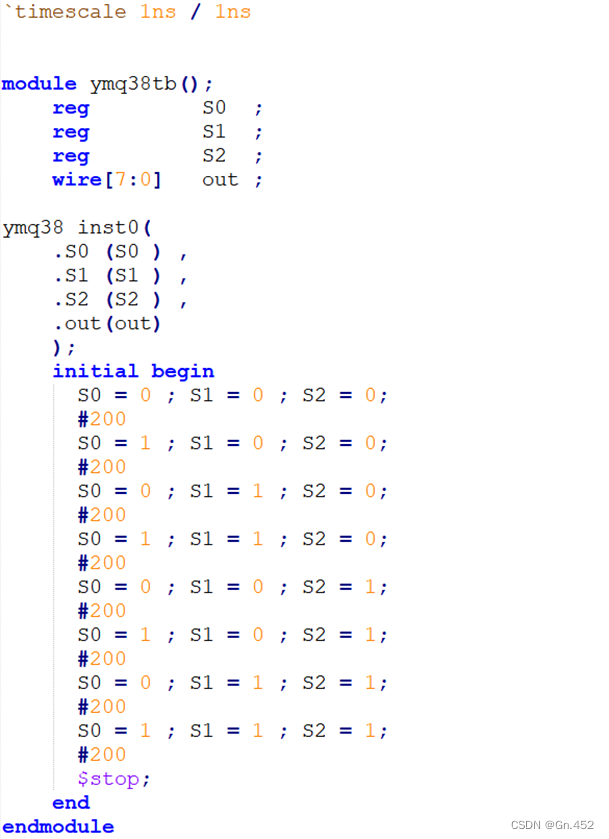

编写一个仿真测试文件,对3-8译码器进行仿真测试,输出结果(参考附件或网上资料)。

(仿真测试)

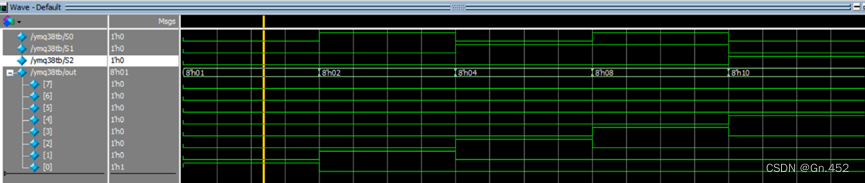

(2)modelsim仿真波形图

- 分析并回答下列问题:

1)Verilog 综合生成的3-8译码器电路原理图与原始设计电路存在什么差异? 仿真测试生成的结果是否与真值表一致?

答:生成的电路图已经把原始设计的中间电路综合简化为一个模块。结果一致。

2) Verilog代码设计的3-8译码器模块的输出信号 为何要定义为 reg类型而不用默认wire(导线)类型?改成wire型是否可以? (即是否可以把 output reg [7:0] out 改为 output [7:0] out) 修改后会出现什么错误?为什么会出错?

答:wire型数据常用来表示以assign关键字指定的组合逻辑信号。模块的输入输出端口类型都默认为wire型。reg型表示的寄存器类型。always模块内被赋值的信号,必须定义为reg型,代表触发器。而我们上面使用的输出信号是在always模块内被赋值所以使用reg类型而非wire类型。删掉output reg 中的reg后会被默认位wire类型,但wire可以有多个驱动器,reg只能有一个,因此会报错。

然后用Verilog的门级描述方式写一个“1位全加器”, 生成RTL电路,与Logsim的“1位全加器”进行对比。在下面这个Verilog门级电路实现时不是按照之前的logsim电路图来描述的是按照用三个与门的全加器实现的全加器来描述的。

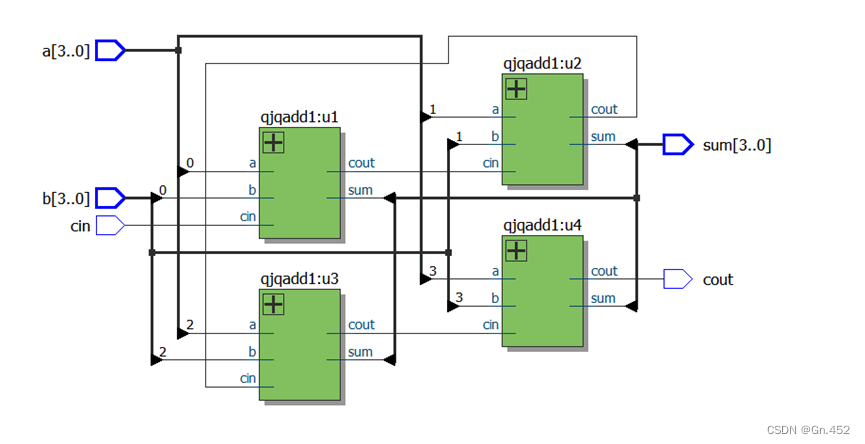

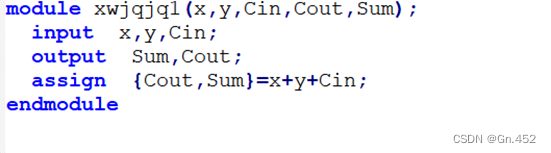

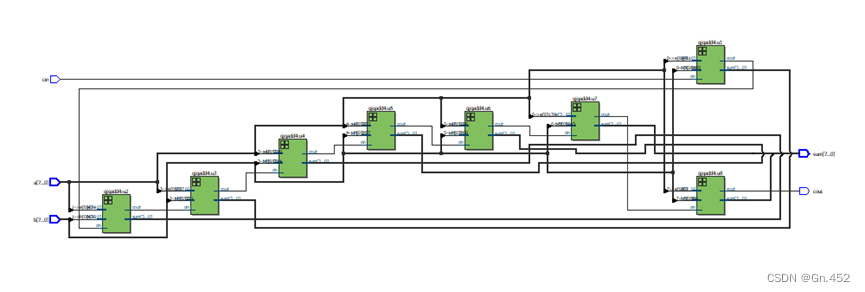

- 采用Verilog模块调用子模块的方式,用4个上面的“1位全加器”级联方式,构成一个“4位全加器”(即串行全加器),生成RTL电路,与Logsim的“4位全加器”电路进行对比;(Verilog模块调用方式实现4位全加器时已经将前面的一位全加器封装成一个模块)

-

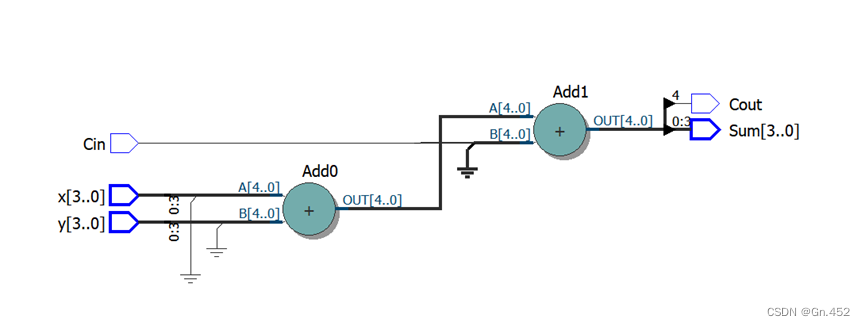

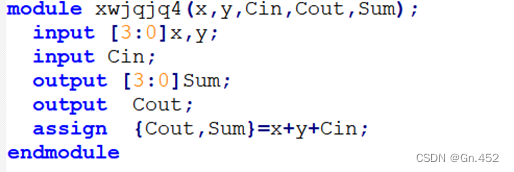

再用行为级描述实现上述两步骤。

一位全加器

四位全加器

-

采用Verilog设计一个8位全加器模块。

-

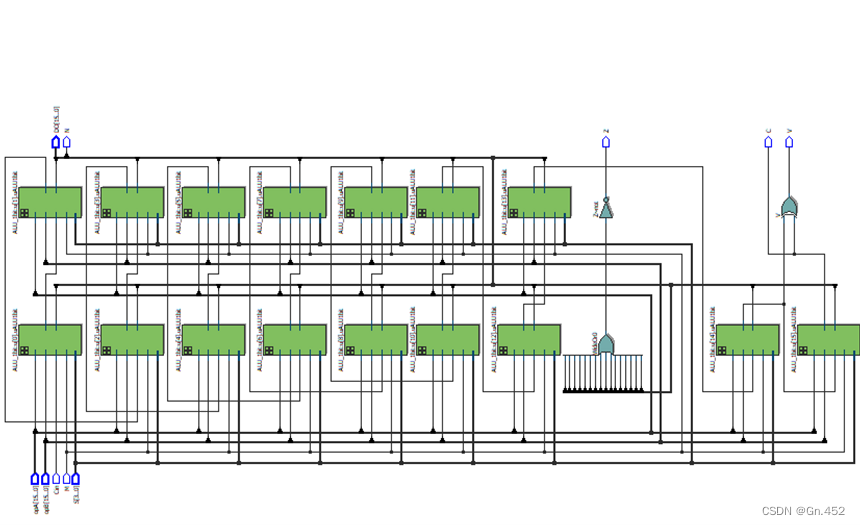

扩展实验(先模仿调试通过,后续再加深理解)。学习教材上的 并行加法器原理(先行进位加法器),参考附件资料,完成一个16位ALU(算术逻辑单元)的电路设计,采用Verilog设计模式,生成RTL电路。

591

591

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?