VIVADO的PLL使用条件限制

一、说明

在vivado构建MMCM/PLL IP核时,因为我输出的时钟个数有点多,频率范围有点宽,然后MMCM就一直报错了。然后借此机会对vivado的MMCM/PLL IP和使用条件和输出范围做一次粗略地研究,然后在此记录。

二、PLL使用限制

1,PLL工作原理

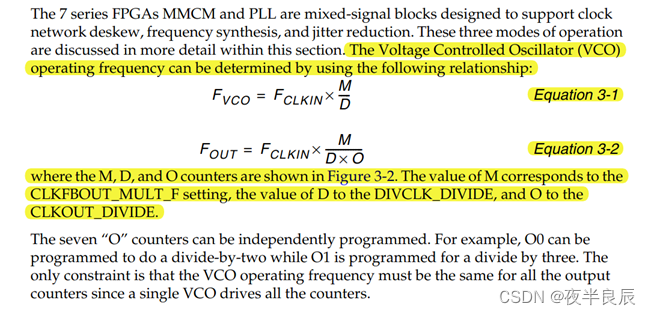

参考文献:ug472

意思就是说:所有的时钟输出都是由VCO分频得到的,VCO的频率为

F

V

C

O

F_{VCO}

FVCO,输入时钟频率为

F

C

L

K

I

N

F_{CLKIN}

FCLKIN,输出时钟频率为

F

O

U

T

F_{OUT}

FOUT。M为倍频系数,D为预分频系数,O为输出分频系数。不同的输出时钟都是因为O不同,所有的输出时钟的M和D是相同的。这个在PLL配置面板上也能看到。

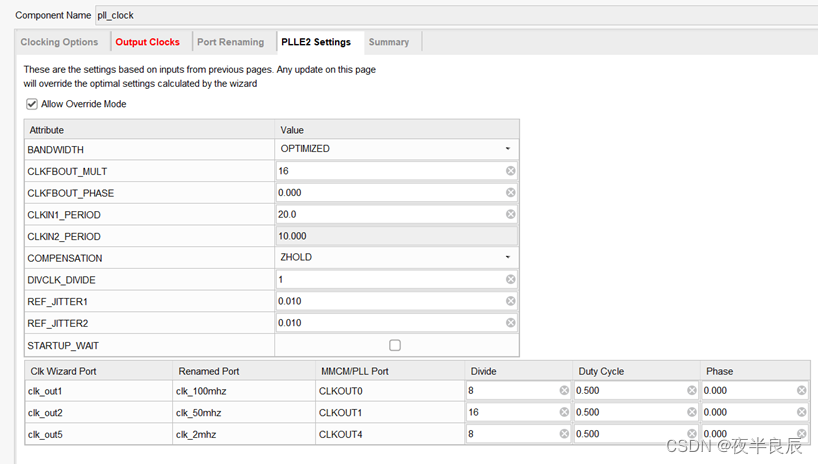

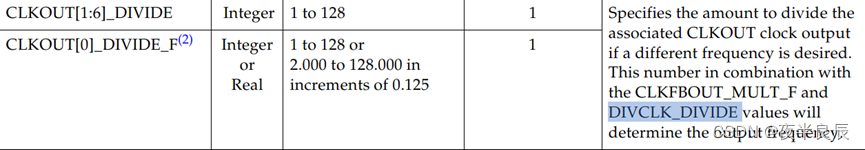

CLKFBOUT_MULT为M,DIVCLK_DIVIDE为D,下边方框里的Devide就是O,可见每个输出时钟的O不相同。

当然如果想自己调整M,D,O,从而调整输出时钟,应当选中Allow Override Mode,要不然无法修改。

2,VCO频率范围和输出频率范围

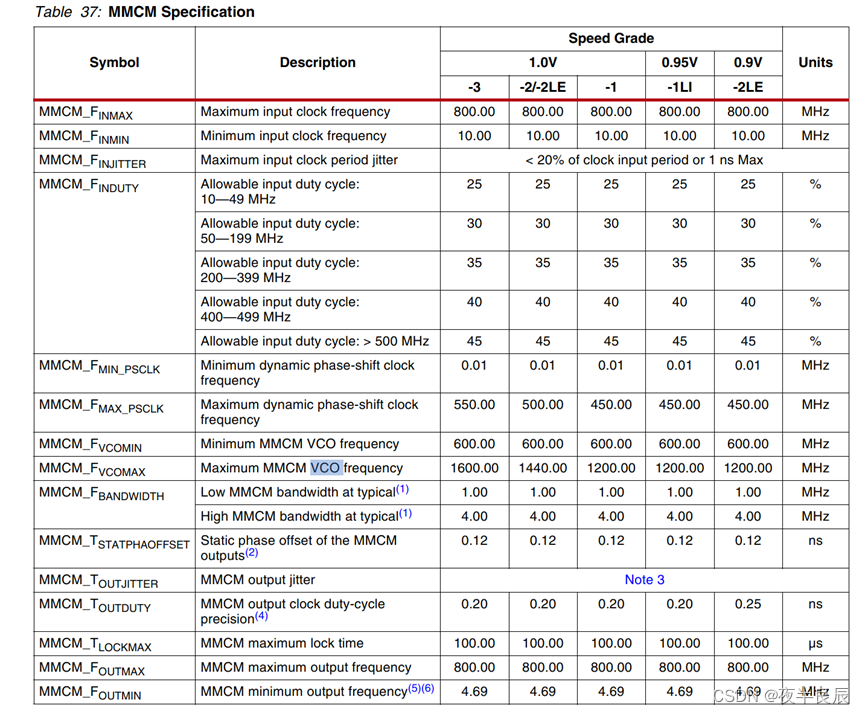

我用的是Artix-7系列,如下表所示

在MMCM模式下,VCO在600MHz ~ 1440MHz,最高频率和fpga速度等级有关,输出时钟在4.69MHz ~ 800Mhz。

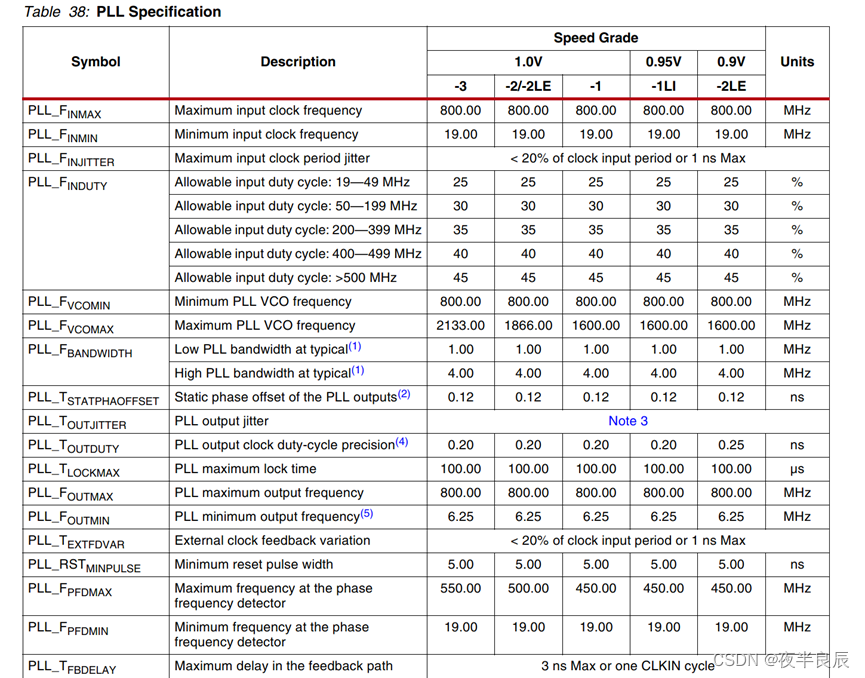

然后在PLL模式下,参数有所不同,如下表所示

参考文献:ds181

PLL的VCO范围为:800MHz ~ 1866MHz,也和速度等级有关。输出时钟频率在6.25MHz~800MHz。

3,输出时钟范围限制的另一个因素

参考文献:ug472

DIVCLK_DIVIDE的范围是1-128,也就是O的范围为1-128。M和D一般没太大关系,但是和VCO频率有很大关系。假设VCO是800MHz。你想分频出来同时分频出来6MHz,7Mhz,8Mhz,9MHz,11Mhz是不可能的,想要分出来这些时钟,就要提高VCO的频率,假设VCO为5544MHz。那么需要O为924才能分频出来6MHz,这样的话就超过了O的范围。所以PLL还是不太灵活。

三、解决方法

目前来看,没有。

不过1-5MHz的低频信号,fpga厂商应该是想让我们尝试用分频器去做,虽然分频器时钟不走全局时钟网络,可能会不稳定。但是因为频率很低,只要做好约束应当还是能用的。但是用了分频器时钟后,信号时延就不太确定,因此要做跨时钟域处理,比如做好数据缓冲这些操作。

高频时钟,一般用不到那么多不同频率的高频时钟,但如果真的用到了也不好说有什么解决办法,如果有多个PLL的话应当可以解决。

5733

5733

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?