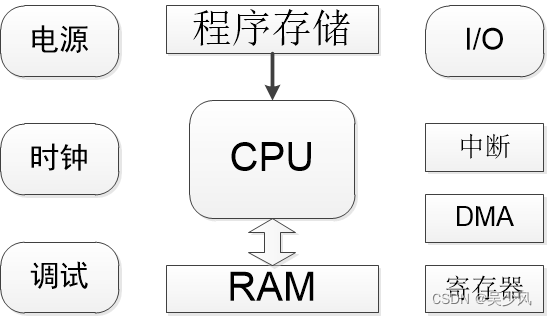

简单MCU

通常,单核的MCU结构简要如下:

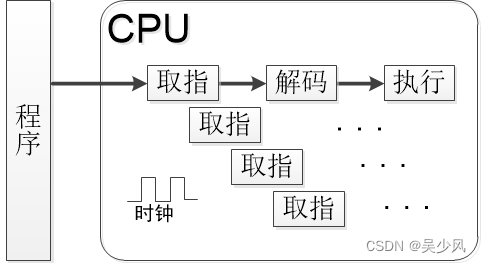

流水线

CPU在时钟的脉动下工作,一个指令需要取指、解码、执行大致3个阶段,至少3个时钟。为了充分利用时间,不是执行结束再取指,而是一边下一步一边取值,这就是流水线。

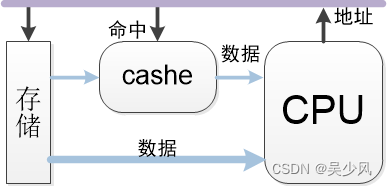

Cashe

通常,外部存储,特别是NVM,速度可能比CPU慢很多,cashe就是解决这个问题的,cashe从外存一次读取一个页面,CPU平常从cashe取指,只有cashe没有的时候才从外存去取,同时cashe也会不断更新自己的页面。

多核

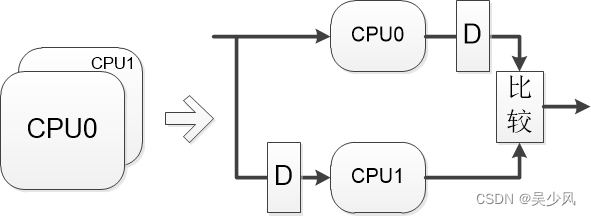

锁步核

下图所示为双核锁步,主CPU0和比较CPU1执行同样的指令,CPU1延时执行,CPU执行结束延时,然后比较。

总线访问

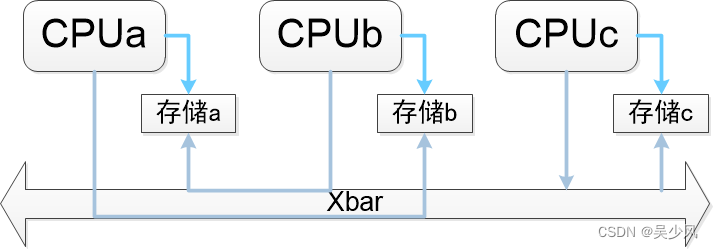

如图,每个CPU都设有本地存储,可以直接访问。除此之外,CPU之间还可以访问系统上其它的资源,这时就会共用一个总线,此时就需要一种总线访问的控制机制。

26262要求

需分析的失效模式

| 要素 | 99%高诊断覆盖率、所需分析的失效模式 | |

| 电源 | 漂移和振荡;过压或欠压;电源尖峰 | |

| 时钟 | 直流故障模型;频率错误;周期抖动 | |

| NVM | 数据、地址、控制总线接口; 控制线和逻辑的直流故障模型 | |

| RAM | 数据、地址、控制总线接口; 控制线和逻辑的直流故障模型; 位存储单元软错误模型 | |

| IO | 直流故障模型;漂移和振荡 | |

| CPU | ALU的数据路径 | 直流故障模型;软错误模型 |

| 寄存器、内部RAM、 地址运算 | 直流故障模型,包括寄存器无寻址、错误寻址、或者多个寻址;软错误模型 | |

| 控制逻辑 | 编码错误、执行错误或者没有执行;无序执行;执行过快或者过慢;堆栈溢出 | |

| 中断处理 | 遗漏或者连续的中断;执行了错误的中断;错误的优先级; 缓慢或干扰中断处理导致丢失或延误的中断服务 | |

| 配置寄存器 | 寄存器损坏;卡滞故障模型 | |

| 其它 | 直流故障模型;软错误模型 | |

| 通信 | 片上通信; 含总线仲裁 | 直流故障模型(数据控制, 地址和仲裁信号);超时; 没有或者持续不断或者错误的仲裁;软错误 |

| 数据传输 | 通信节点失效;消息损坏;消息延迟;消息丢失;非预期消息重复;顺序错误;消息插入;伪消息 | |

安全措施

| 安全措施 | 覆盖率 | 备注 | |

| CPU | 硬件支持的自检 | 中 | 取决于自检质量 |

| 软件自检 | |||

| 单硬件通道软件多样化冗余 | 高 | 取决于冗余质量。共模失效会降低诊断覆盖率 | |

| 硬件冗余(双核锁步、非对称冗余、编码处理) | |||

| 软件比较 | 高 | 取决于比较质量 | |

| 配置寄存器测试 | 仅配置寄存器 | ||

| 集成硬件一致性监控 | 仅覆盖非法硬件异常 | ||

| 堆栈溢出探测 | 低 | 仅堆栈边界测试 | |

| NVM | 使用错误探测纠错码(E D C) | 高 | 取决于冗余的比特数;可用来纠错 |

| 储存器特征码 | - | ||

| 存储块复制 | - | ||

| 奇偶校验、改进的校验和 | 低 | - | |

| RAM | 使用错误探测纠错码(E D C) | 高 | 取决于冗余的比特数;可用来纠错 |

| 存储块复制 | 共因失效模式会降低诊断覆盖率 | ||

| 运行校验和/CRC | 特征码的有效性取决于一个与被 保护的存储块长度有关的多项式。 应当注意在校验和计算期间, 用于确定校验和的值不能被改变。 如果返回的是随机数据模式,则可能性就是校验和最大值的倒数 | ||

| RAM跨步测试 | 高 | 对链接单元的覆盖率取决于写和读的次序。测试通常不适合在运行时进行 | |

| RAM模式测试 | 中 | 对卡滞失效具有高覆盖率,对链接失效没有覆盖。适合在中断保护下运行 | |

| 奇偶校验位 | 低 | - | |

| 电源 | 电压或者电流控制( 输出) | 高 | - |

| 时钟 时序 | 具有独立时间基准和时间窗口的 看门狗 | 中 | 取决于时间窗口的时间限制 |

| 程序序列的逻辑监控 | 仅当外部暂时事件影响逻辑程序流时才能有效预防时钟失效。 提供了可能导致软件运行次序紊乱的内部硬件失效的覆盖率(比如中断频率错误) | ||

| 程序序列的时间和逻辑联合监控 | 高 | - | |

| 基于时间相关性的程序序列的 时间和逻辑联合监控 | 提供了对可能导致软件运行序列紊乱的内部硬件失效的覆盖。 当采用非对称设计时,提供了对主设备和监控设备间通信次序的覆盖。注:针对中断、CPU负载等导致的执行不稳定设计相应方法 | ||

| 组合 时序 逻辑 | 硬件自检 | 高 | 取决于自检的类型。门级是此测试的适当级别 |

| 软件自检 | 中 | - | |

| 片上 通信 | 测试模式 | 高 | 取决于模式类型 |

| 全硬件冗余 | 共因失效模式会降低诊断覆盖率 | ||

| 多位硬件冗余 | 中 | 适当的数据、地址和控制线的交错,且如果与一些完全冗余相结合(如 提供给仲裁),可达到高的诊断覆盖率 | |

TC3xx实施

| CPU | 锁步核,比较逻辑错误注入测试 |

| SRI接口ECC,SRI总线错误注入测试 | |

| 寄存器写保护 | |

| NVM/RAM | 存储内容ECC |

| 访问控制 | |

| 寄存器保护 | |

| 时钟 | 振荡器看门狗 |

| 内部备份时钟 | |

| 时钟监测 | |

| 寄存器位翻转硬件检测 | |

| 电源 | 输出监控 |

| 反馈ADC | |

| SRI系统资源互联 | EDC错误检测码 |

| 故障注入测试 | |

| 超时 | |

| SMU安全管理单元 | 所有安全机制警报归入SMU处理 |

1973

1973

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?