每次遇到问题,要从上往下详细梳理,不然很容易忽略或者遗漏中间环节,并且最后你会发现,问题的原因会非常低级。

先总结下出问题的原因:

1) 底层rtl 接线修改(ddr phy和ddr4 model的连线对应关系)后,对应的uvm环境没有对应的修改。

2)DDR工作模式修改后,没有确保连线完全正确。例如uvm中把mbist_mode接0后,并没有传给ddr module中去。

现象:

我们用的ddr4采用的是synopsys的Umctl2 ddr控制器,一直在报一个error如下:

问题跟踪:

1)刚开始没有得到确切信息说rtl底层修改了,因此,uvm环境中没有对应修改和ddr4 model的连线,本来以为是这个问题导致的,但是尝试发现,问题依旧存在。然后从开始报assert的地方开始追踪,和以前的代码进行对比,发现很多的x态没有办法解释。由于mbist_mode是自己在顶层亲自拉低的,所以很自信,没有想到竟然没有连接到ddr 的module中去,导致ddr 实际上没有工作在mbist mode下。

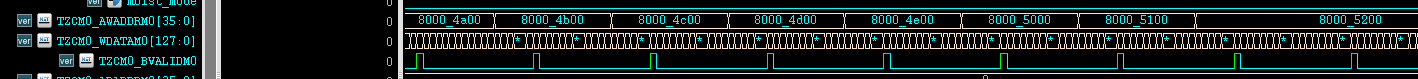

2)连接ok后,发现上述错误消失了,然后查看ddr的波形,看是否真正写进去了。发现有地址有数据有bvalid,应该已经写进去了。

追溯:

探究一下,dq和dqs的信号定义:

DQS:双向控制引脚(Bi-directional data strobe),是内存和内存控制器之间同步用的,由DQ信号发出端发出DQS,信号接收端根据DQS的上下沿来触发数据的接收。

从内存读信号:控制器会根据内存发出的DQS来判断什么时候接收读出的数据,

向内存写信号: 内存根据控制器发出的DQS来触发数据的接收。

对于DDR2,有一个读写双向的DQS,对于DDR3,有读和写两个DQS,那么DDR4呢?

ODT:中断匹配电阻,目前已经从主板上移到了芯片内部,odt的功能打开关闭由北桥芯片控制,其终结的信号有DQ、DQS、RDQS、DM等。

DM:对于突发写入,如果有不想要存入的数据,可以用DM信号进行屏蔽,DM信号和数据信号同时发出,接收方在DQS的上升沿和下降沿来判断DM的状态,如果DM=1,那么通过DQS中部选取的数据就被屏蔽了。

如下图:

dqs是两个信号线的差分信号,和clk/clkn作用一直,用于在一个时钟周期内准确区分出每个传输周期,便于接收方接收数据。 3表示2‘b11’, 此时上升沿和下降沿同时采样数据;如果0表示不采样数据。另外,对于DM信号,一直是3,表示数据全部屏蔽,即ddr控制器发出了这些数据,但是并没有实际写入到ddr中去。后又和设计确认,发现,DM这个信号为高时,表示写有效,表示数据写进去了,这个可以通过查找controller的spec来得到印证。

在axi_transaction的定义中,有WSTRB【n】信号,信号为高,代表对应数据线代表有效信息,每次写8bit对于一个strobe,WSTRB【n】对应WDATA【8n+7:8n】,master必须确认strobe为高时,对应byte line只包含有效数据。

758

758

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?