先了解内存知识基础:

(2条消息) DDR 内存基础知识(2)- DDR预取_0xFFFFFFF0的博客-CSDN博客_ddr 预取

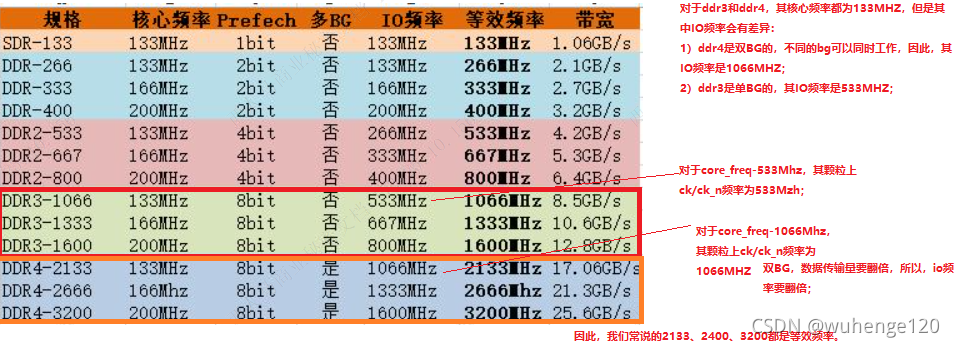

1、DDR4和DDR3 的一个差异是:DDR4之前的带宽提升依靠增加预取的bit数(ddr 2bit,ddr2 4bit ,ddr3 8bit 预取),而到了ddr4,只能通过bank group的方式来提高带宽了。

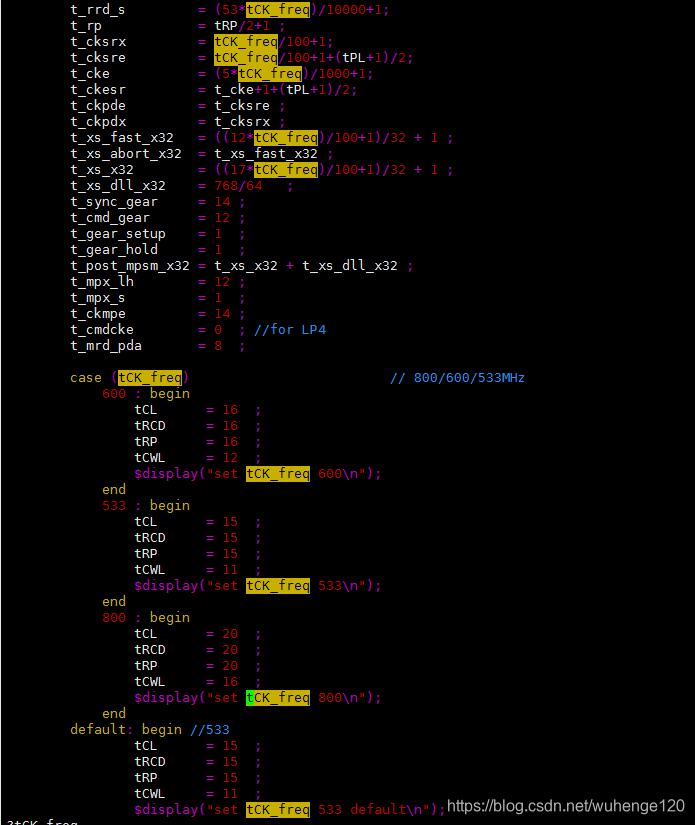

对于DDR4的控制器和DDR4颗粒,首先会提供一个tCK_freq的参数,这个参数值一般是533Mhz、600Mhz和800Mhz,分别对应数据传输率为2133Mbit、2400Mbit和3200Mbit。

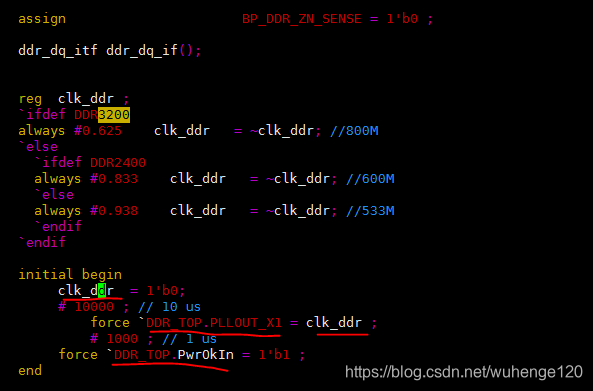

在UVM环境中,有一个宏+define+DDR2133,此宏的生效的地方在:

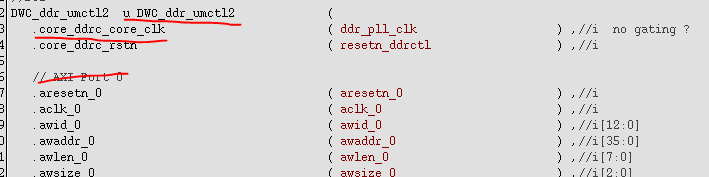

可以看到此时在我们验证平台中产生的clk连接到了DDR_TOP.PLLOUT_X1这个信号管脚中去了,这个信号会得到ddr_pll_clk并传递给umctl2 这个ddr控制器中,用于给umctl提供core_ddrc_core_clk,产生的时钟有533Mhz、600Mhz和800Mhz;

另外,在uvm验证环境中,在配置ddr的时候也需要将tCK_freq配置对应的频率,是为了生成相应的时序,并写入到DDR 的controller中去。

但是533/600/800Mhz和2133/2400/3200Mbit是如何挂钩在一起的呢?

从ddr颗粒的时钟波形上可以看出,ck/ck_n的信号频率是1.06Ghz,并且上下沿采样,因此,一根数据线上的数据传输率为1.06Ghzx2=2133Mbit;

那么1.06Ghz是如何根据533Mhz得到的呢?

对于双BG的DDR4,由于两个BG可以同时工作,因此,其IO频率(即颗粒上的ck/ck_n 会翻倍)。

而我们将的2133Mhz/2400Mhz/3200Mhz均为等效频率。

2、总的带宽如何计算呢?

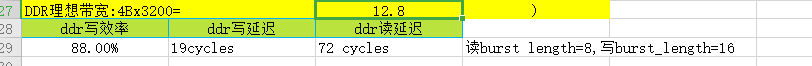

例如tCK_freq=800Mhz时候,接了两个DDR颗粒,BP_DDR_DQ是inout [31:0],每个ddr颗粒16bit,因此,总的带宽为:3200Mbit x 32=

根据之前同事总结的来看,对于总线位宽32bit来说,3200M情况下,总线带宽为:3200x4B(4x8bit)=12.8GByte/s

那么ddr的带宽都受那些影响呢?

上面讲述的是ddr的频率对带宽的影响,例如对于600Mhz和800Mhz tCK_freq,带宽是不同的;那么noc总线是否对ddr的读写带宽有影响呢?如果有,如何影响带宽?

如果DDR的频率比较小,那么主要影响带宽的因素就是ddr的频率;如果DDR的频率比较大,那么主要影响带宽的因素就是noc 总线的频率;例如:

对于DDR 2400(对应的tCK_freq=600Mhz), 总线位宽是32bit,最大带宽是=2400x32 /8=9.6Gbyte/s

对于noc 总线clk=600Mhz,由于ddr和noc总线接口位宽是128bit,因此,带宽计算:600Mhzx 128/8= 9.6Gbyte/s

如何查看noc的位宽:

![]()

3、DDR 的bank group 的作用

![]()

根据addr地址,可以看出,bank_group对应的是addr[30:29], bank 对应的是addr[28:27], row 对应addr[26:10], col对应addr[9:0];

4、DDR4和DDR5的具体区别在哪里?

1)总线带宽更高。

2)功耗更低。

本文深入讲解DDR内存的基础知识,包括DDR4与DDR3的差异,DDR4的带宽提升机制,如bankgroup对性能的影响。内容涵盖DDR4的tCK_freq参数、时钟频率与数据传输率的关系,以及总线带宽的计算方法。此外,还探讨了DDR的bankgroup如何通过addr地址映射进行操作,并简单介绍了DDR4与DDR5的主要区别。

本文深入讲解DDR内存的基础知识,包括DDR4与DDR3的差异,DDR4的带宽提升机制,如bankgroup对性能的影响。内容涵盖DDR4的tCK_freq参数、时钟频率与数据传输率的关系,以及总线带宽的计算方法。此外,还探讨了DDR的bankgroup如何通过addr地址映射进行操作,并简单介绍了DDR4与DDR5的主要区别。

2809

2809

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?