前言

在进行FPGA电路设计时,遇到了一些问题,决定讲这些内容汇总起来,加上自己的理解,以方便学习(后续持续更新,期望大家多多指正)。

名词解释

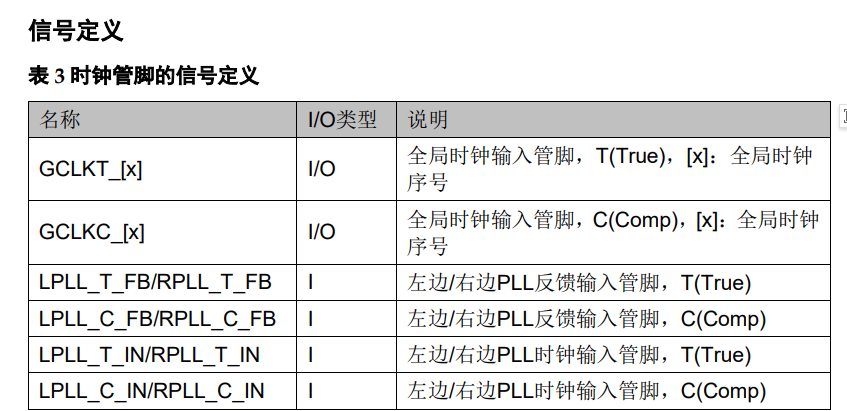

在进行高云的一款FPGA进行时钟设计的过程,遇到了两种类型的时钟,True和Comp(见图1)。查了下网上的资源,找到一篇很详细的文章——FPGA解惑:从IO到原语(Gowin为例)。其解释如下:

- True 和 Comp:分别表示差分对的真值和补值。差分信号通过这两根线传输,具有较强的抗噪性。

设计上如果是单端的时钟则要接gclkt,差分实时T接p端、C接n端;故此个人理解就是类似于二进制中的真值和补码,那么True就是原数据,Comp就是还要再做处理。

设计思考

不用的BANK处理方式

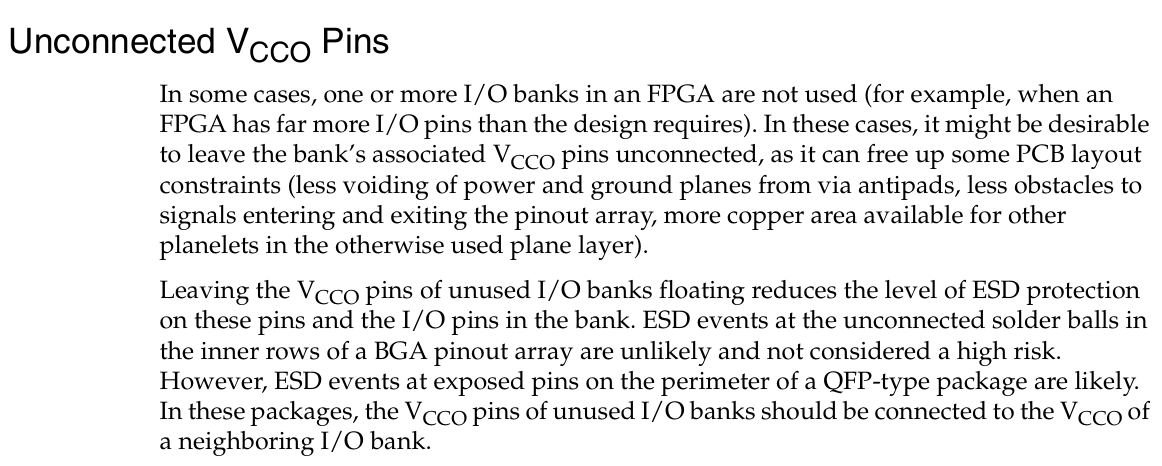

以前几乎都是担心IO口不够用,前段时间却刚好遇到过芯片已定型,但IO却用的很少的情况,因此就考虑到这个问题。查了些许资料,还是从FPGA的龙头赛灵思找到了一点解释(见图2):建议是还是即使不用也要保持连接,不然就会降低IO的ESD防护能力,尤其是对QFP封装的边缘。

网上也确实有遇到过类似问题,在 xilinx的两三个bank不供电,是否会引起fpga工作不正常?这个论坛里博主就遇到过,所以后面如果碰到的时候设计上还是要注意一下。

个人理解,BGA相较于QFP电源布局跟引脚的接触面积更大,寄生效应更小,因此防护作用会更好。

501

501

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?