名称:基于FPGA的多输出的逻辑网络Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

设计一个多输出的逻辑网络,它的输入是8421BCD码,它的输出定义为

Y1:检测到输入数字能被2整除

Y2:检测到输入数字能被3整除

Y3:检测到输入数字能被5整除

要求

1.用可编程器件完成设计,器件型号EPM240T100C5

2.写出 Verilog HDL语言源代码

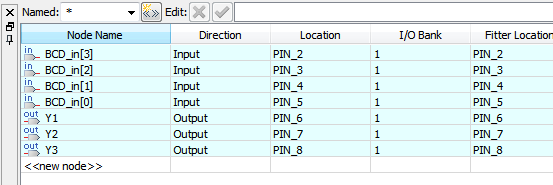

3.配置器件的管脚

4.给出设计的仿真波形。

1. 工程文件

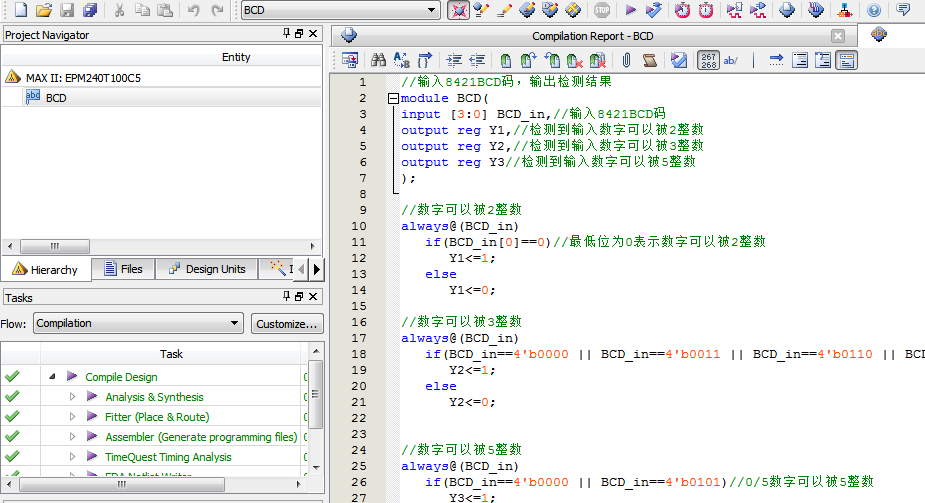

2. 程序文件

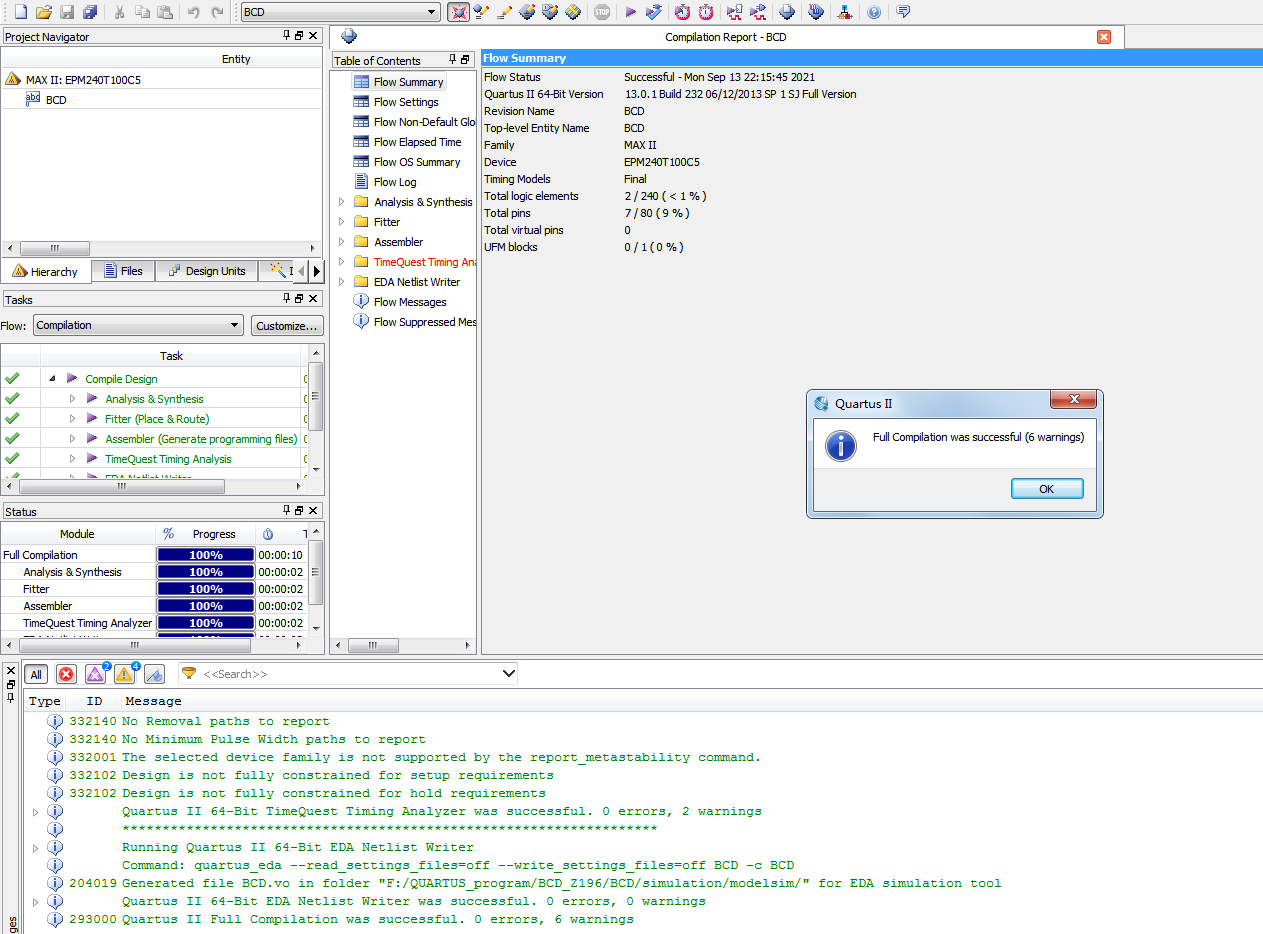

3. 程序编译

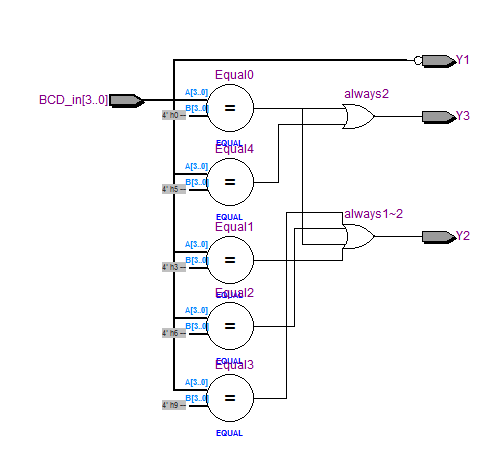

4. RTL图

5. 管脚分配

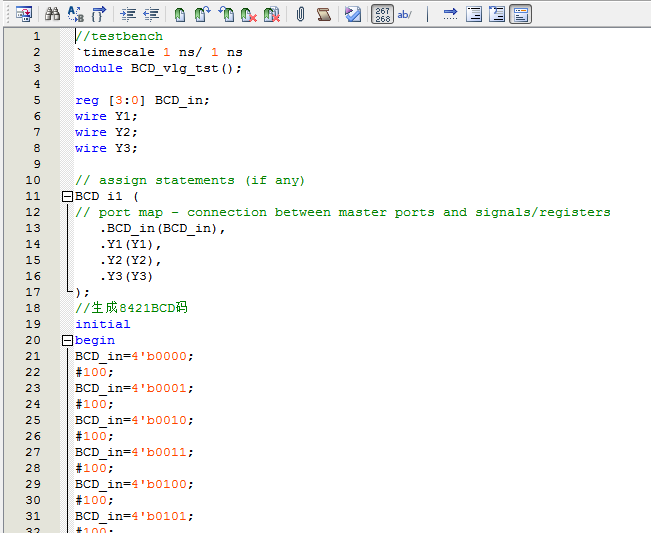

6. Testbench

7. 仿真图

部分代码展示:

/输入8421BCD码,输出检测结果 module BCD( input [3:0] BCD_in,//输入8421BCD码 output reg Y1,//检测到输入数字可以被2整数 output reg Y2,//检测到输入数字可以被3整数 output reg Y3//检测到输入数字可以被5整数 ); //数字可以被2整数 always@(BCD_in) if(BCD_in[0]==0)//最低位为0表示数字可以被2整数 Y1<=1; else Y1<=0;

源代码

扫描文章末尾的公众号二维码

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?