名称:基于FPGA的8位卷积运算设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:8位卷积运算

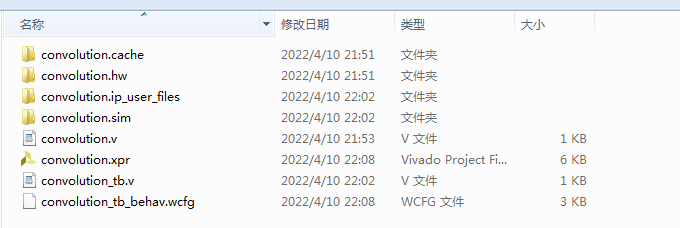

1. 工程文件

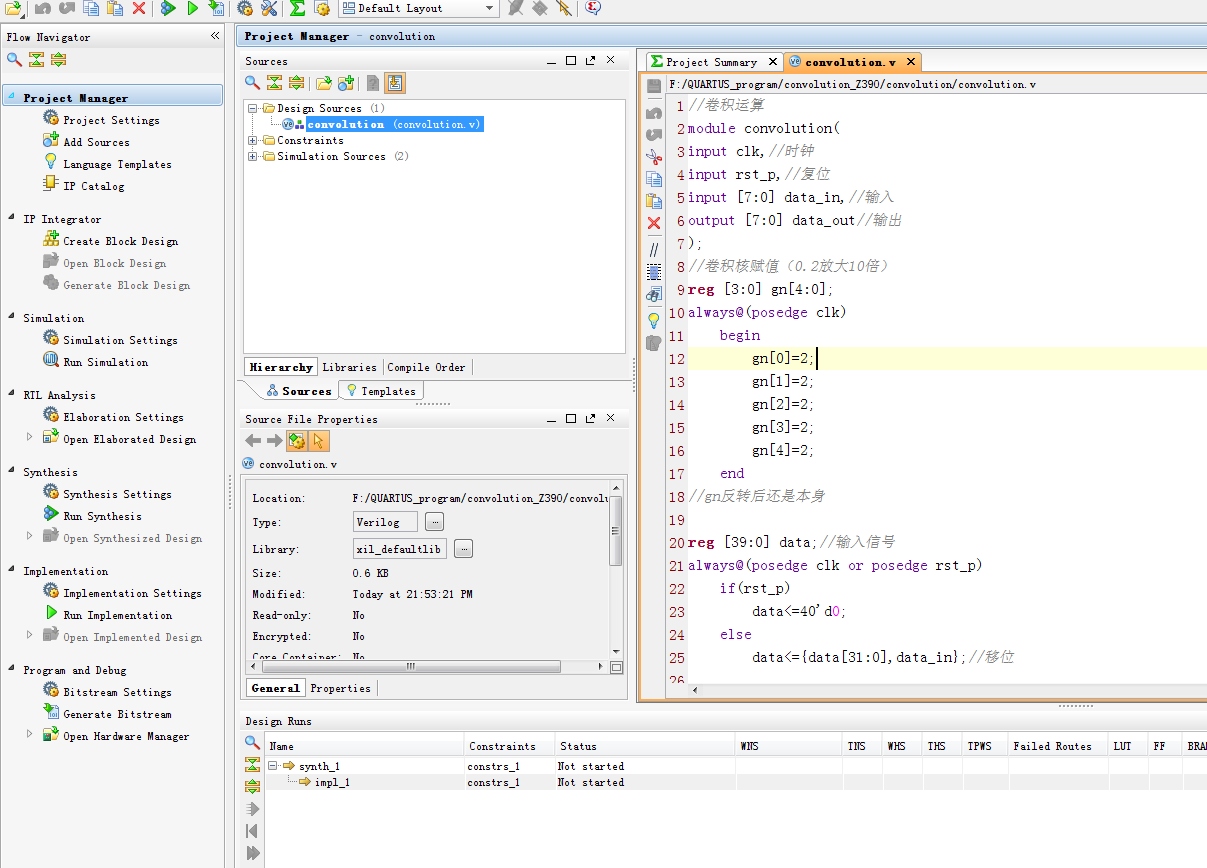

2. 程序文件

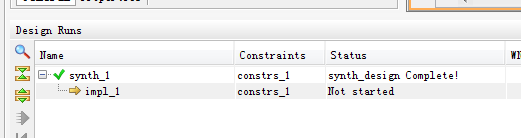

3. 程序编译

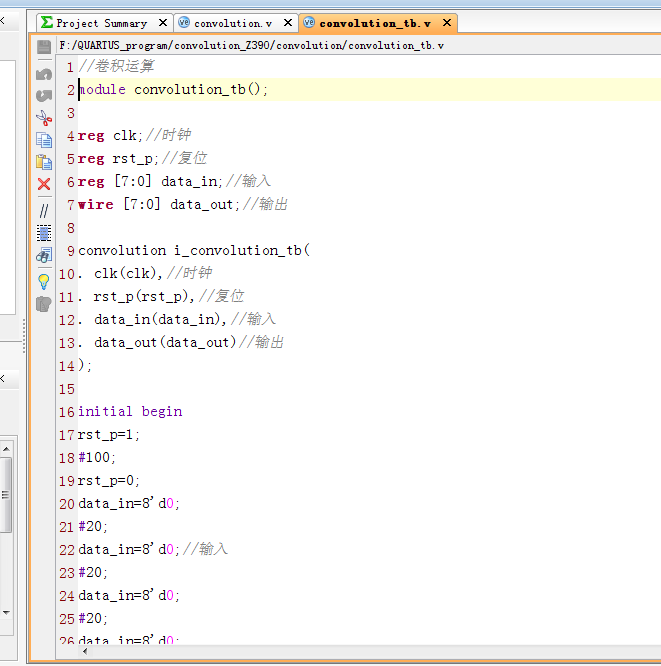

4. Testbench

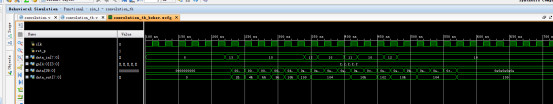

5. 仿真图

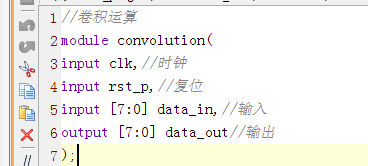

部分代码展示:

//卷积运算

module convolution(

input clk,//时钟

input rst_p,//复位

input [7:0] data_in,//输入

output [7:0] data_out//输出

);

//卷积核赋值(0.2放大10倍)

reg [3:0] gn[4:0];

always@(posedge clk)

begin

gn[0]=2;

gn[1]=2;

gn[2]=2;

gn[3]=2;

gn[4]=2;

end

//gn反转后还是本身

reg [39:0] data;//输入信号

always@(posedge clk or posedge rst_p)

if(rst_p)

data<=40'd0;

else

data<={data[31:0],data_in};//移位

//累加和

assign data_out=gn[0]*data[39:32]+gn[1]*data[31:24]+gn[2]*data[23:16]+gn[3]*data[15:8]+gn[4]*data[7:0];

endmodule

源代码

扫描文章末尾的公众号二维码

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?