名称:基于FPGA的模16减法计数器设计VHDL代码ISE仿真(文末获取)

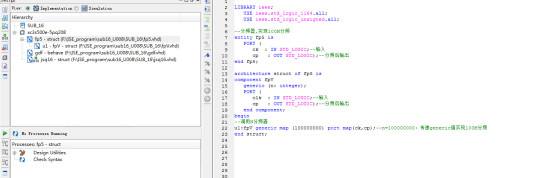

软件:ISE

语言:VHDL

代码功能:

参考实验步

1.新建工程

2.用VHDL设计一个时钟分频器fpV,其分频数由 Generic确定,初始值取16。并完成仿真

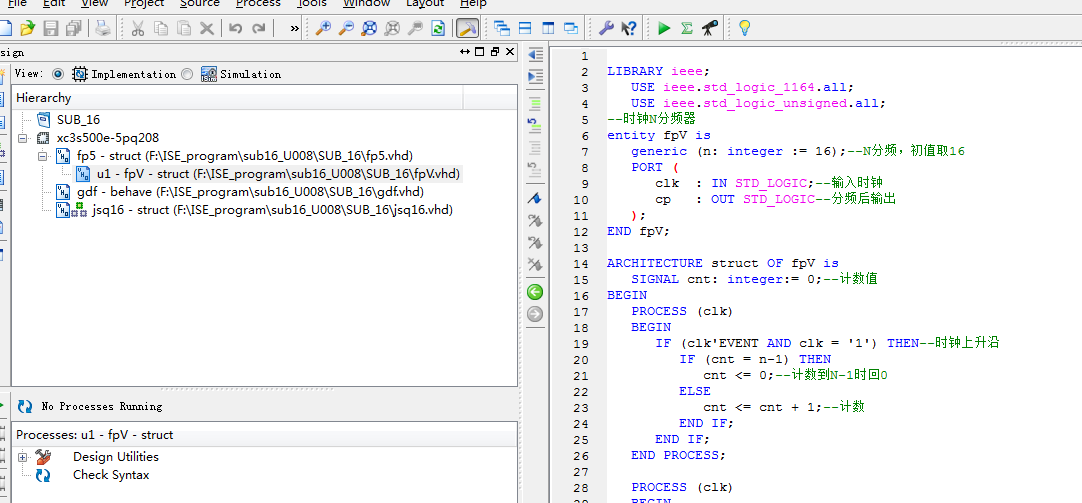

3.用VHDL设计分频器fp5,通过调用fpV实现100M分频。请理解并参考如下清单

entity fp5 is

Port (ck in STD LOGIC

cp:out STD LOGIC)

end fp5:

architecture struct of fp5 is

component fpV

generic(n: integer).

port(ck: in std logic;

cp:out std logic);

end component

begin

u: fpv generic map(10000000 port map(ck.cp)-通过传递 Generic值实现100M分频end struct:

注:分频器设计也可以采用其他方法

4.用VHDL设计一个模16的减法计数器jsq16,并完成仿真。

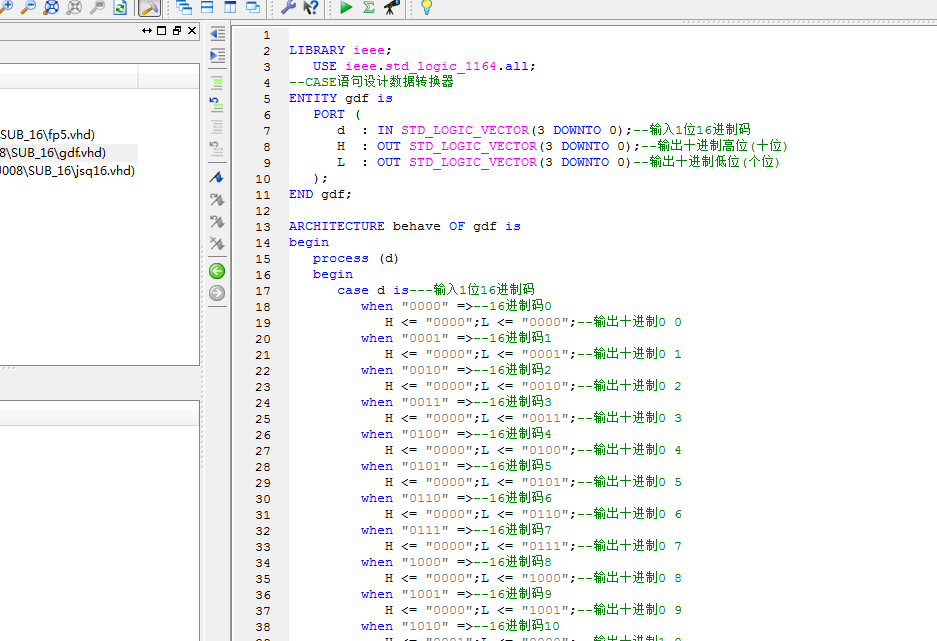

5.用VHDL设计一个数据转换器gdf(请采用CASE语句),该转换器的功能是将一位16进制码转换为两位10进制码。其中H(3:0)为高位,数值范围是是000001,L(3:0)为低位,数值范围是0000-1001。并完成仿真

1. 时钟分频器

程序文件

Testbench

仿真图

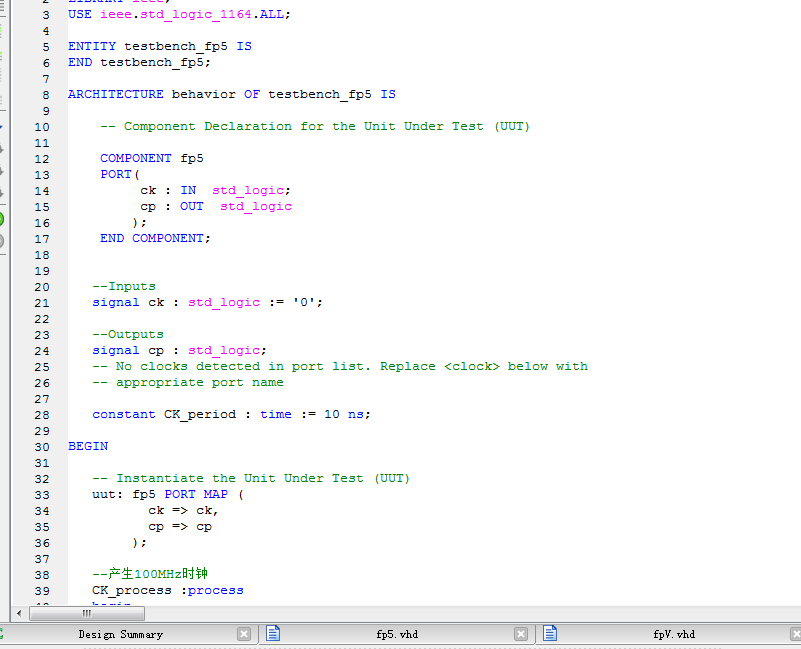

2. 模16减法计数器

程序文件

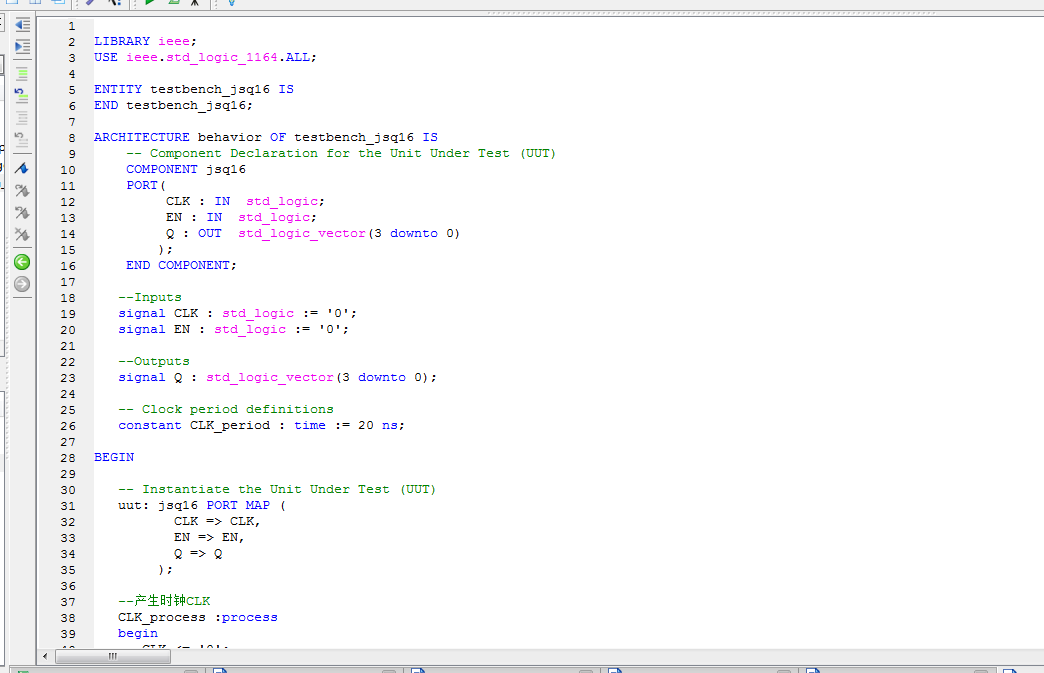

Testbench

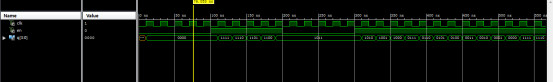

仿真图

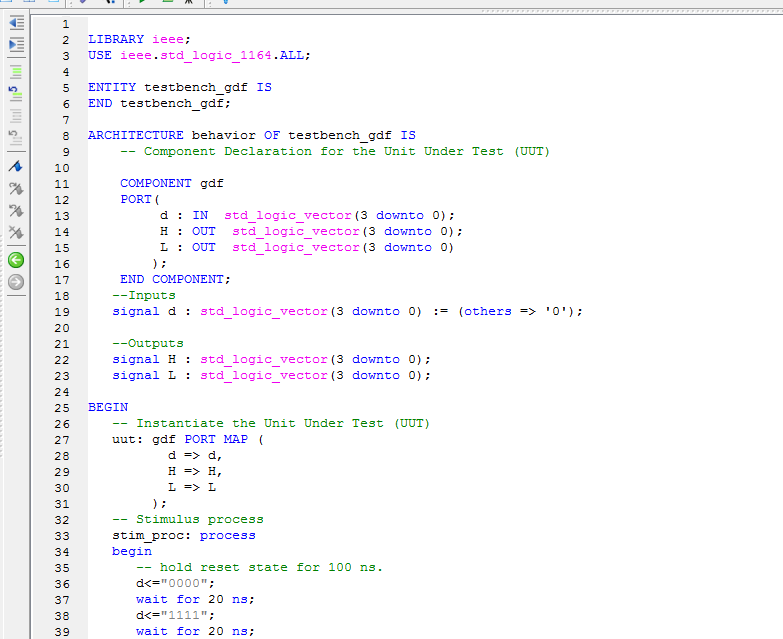

3. 数据转换器

程序文件

Testbench

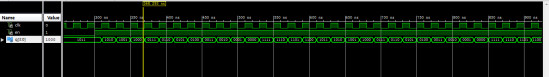

仿真图

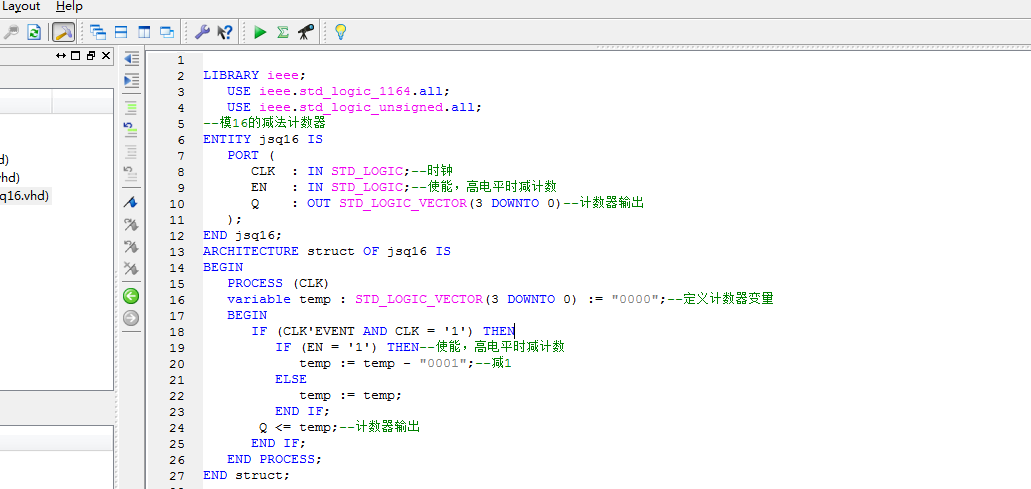

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --分频器,实现100M分频 entity fp5 is PORT ( ck : IN STD_LOGIC;--输入 cp : OUT STD_LOGIC);--分频后输出 end fp5; architecture struct of fp5 is component fpV generic (n: integer); PORT ( clk : IN STD_LOGIC;--输入 cp : OUT STD_LOGIC);--分频后输出 end component; begin --调用N分频器 u1:fpV generic map (100000000) port map(ck,cp);--n=100000000,传递generic值实现100M分频 end struct;

源代码

扫描文章末尾的公众号二维码

1147

1147

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?