名称:基于FPGA的地铁售票机设计VHDL代码ISE仿真(文末获取)

软件:ISE

语言:VHDL

代码功能:

地铁售票机

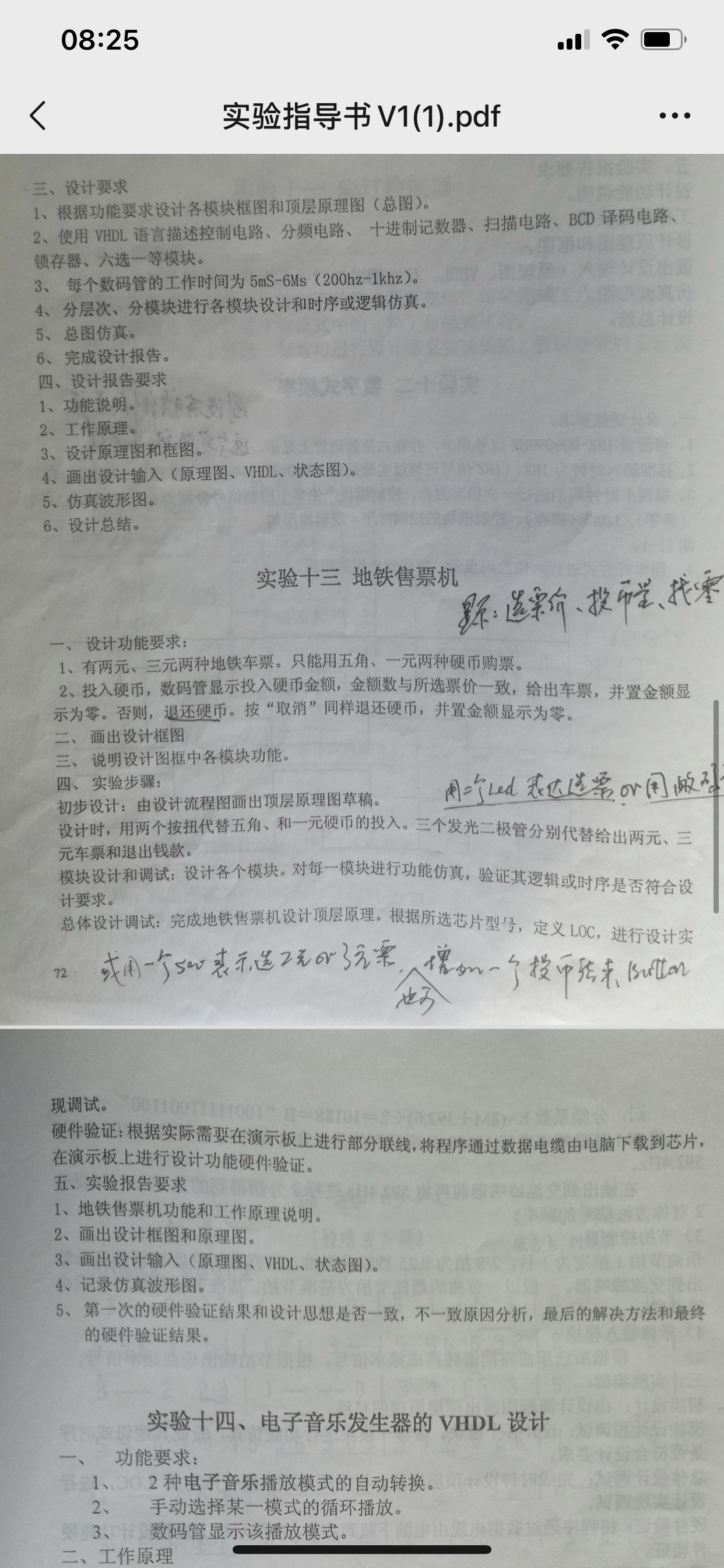

一、设计功能要求

1、有两元,三元两种地铁车票。只能用五角、一元两种硬币购票

2,投入硬币,数管显示投入便币金额,金与所选票价一致,给出车票,并置金额显示为零,否则,退还便币,按“取消”同样退还硬币,并置金额显示为零

二、画出设计准图

三、说明设计图中各模块功能

四、实验步骤

初步设计:由设计流程图画出顶层原理图草稿

设计时,用两个按扭代替五角、和一元硬门币的投入,三个发光二极管分别代替给出两元、三元车票和退出钱款。

模块设计和调试:设计各个模块,对每一模块进行功能仿真,验其逻时序是否符合设计要求

总体设计调试,完成地铁售票机设计顶层原理,根据所选芯片型号,定义LOC,进行设计实现调试

硬牛验证:根据实际需要在示板上进行部分联线,将程序通过数据电缆由电脑下载到芯片,在演示板上进行设计功能硬件验证

五、实验报告要求

1、地铁售票机功能和工作原理说明

2、画出设计框图和原理图

3、画出设计输入(原理图、VEDL、状态图)

4、记录仿真波形图

5、第一次的硬件验证结果和设计思想是否一致,不一致原因分析,最后的解决方法和最终的硬件验证结果

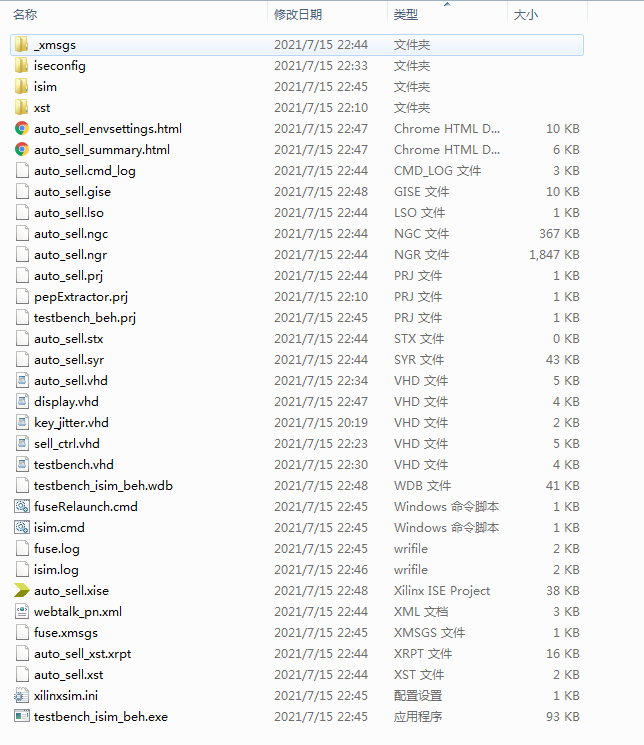

1. 工程文件

2. 程序文件

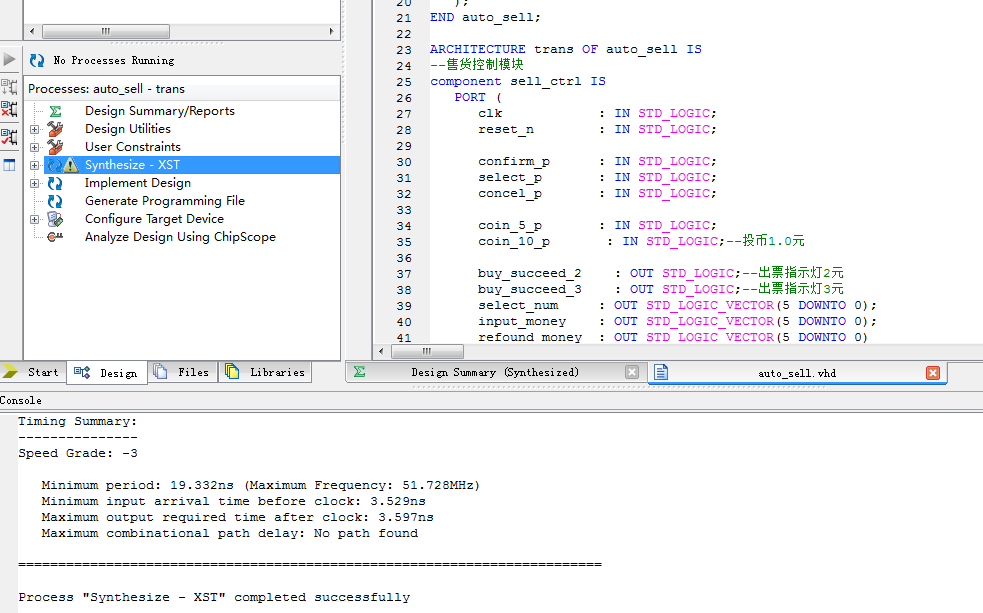

3. 程序编译

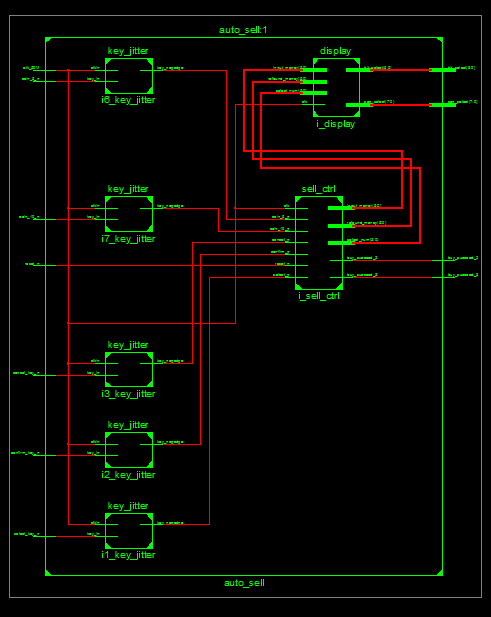

4. RTL图

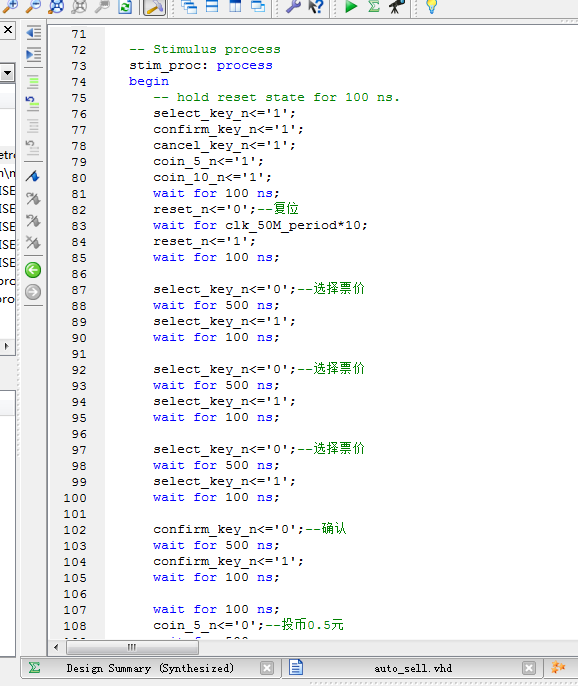

5. Testbench

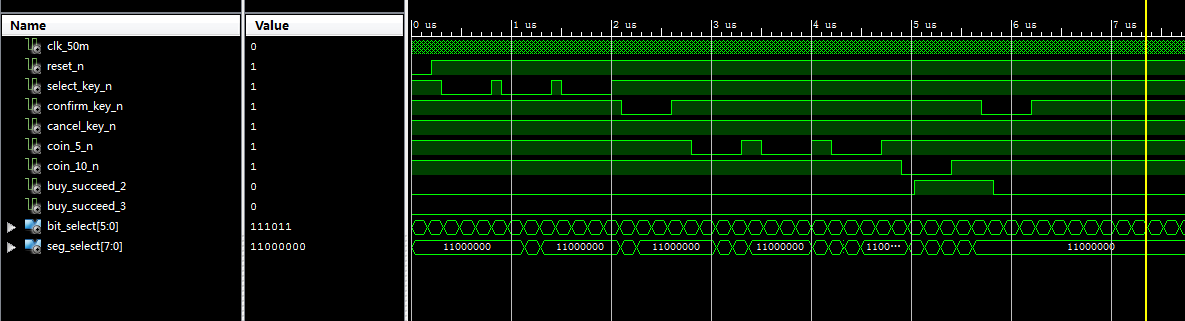

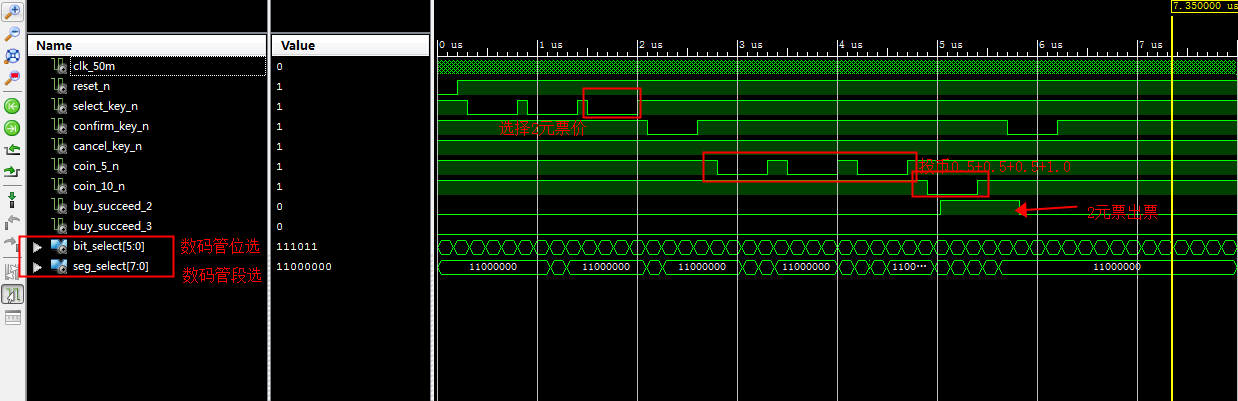

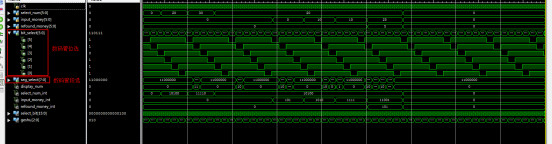

6. 仿真图

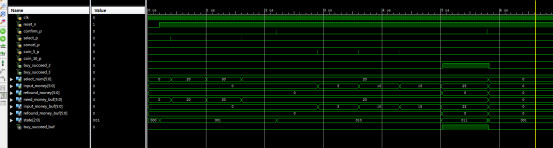

整体仿真图

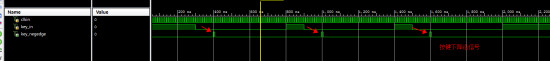

按键模块仿真

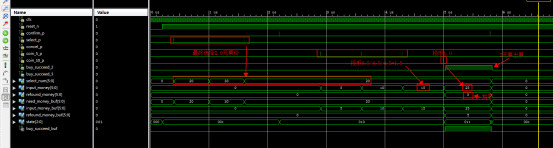

售货机控制模块仿真

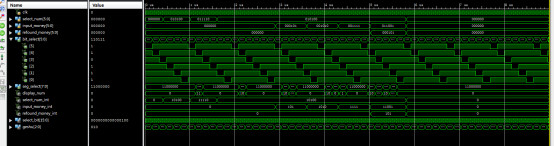

数码管显示模块仿真

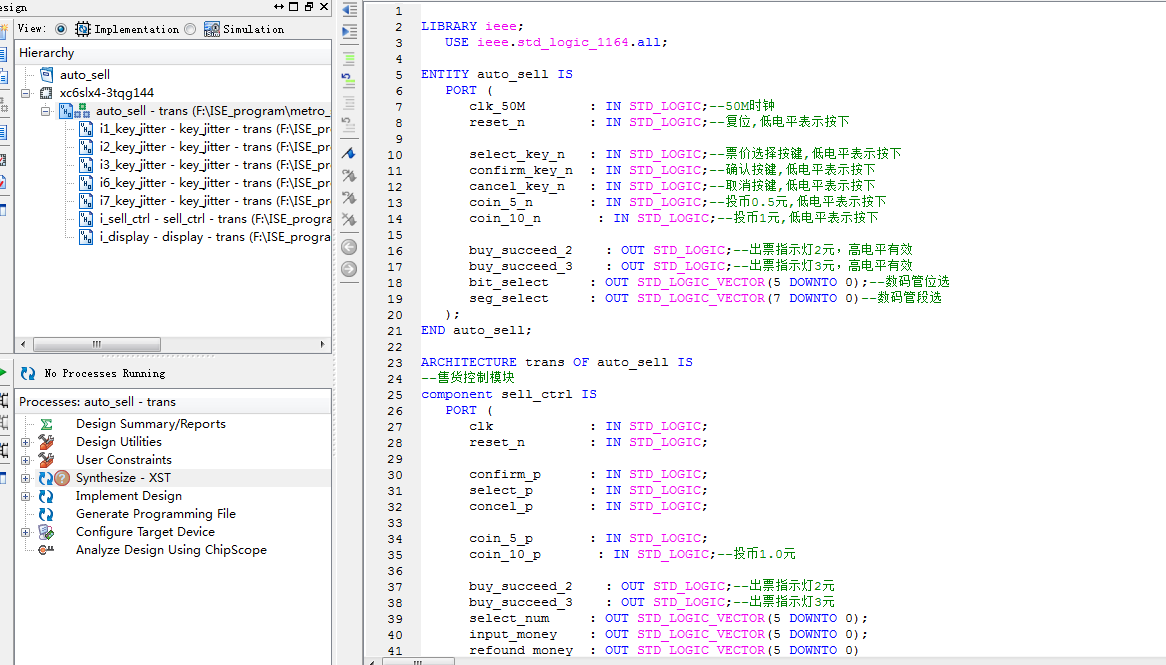

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY auto_sell IS PORT ( clk_50M : IN STD_LOGIC;--50M时钟 reset_n : IN STD_LOGIC;--复位,低电平表示按下 select_key_n : IN STD_LOGIC;--票价选择按键,低电平表示按下 confirm_key_n : IN STD_LOGIC;--确认按键,低电平表示按下 cancel_key_n : IN STD_LOGIC;--取消按键,低电平表示按下 coin_5_n : IN STD_LOGIC;--投币0.5元,低电平表示按下 coin_10_n : IN STD_LOGIC;--投币1元,低电平表示按下 buy_succeed_2 : OUT STD_LOGIC;--出票指示灯2元,高电平有效 buy_succeed_3 : OUT STD_LOGIC;--出票指示灯3元,高电平有效 bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END auto_sell; ARCHITECTURE trans OF auto_sell IS --售货控制模块 component sell_ctrl IS PORT ( clk : IN STD_LOGIC; reset_n : IN STD_LOGIC; confirm_p : IN STD_LOGIC; select_p : IN STD_LOGIC; concel_p : IN STD_LOGIC; coin_5_p : IN STD_LOGIC; coin_10_p : IN STD_LOGIC;--投币1.0元 buy_succeed_2 : OUT STD_LOGIC;--出票指示灯2元 buy_succeed_3 : OUT STD_LOGIC;--出票指示灯3元 select_num : OUT STD_LOGIC_VECTOR(5 DOWNTO 0); input_money : OUT STD_LOGIC_VECTOR(5 DOWNTO 0); refound_money : OUT STD_LOGIC_VECTOR(5 DOWNTO 0) ); END component; --按键消抖模块 component key_jitter IS PORT ( clkin : IN STD_LOGIC; key_in : IN STD_LOGIC; key_negedge : OUT STD_LOGIC ); END component; --显示模块 component display IS PORT ( clk : IN STD_LOGIC; select_num : IN STD_LOGIC_VECTOR(5 DOWNTO 0); input_money : IN STD_LOGIC_VECTOR(5 DOWNTO 0); refound_money : IN STD_LOGIC_VECTOR(5 DOWNTO 0); bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0); seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END component; SIGNAL select_num : STD_LOGIC_VECTOR(5 DOWNTO 0); SIGNAL input_money : STD_LOGIC_VECTOR(5 DOWNTO 0); SIGNAL refound_money : STD_LOGIC_VECTOR(5 DOWNTO 0); SIGNAL confirm_p : STD_LOGIC; SIGNAL select_p : STD_LOGIC; SIGNAL concel_p : STD_LOGIC; SIGNAL coin_5_p : STD_LOGIC; SIGNAL coin_10_p : STD_LOGIC; -- Declare intermediate signals for referenced outputs SIGNAL buy_succeed_buf : STD_LOGIC; SIGNAL bit_select_buf : STD_LOGIC_VECTOR(5 DOWNTO 0); SIGNAL seg_select_buf : STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN bit_select <= bit_select_buf; seg_select <= seg_select_buf; --调用按键消抖模块 i1_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => select_key_n, key_negedge => select_p ); --调用按键消抖模块 i2_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => confirm_key_n, key_negedge => confirm_p ); --调用按键消抖模块 i3_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => cancel_key_n, key_negedge => concel_p ); --调用按键消抖模块 i6_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => coin_5_n, key_negedge => coin_5_p ); --调用按键消抖模块 i7_key_jitter : key_jitter PORT MAP ( clkin => clk_50M, key_in => coin_10_n, key_negedge => coin_10_p );

源代码

扫描文章末尾的公众号二维码

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?