名称:基于FPGA的简易万年历设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:简易万年历设计

1. 工程文件

2. 程序文件

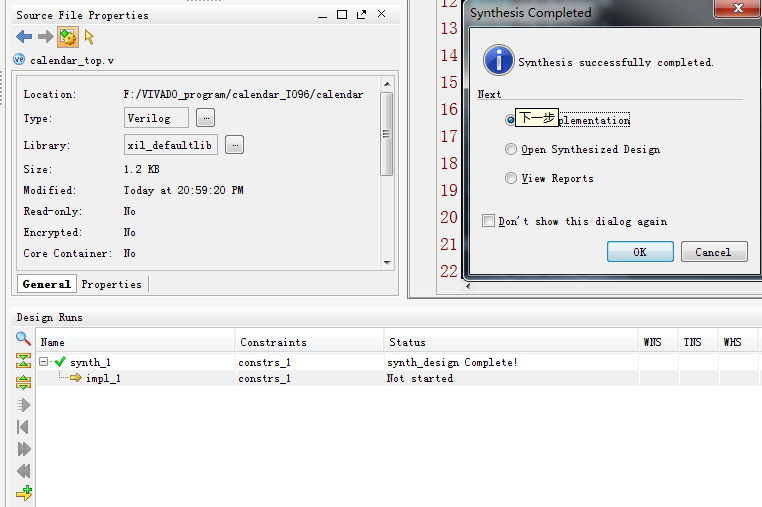

3. 程序编译

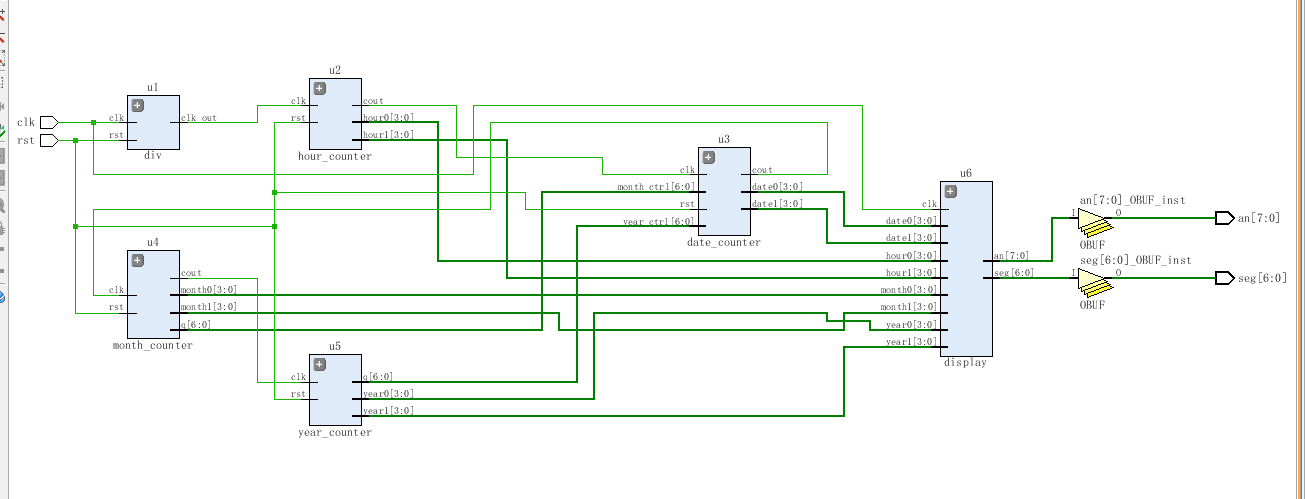

4. RTL图

5. Testbench

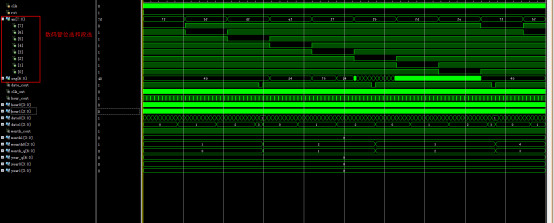

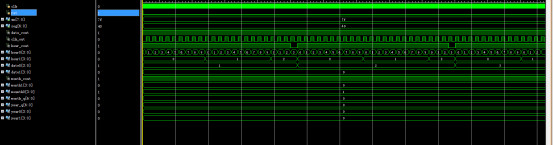

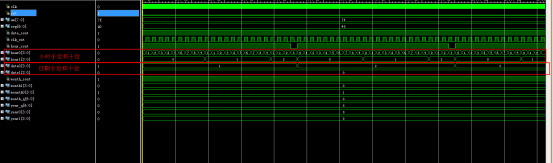

6. 仿真图

部分代码展示:

//万年历顶层模块 module calendar_top( output [7:0]an, input clk, input rst, output [6:0] seg); wire date_cout; wire [3:0]date0; wire [3:0]date1; wire clk_out; wire hour_cout; wire [3:0]hour0; wire [3:0]hour1; wire month_cout; wire [3:0]month1; wire [3:0]mounth0; wire [6:0]month_q; wire [6:0]year_q; wire [3:0]year0; wire [3:0]year1; div u1(.clk(clk), .clk_out(clk_out), .rst(rst)); //分频模块 hour_counter u2 (.clk(clk_out), .cout(hour_cout), .hour0(hour0), .hour1(hour1), .rst(rst)); //时钟计数模块 date_counter u3 (.clk(hour_cout), .cout(date_cout), .date0(date0), .date1(date1), .month_ctrl(month_q), .rst(rst), .year_ctrl(year_q)); //日期计数模块 month_counter u4 (.clk(date_cout), .cout(month_cout), .month0(mounth0), .month1(month1), .q(month_q), .rst(rst)); //月计数模块 year_counter u5 (.clk(month_cout), .q(year_q), .rst(rst), .year0(year0), .year1(year1)); //年计数模块

源代码

扫描文章末尾的公众号二维码

1002

1002

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?