名称:基于FPGA的同步清零置数加减法计数器设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

实现一个计数器:

1、计数器位宽为4;

2、要求可以实现同步清零,及同步置数的功能;

3、通过一个输入信号来选择:实现加法计数和减法计数;加到最大值后如果继续加或减到0后继续减,则计数器不变

4、输出最终的计数值的数据类型是wire型;

5、需要搭建简单的 testbench,用位置关联法例化,仿出波形。

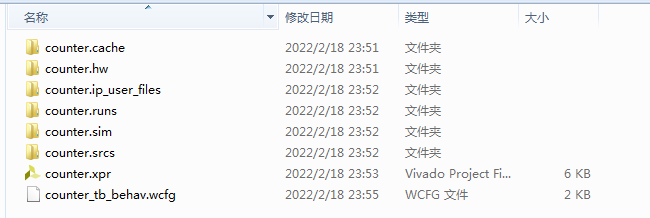

1. 工程文件

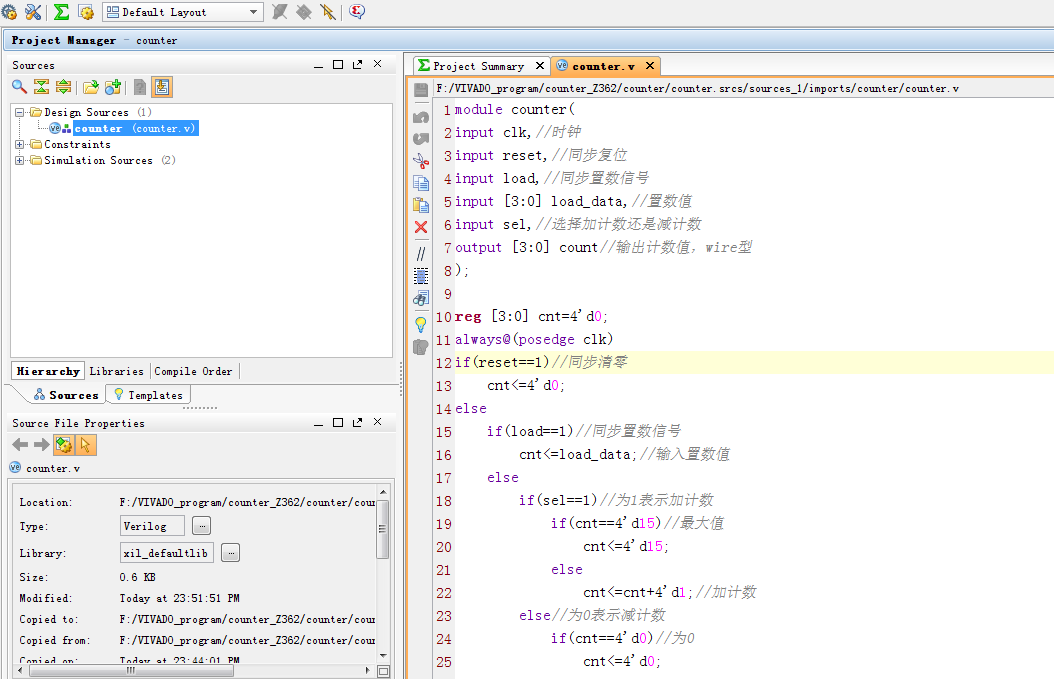

2. 程序文件

3. 程序编译

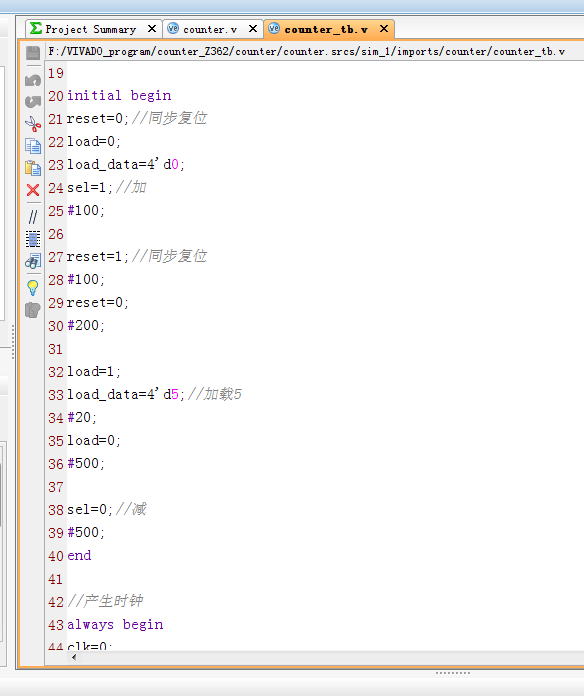

4. Testbench

5. 仿真图

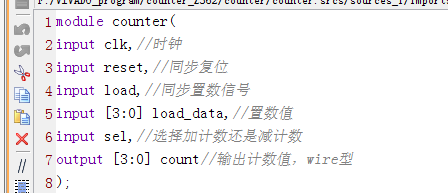

部分代码展示:

module counter( input clk,//时钟 input reset,//同步复位 input load,//同步置数信号 input [3:0] load_data,//置数值 input sel,//选择加计数还是减计数 output [3:0] count//输出计数值,wire型 ); reg [3:0] cnt=4'd0; always@(posedge clk) if(reset==1)//同步清零 cnt<=4'd0; else if(load==1)//同步置数信号 cnt<=load_data;//输入置数值 else if(sel==1)//为1表示加计数 if(cnt==4'd15)//最大值 cnt<=4'd15; else cnt<=cnt+4'd1;//加计数 else//为0表示减计数 if(cnt==4'd0)//为0 cnt<=4'd0;

源代码

扫描文章末尾的公众号二维码

902

902

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?