名称:基于FPGA的调用IP核实现128和512点FFT设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:调用IP核实现128和512点FFT

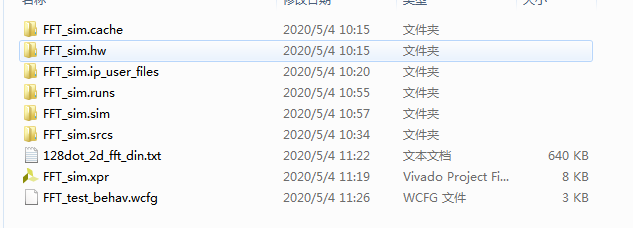

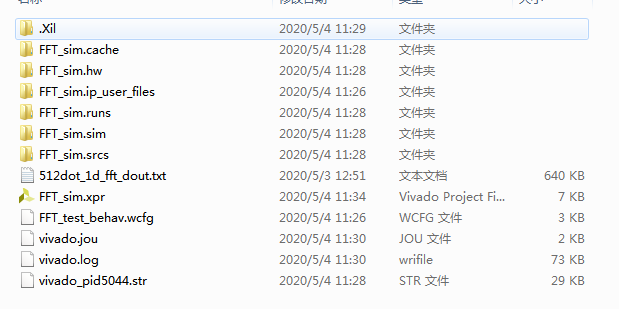

1. 工程文件

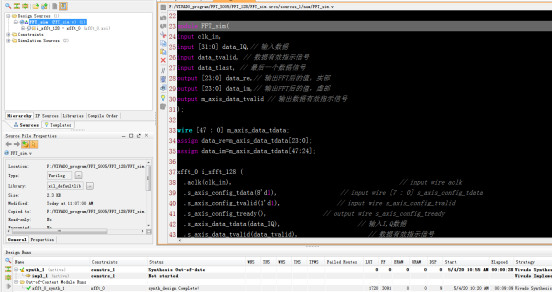

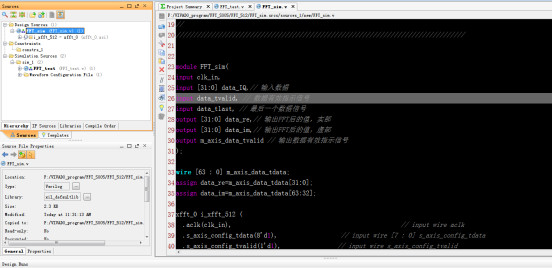

2. 程序文件

128点

512点

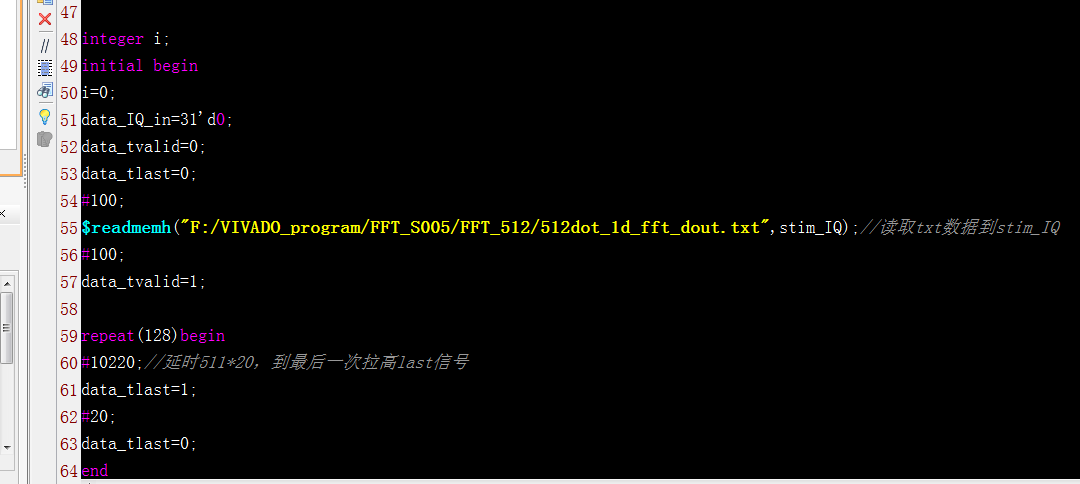

3. Testbench

128点

512点

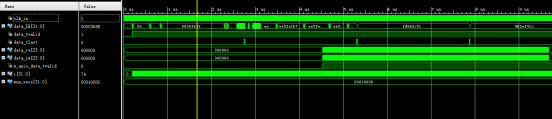

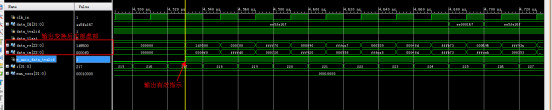

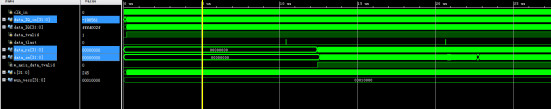

4. 仿真图

128点仿真图

512点仿真图

部分代码展示:

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2020/04/17 23:17:51 // Design Name: // Module Name: FFT_8192 // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module FFT_sim( input clk_in, input [31:0] data_IQ,// 输入数据 input data_tvalid, // 数据有效指示信号 input data_tlast, // 最后一个数据信号 output [23:0] data_re,// 输出FFT后的值,实部 output [23:0] data_im,// 输出FFT后的值,虚部 output m_axis_data_tvalid // 输出数据有效指示信号 ); wire [47 : 0] m_axis_data_tdata; assign data_re=m_axis_data_tdata[23:0]; assign data_im=m_axis_data_tdata[47:24]; xfft_0 i_xfft_128 ( .aclk(clk_in), // input wire aclk .s_axis_config_tdata(8'd1), // input wire [7 : 0] s_axis_config_tdata .s_axis_config_tvalid(1'd1), // input wire s_axis_config_tvalid .s_axis_config_tready(), // output wire s_axis_config_tready .s_axis_data_tdata(data_IQ), // 输入I,Q数据 .s_axis_data_tvalid(data_tvalid), // 数据有效指示信号 .s_axis_data_tready(), // output wire s_axis_data_tready .s_axis_data_tlast(data_tlast), // 最后一个数据信号 .m_axis_data_tdata(m_axis_data_tdata), // 输出FFT后的值,包括实部虚部 .m_axis_data_tvalid(m_axis_data_tvalid), // 输出数据有效指示信号 .m_axis_data_tready(1'b1), // input wire m_axis_data_tready .m_axis_data_tlast(), // output wire m_axis_data_tlast .event_frame_started(), // output wire event_frame_started .event_tlast_unexpected(), // output wire event_tlast_unexpected .event_tlast_missing(), // output wire event_tlast_missing .event_status_channel_halt(), // output wire event_status_channel_halt .event_data_in_channel_halt(),

源代码

扫描文章末尾的公众号二维码

533

533

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?