名称:带左转灯的交通灯控制器设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

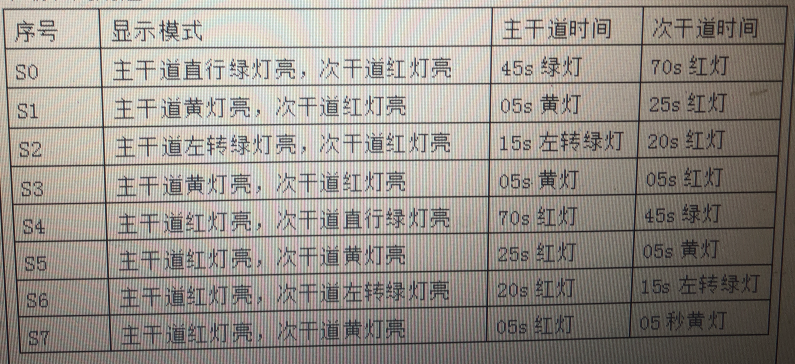

在空间上,右转车辆不与直行车辆冲实,故不考虑对右转车辆的控制情况,在交叉路口中按照实际设定整个循环周期不应太长,否则会导致相位上排队过长影响驾驶员的心理,所以在本次设定中,考虑到直行车辆比左转车辆流量大的情况下,直行绿灯设置45s,左转绿灯设置15s,中间夹杂两次5s的黄灯,所以个最长周期是140s

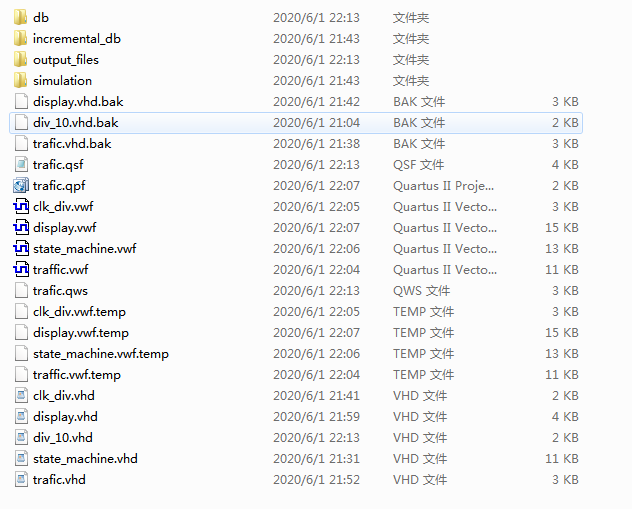

1. 工程文件

2. 程序文件

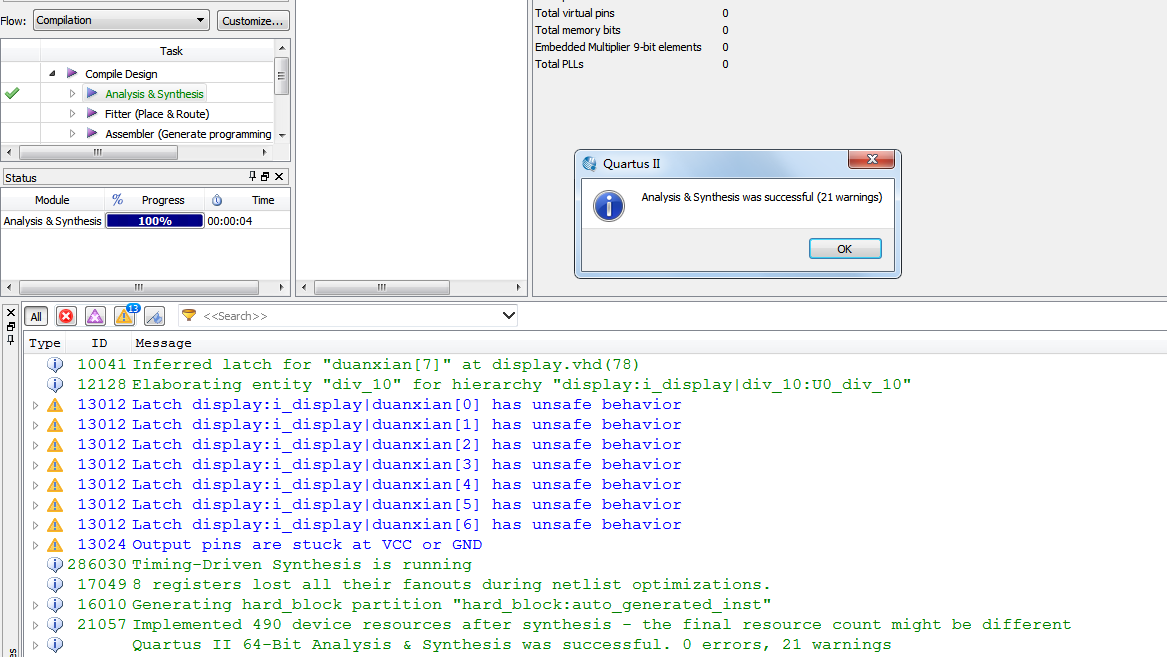

3. 程序编译

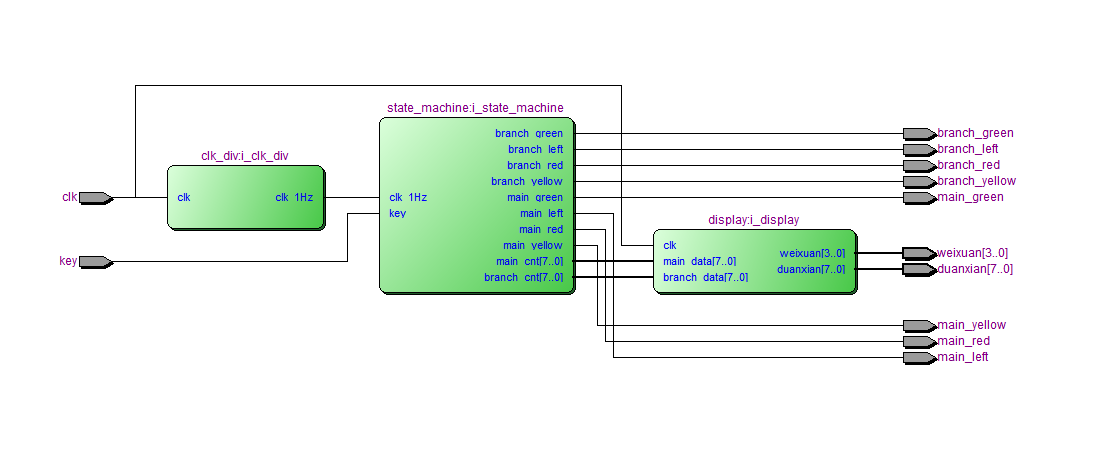

4. RTL图

5. 仿真图

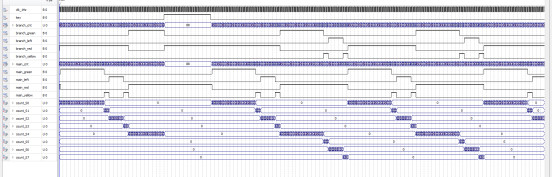

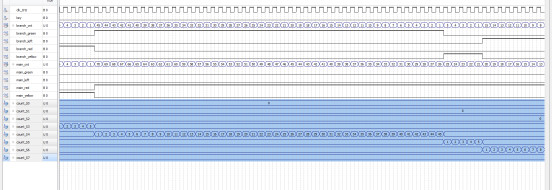

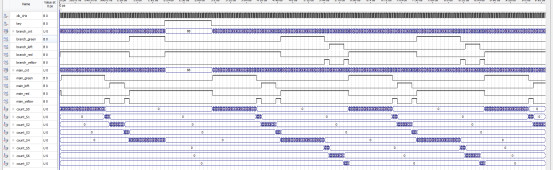

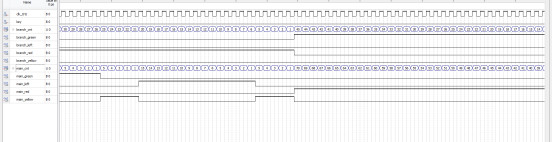

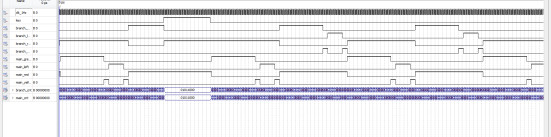

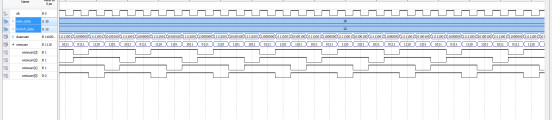

顶层模块仿真

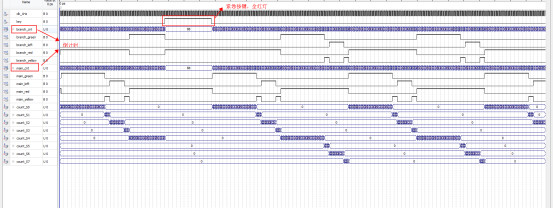

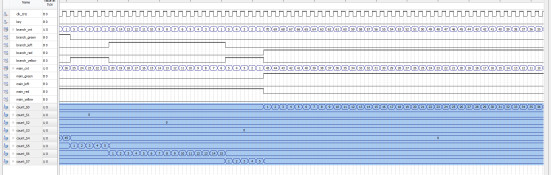

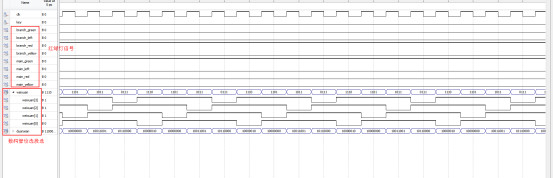

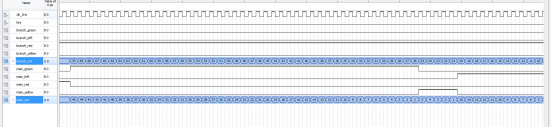

分频模块

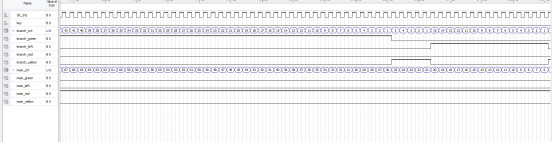

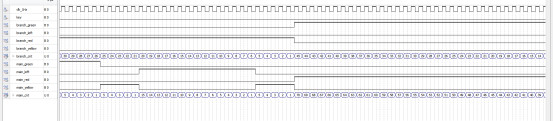

状态机模块

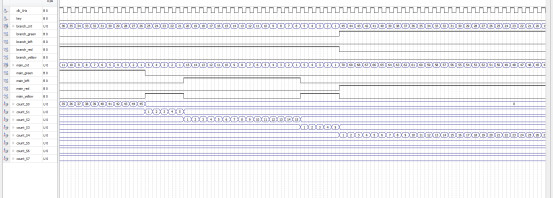

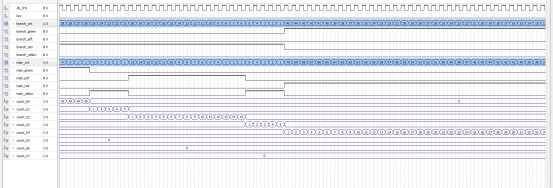

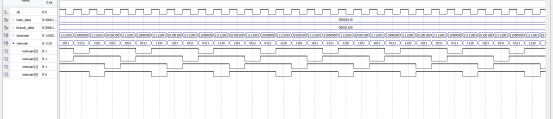

显示模块

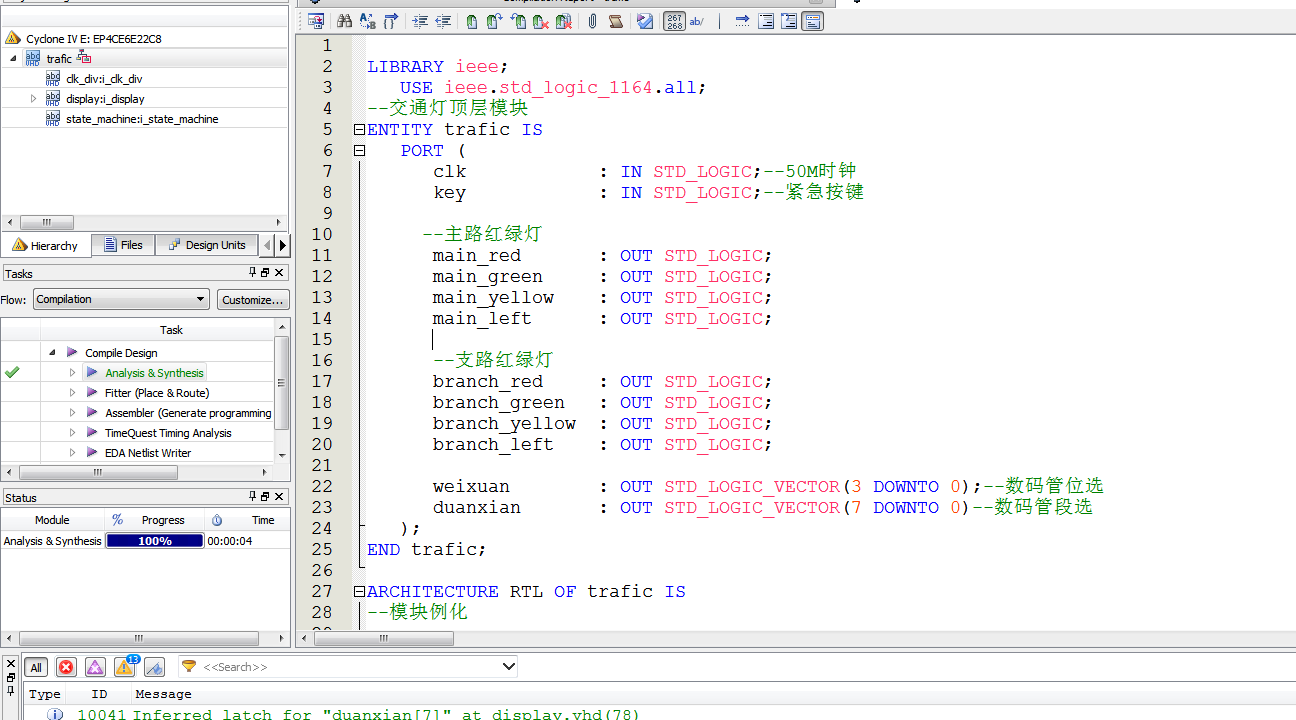

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --交通灯顶层模块 ENTITY trafic IS PORT ( clk : IN STD_LOGIC;--50M时钟 key : IN STD_LOGIC;--紧急按键 --主路红绿灯 main_red : OUT STD_LOGIC; main_green : OUT STD_LOGIC; main_yellow : OUT STD_LOGIC; main_left : OUT STD_LOGIC; --支路红绿灯 branch_red : OUT STD_LOGIC; branch_green : OUT STD_LOGIC; branch_yellow : OUT STD_LOGIC; branch_left : OUT STD_LOGIC; weixuan : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管位选 duanxian : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END trafic; ARCHITECTURE RTL OF trafic IS --模块例化 --状态机控制模块 COMPONENT state_machine IS PORT ( clk_1Hz : IN STD_LOGIC; key : IN STD_LOGIC; main_red : OUT STD_LOGIC; main_green : OUT STD_LOGIC; main_yellow : OUT STD_LOGIC; main_left : OUT STD_LOGIC; branch_red : OUT STD_LOGIC; branch_green : OUT STD_LOGIC; branch_yellow : OUT STD_LOGIC; branch_left : OUT STD_LOGIC; main_cnt : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); branch_cnt : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; --数码管显示模块 COMPONENT display IS PORT ( clk : IN STD_LOGIC; main_data : IN STD_LOGIC_VECTOR(7 DOWNTO 0); branch_data : IN STD_LOGIC_VECTOR(7 DOWNTO 0); weixuan : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); duanxian : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; --分频模块 COMPONENT clk_div IS PORT ( clk : IN STD_LOGIC; clk_1Hz : OUT STD_LOGIC ); END COMPONENT; SIGNAL clk_1Hz : STD_LOGIC; SIGNAL main_cnt : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL branch_cnt : STD_LOGIC_VECTOR(7 DOWNTO 0); BEGIN --分频模块 i_clk_div : clk_div PORT MAP ( clk => clk, clk_1Hz => clk_1Hz--1Hz );

源代码

点击下方的公众号卡片获取

1657

1657

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?