笔者在上一节介绍了CAN采样点的计算方法,那么在实际项目中如何验收验证呢?本节主要介绍采样点的测量方法和实际项目中的干货——误差来源分析!

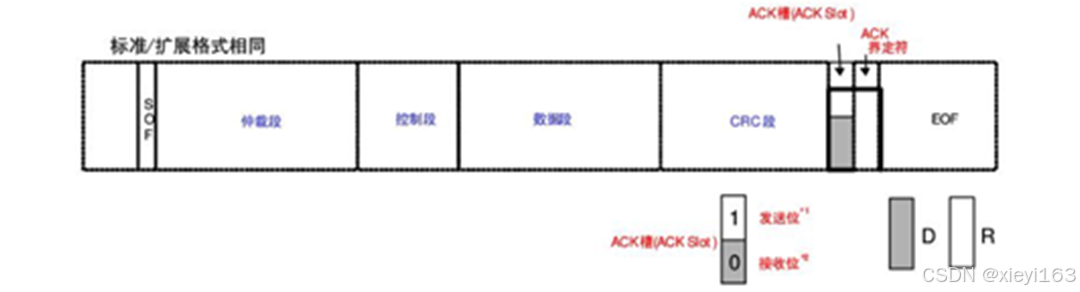

如下图,一个CAN帧被分为不同的段,其中 CRC_DEL段固定为隐性位,ACK_Slot段固定位显性位,对采样点的测量就是利用这个特性设计的。

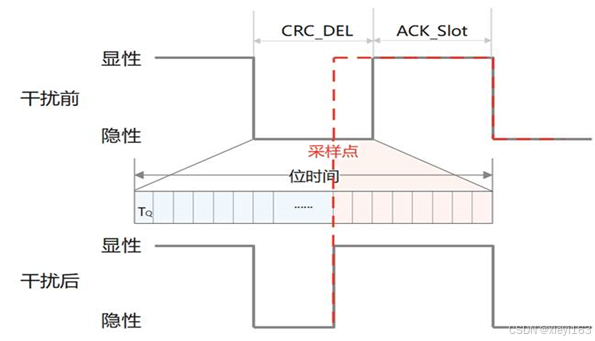

使用测试工具在CAN总线上发送特定干扰报文,然后检测DUT是否会发送错误帧。业界当前一般使用Vector的VH6501设备进行干扰,周期发送高优先级报文,在每个周期,微调CRC_DEL位长度,使其缩短1个VH6501时钟长度,并同时将后一位ACK_Slot位长度增加1个VH6501时钟长度。由于CRC_DEL位固定为隐性位,ACK_Slot位固定位显性位,当ACK_Slot显性位移到DUT采样点位置时,就会被DUT采样到并判定CRC_DEL位为显性位,DUT检测为格式错误,就会向总线发送错误帧,测试工具检测到DUT发送的错误帧时,则结束测试,并记录调整的次数为n,然后根据调整次数计算出DUT的采样点。

以上的测量方法理论上可以测量出节点的采样点,网络上也有很多博主都有所介绍,甚至更详细的介绍测试步骤,感兴趣的朋友可以自行搜索。我们下面重点分析下实际项目中采样点测量结果会和理论值存在的误差,误差来源于以下几个方面:

- 采样次数产生的误差

采样次数指每个bit总线被采样的次数,对于ST,NXP等芯片采样次数一般可配置为1次或三次,GD32F305芯片采样次数被设计为固定3次;

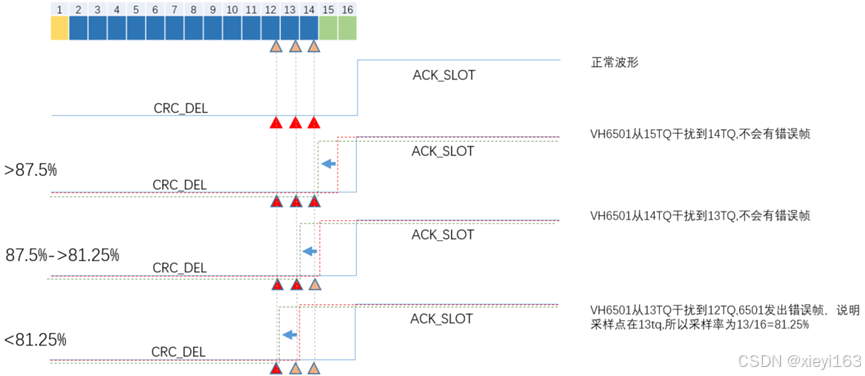

如下图,GD芯片采样次数为3次,比如对于采样率为87.5%的配置下(SYNG:1, BS1:13, BS2:2),CAN控制器会分别在12Tq,13Tq,14Tq的节点进行采样,以其中2次以上的采样结果为最终结果;结合采样方法看会有1Tq的误差

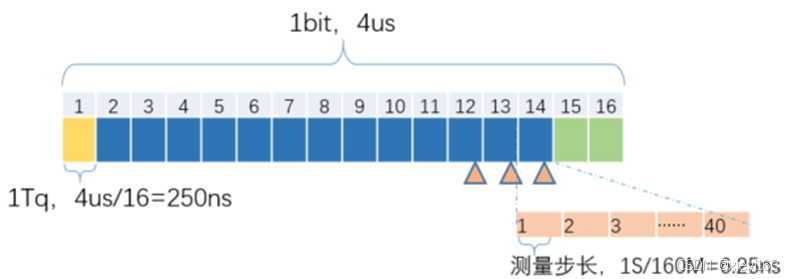

2. 测量精度带来的误差,我们当前使用Vector的VH6501,主频为160M,所以ACK_Slot位长度增加1步的时间长度为1/160MHz = 6.25ns.

系统使用波特率为250K,所以每Bit的时间长度为1s/250 = 4us=4000ns,所以此处会有6.25/4000=0.15625%的误差

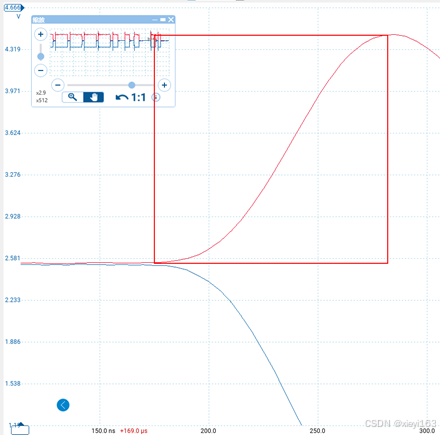

3. 网络电器特性的误差,在实际的CAN网络中,电平从隐性到显性的变化也需要时间,在做显性位或隐性的仲裁时,需要电平差值达到一定的阈值,所以这个过程中也会有测量误差的产生,11898中总线频率250K时规定的上升下降时间为200ns-500ns下图为现场采集的一段由隐性位变为显性位的电平,可以看到上升沿时间约110ns, 所以可能会有110ns/4000ns=2.75%的一个误差。

以上都是测量方法中可能存在的误差来源,在实际项目环境中CAN网络本身也会存在一定的偏差(注意是波形本身存在的偏差不属于测量误差),我们在后面继续探讨!

1493

1493

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?