一、新建工程

1、新建两个文件夹,par用来放工程文件,rtl用来放源代码。

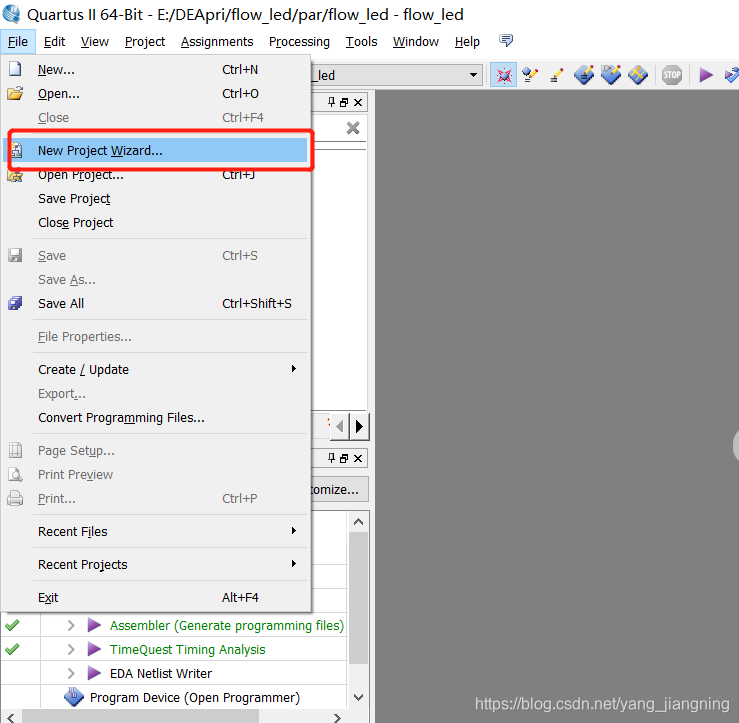

2、选择新建工程向导。

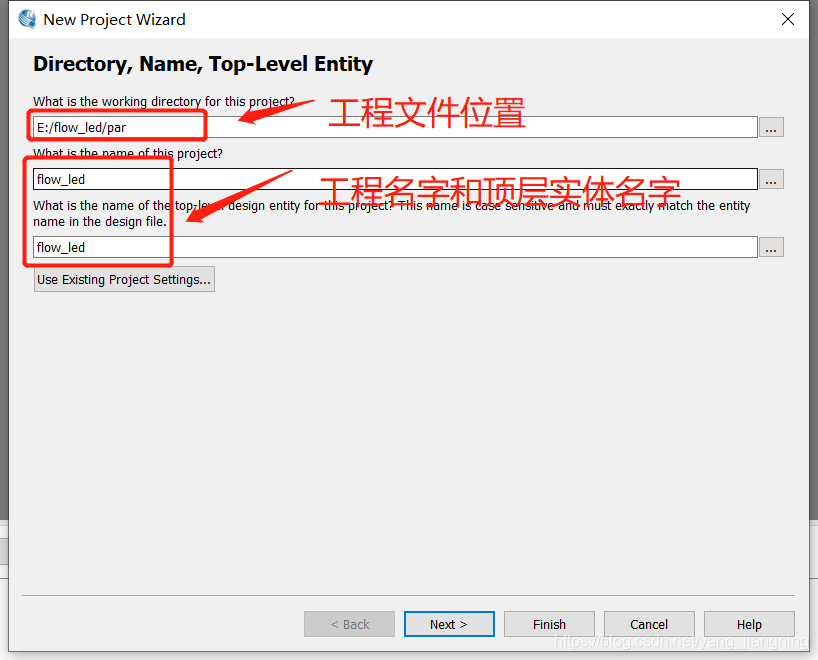

3、设置工程文件位置和工程名字。

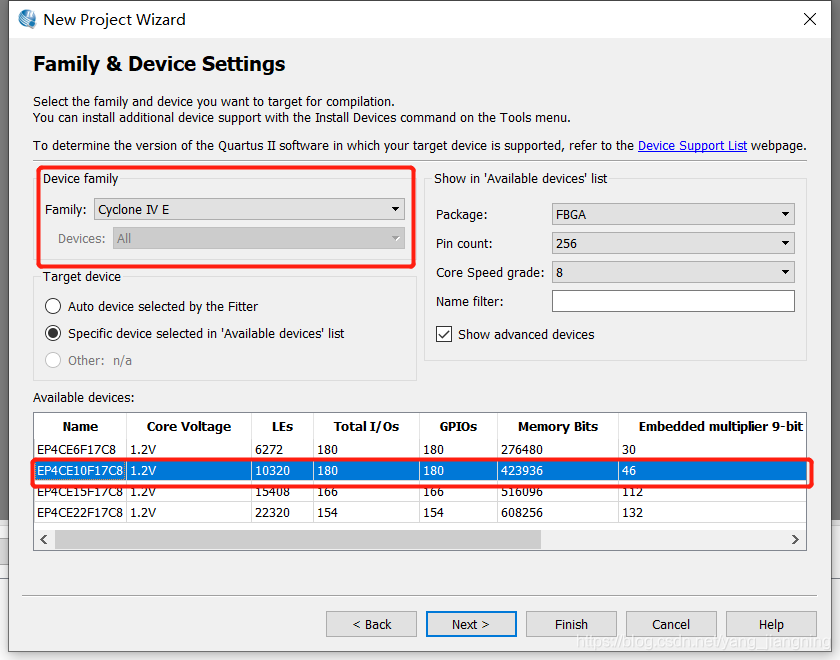

4、选择FPGA芯片型号

5、选择EDA工具,比如仿真工具modelsim

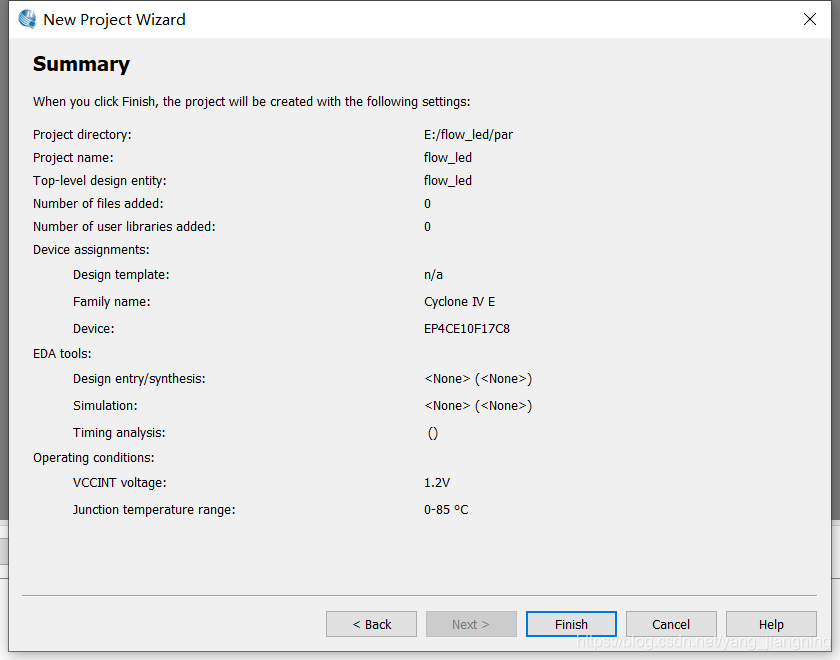

6、查看配置信息报告。

7、然后点击finish完成工程建立。

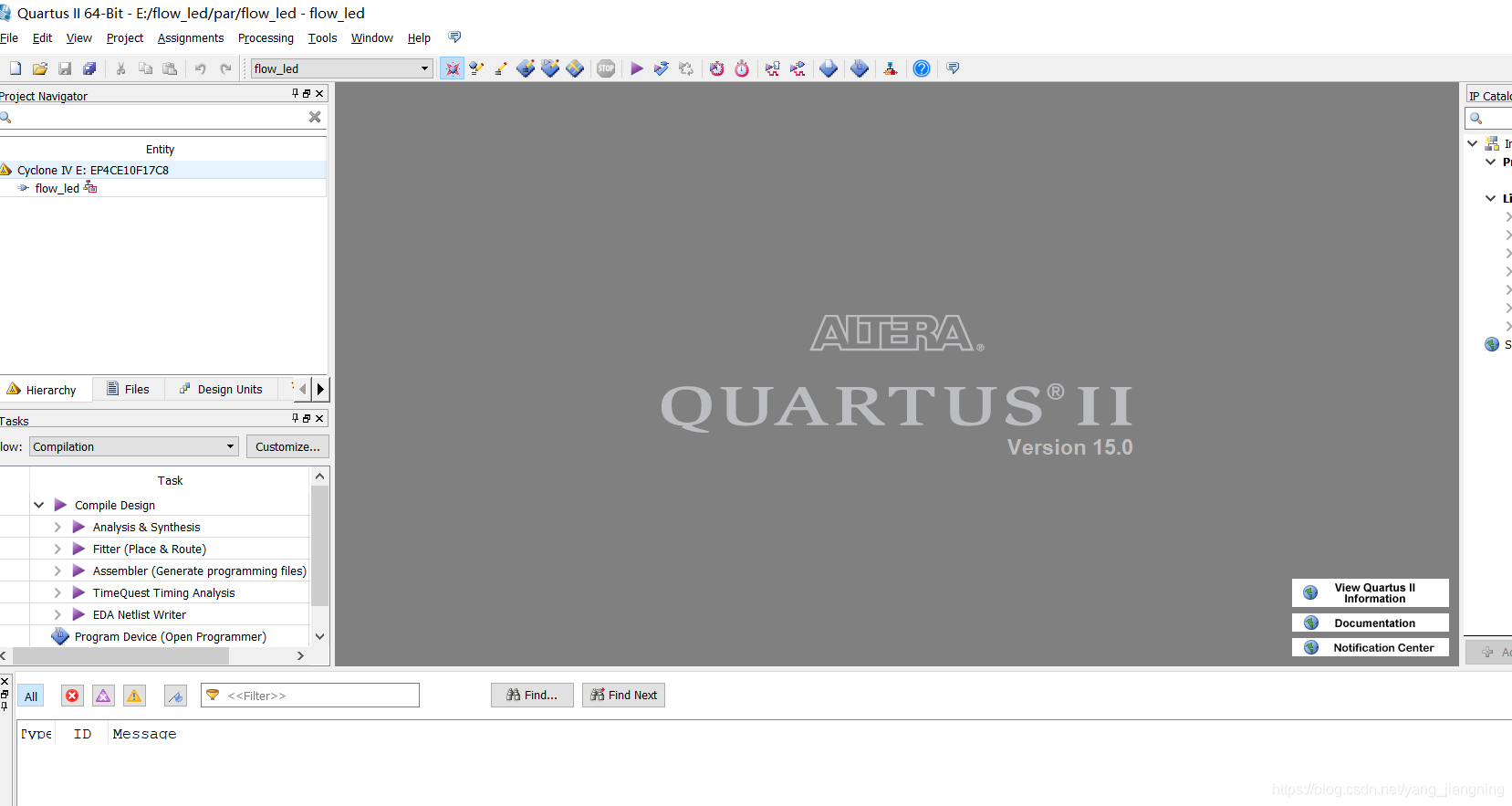

二、设计,配置,综合,编译等

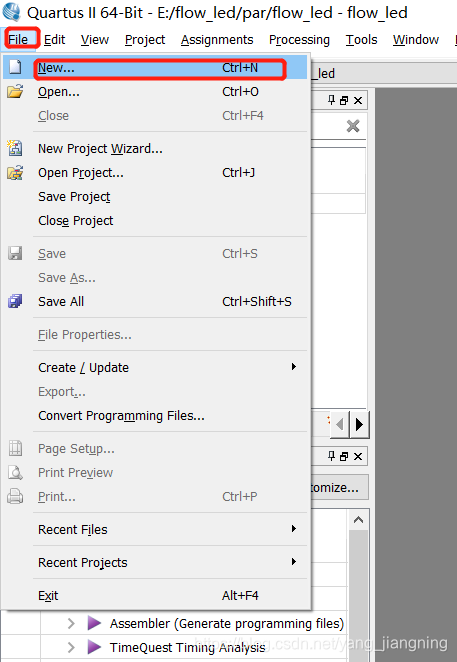

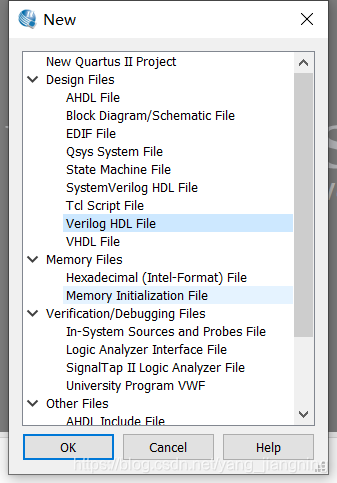

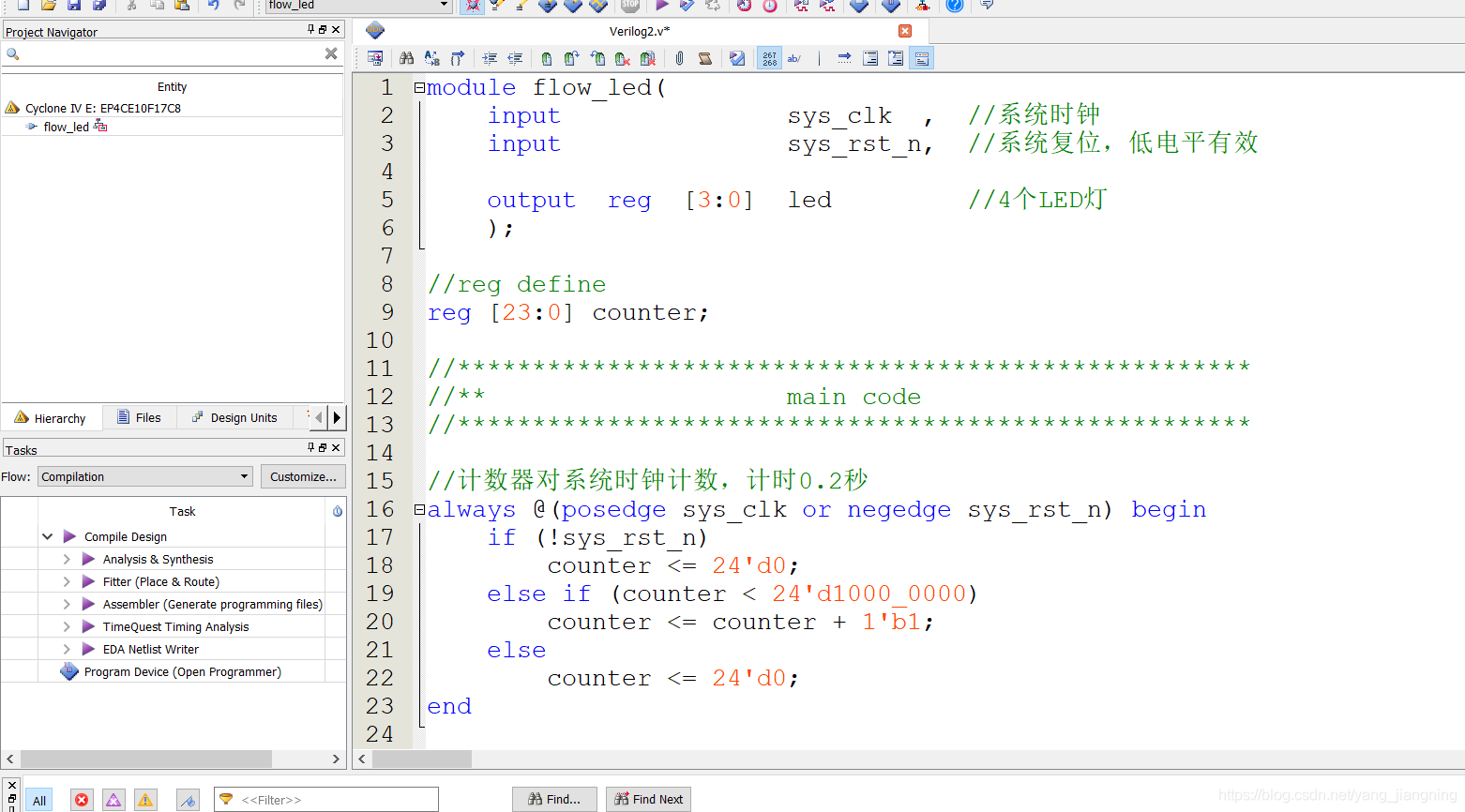

1、新建一个Verilog HDL 文件。

2、编写Verilog程序。

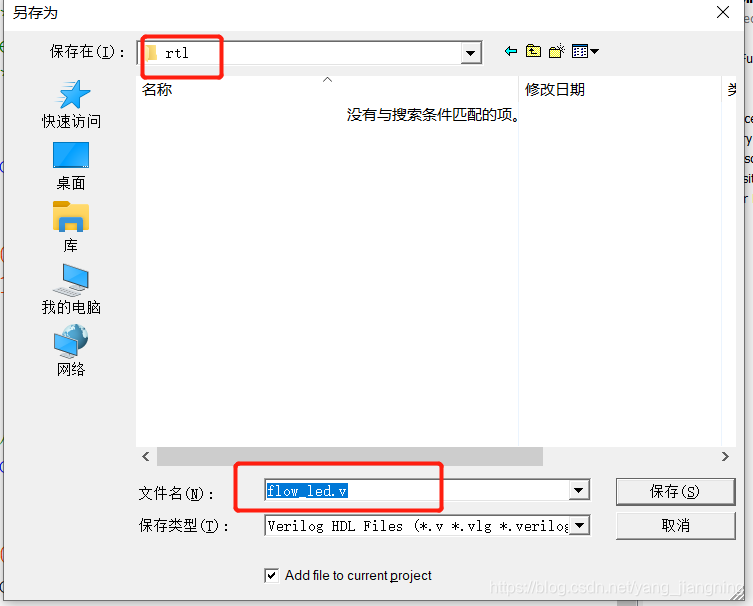

3、编写完成后,另存为flow_led.v文件放在rtl文件夹中

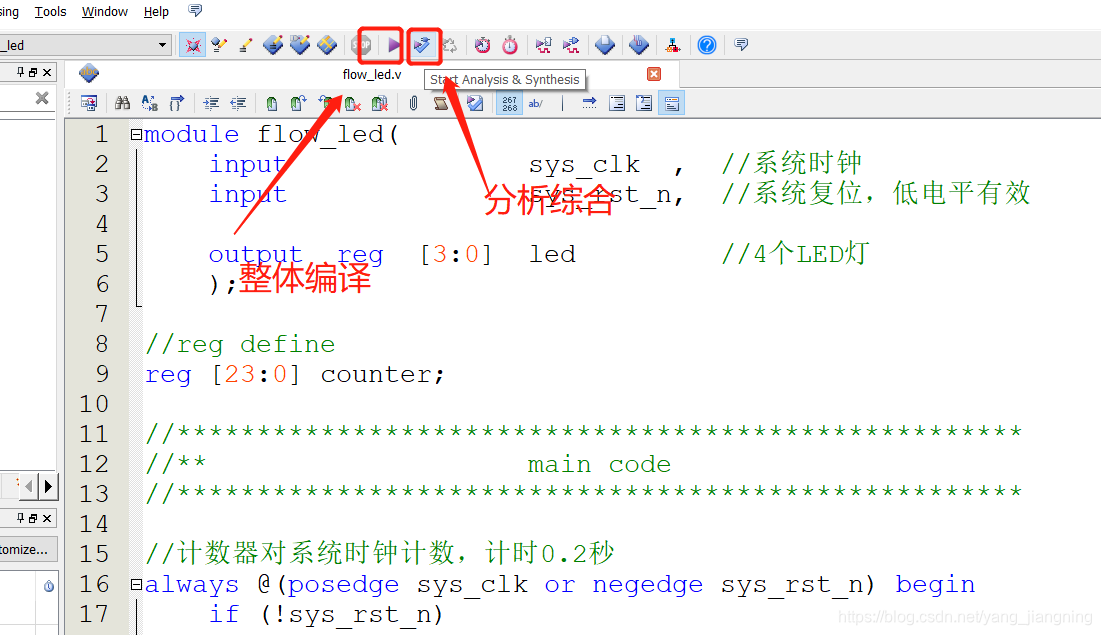

4、保存完后进行分析综合(或者整体编译,但是耗时较长,一般分析综合即可)

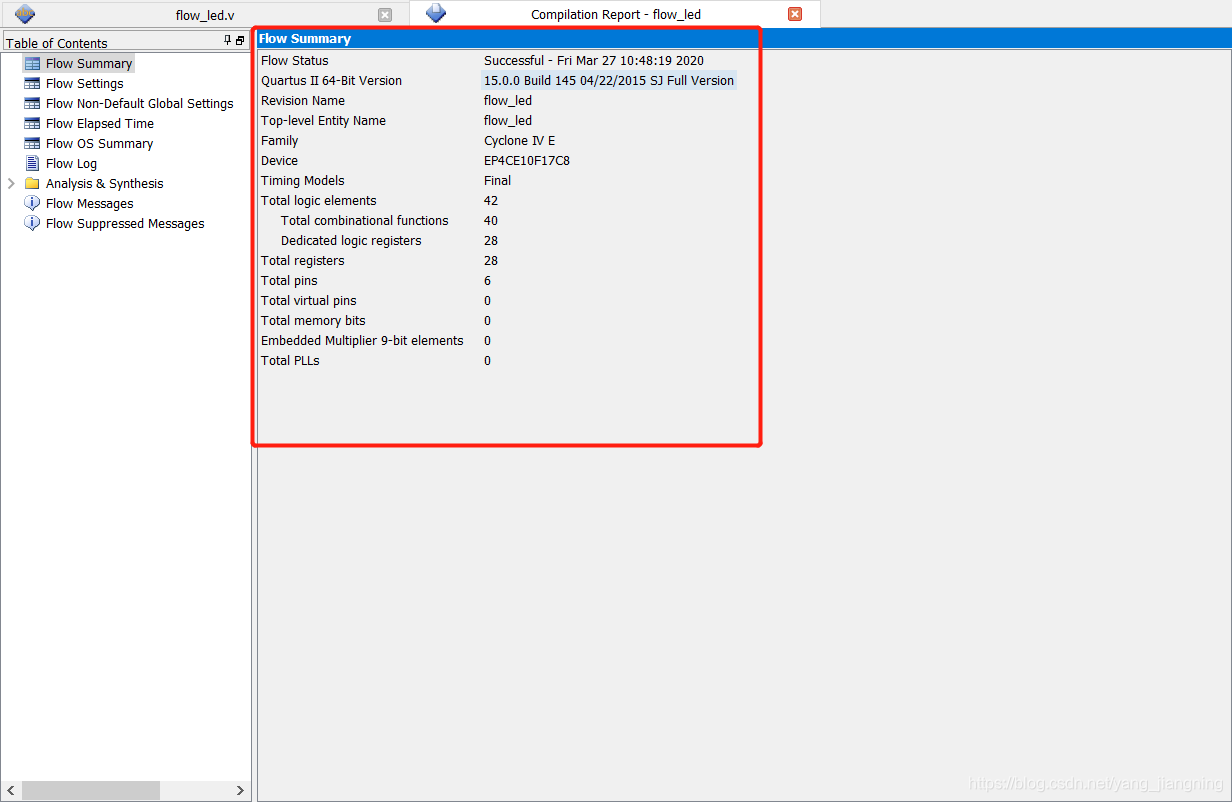

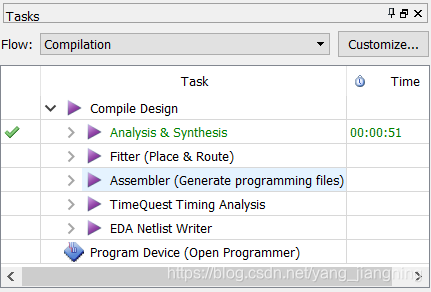

5、综合完成

编译流程窗口【Analysis & Synthesis】前面的问号会变成对勾,表示编译通过。(如下图)

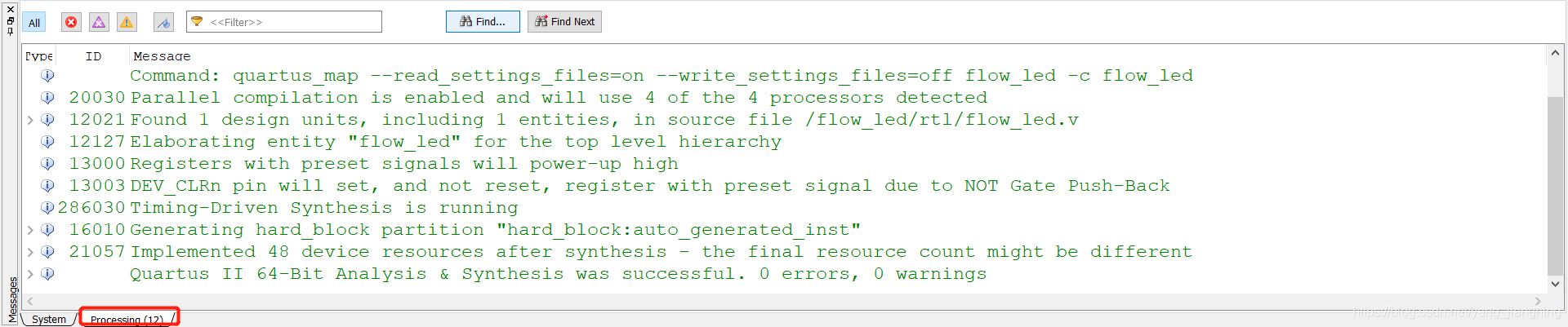

我们可以查看打印窗口的“Processing”里的信息。包括各种“Warning”和“Error”。“Error”是必须要关心的,“Error”意味着代码有语法错误,后续的编译将无法继续,如果出现错误,可以双击错误信息,此时编辑器会定位到语法错误的位置,修改完成后,重新开始编译;而“Warning”则不一定是致命的,有些潜在的问题可以从“Warning”中寻找,如果一些“Warning”信息对设计没有什么影响,也可以忽略它。(如下图)

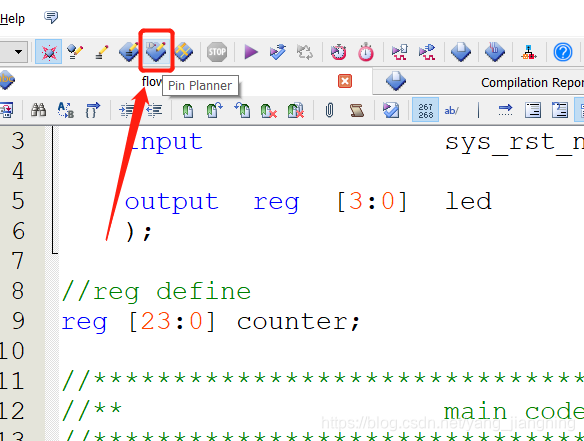

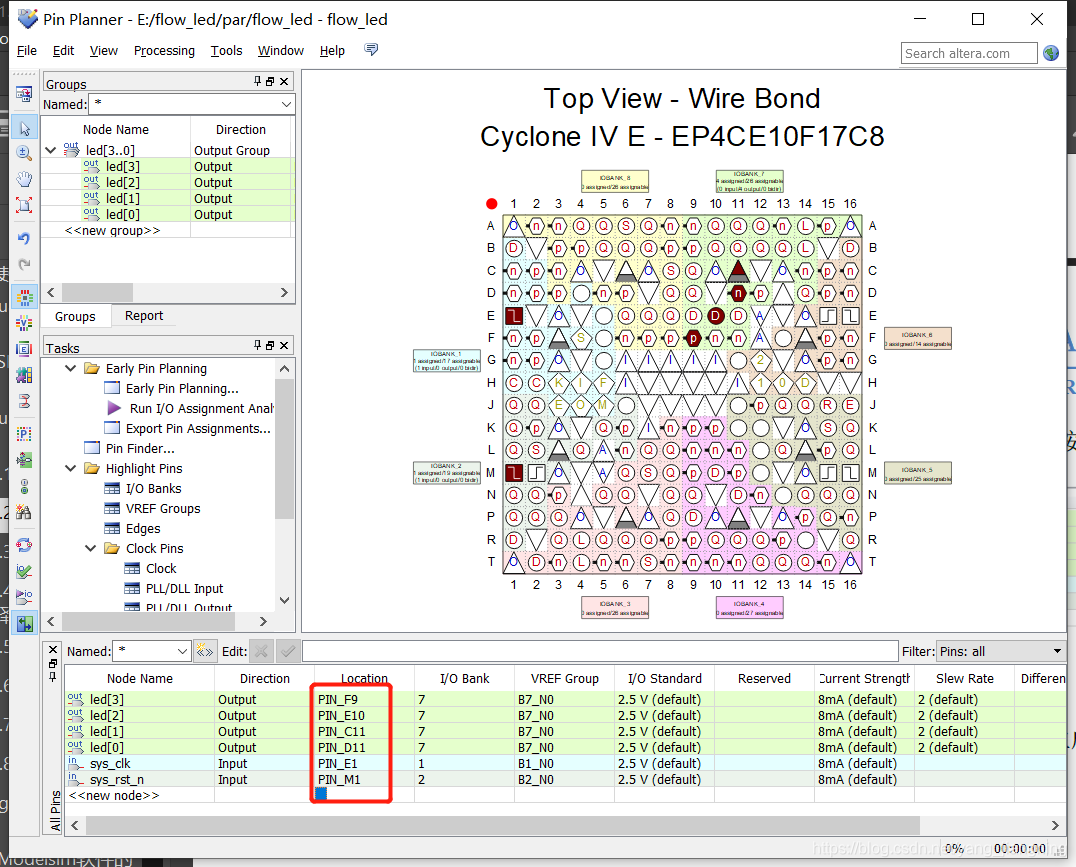

6、管脚约束

根据原理图进行管脚配置。

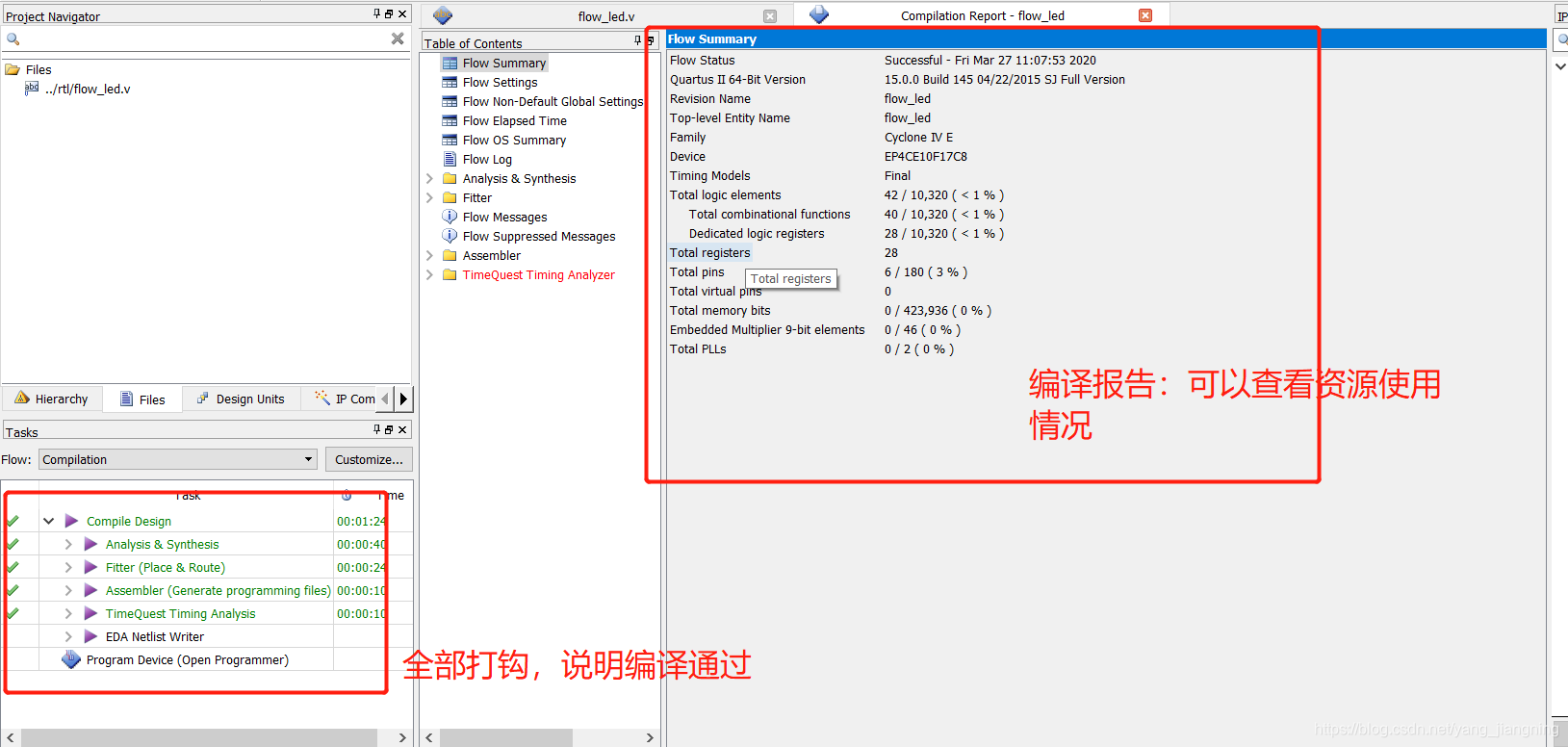

7、管脚约束完后对整个工程进行一次编译

三、下载程序

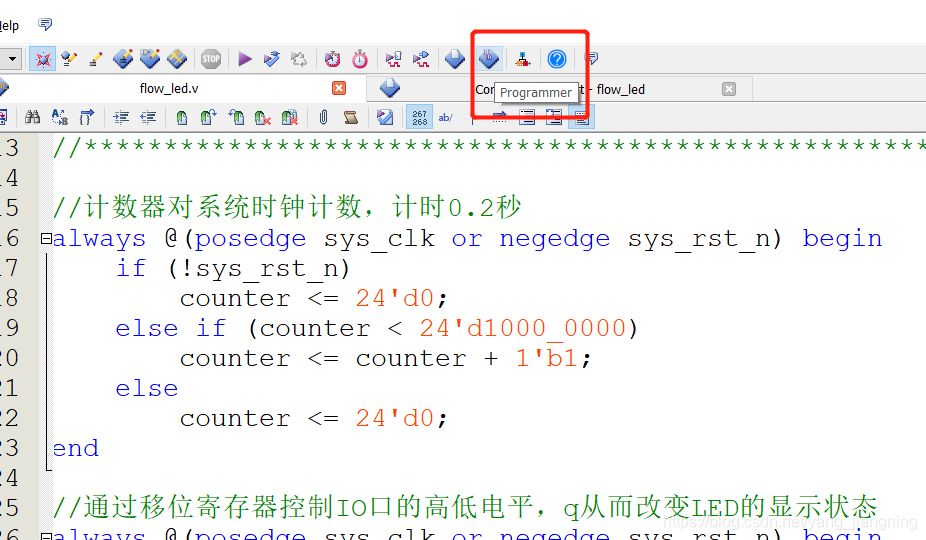

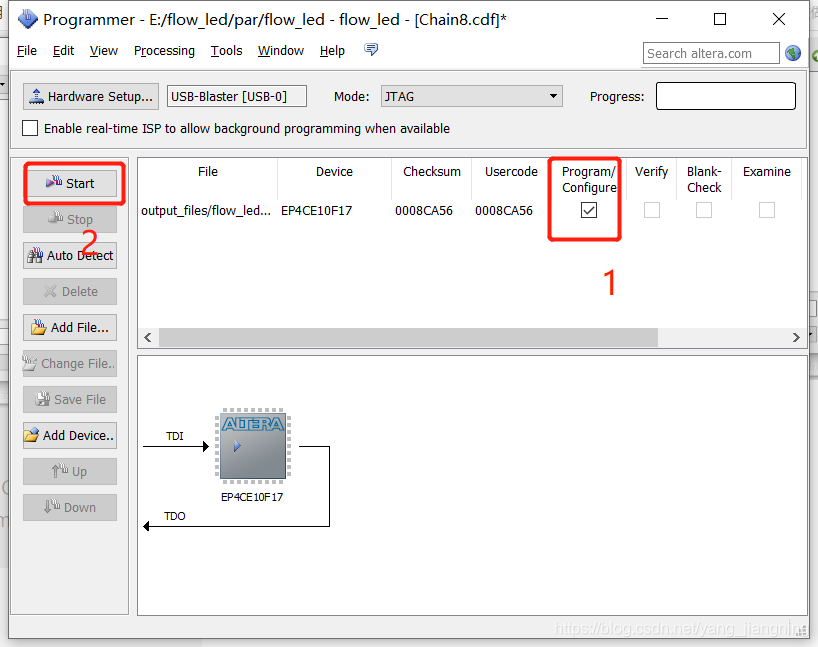

1、选择工具programmer

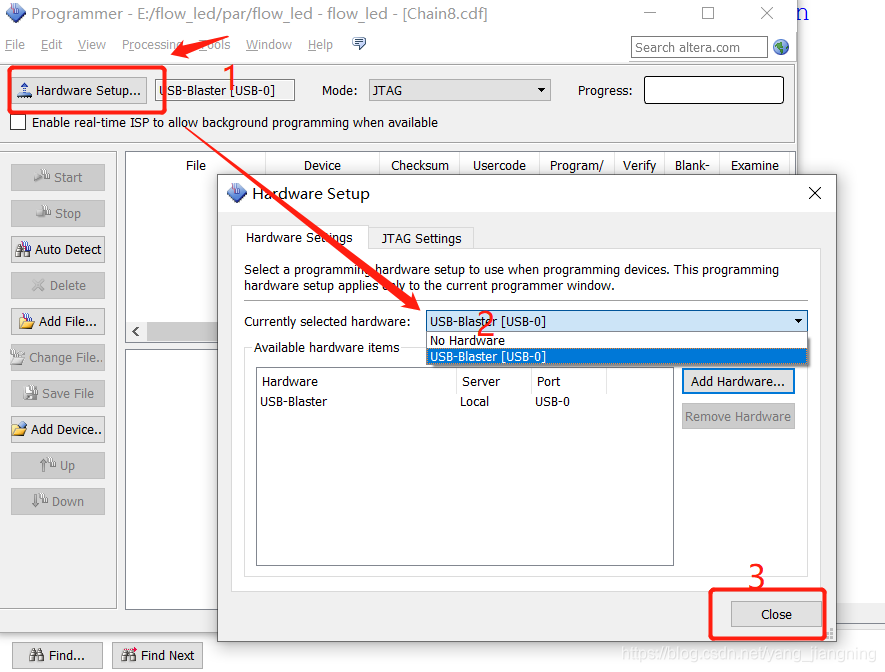

2、如图,选择USB-blaster

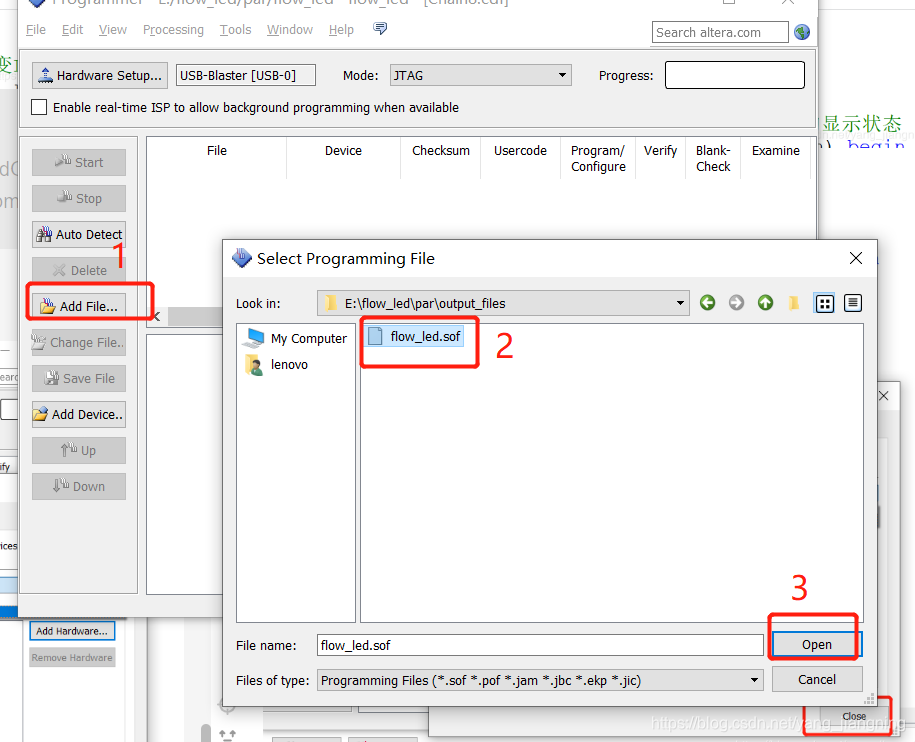

3、添加sof文件

4、在对应的文件下打钩,然后点击start

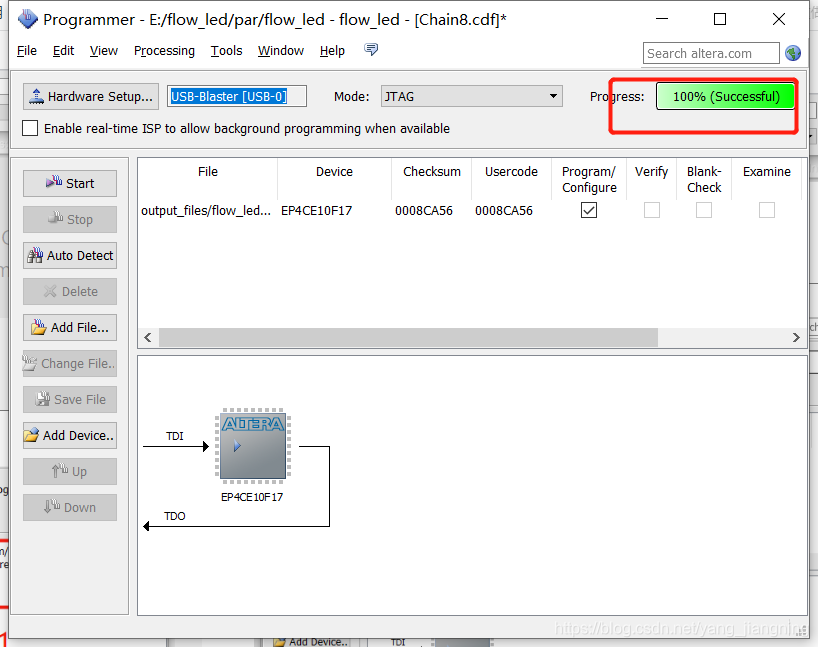

5、达到100%时,完成

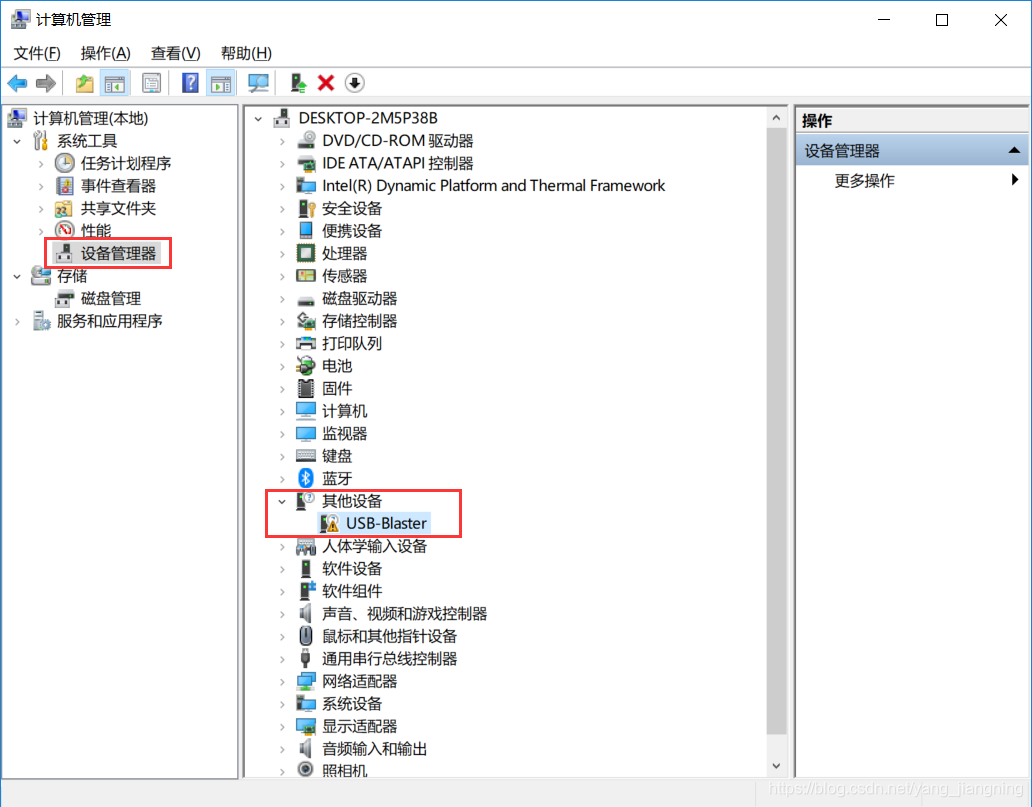

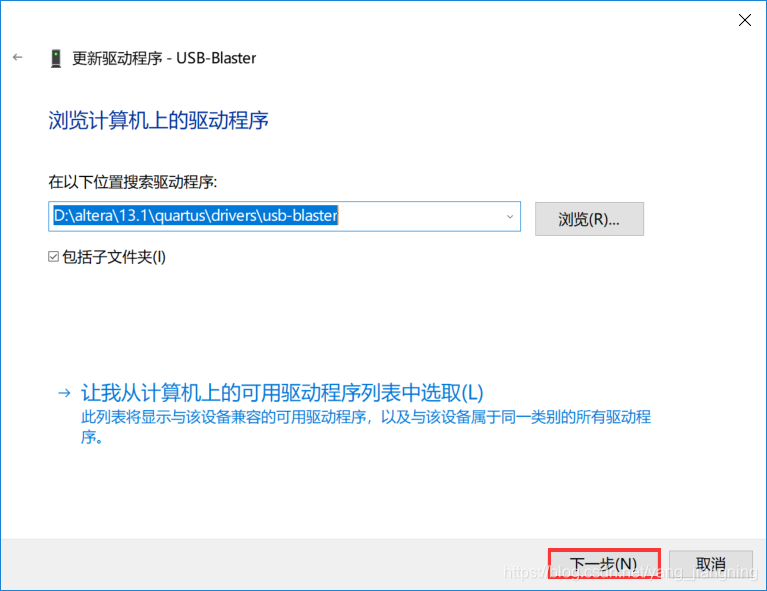

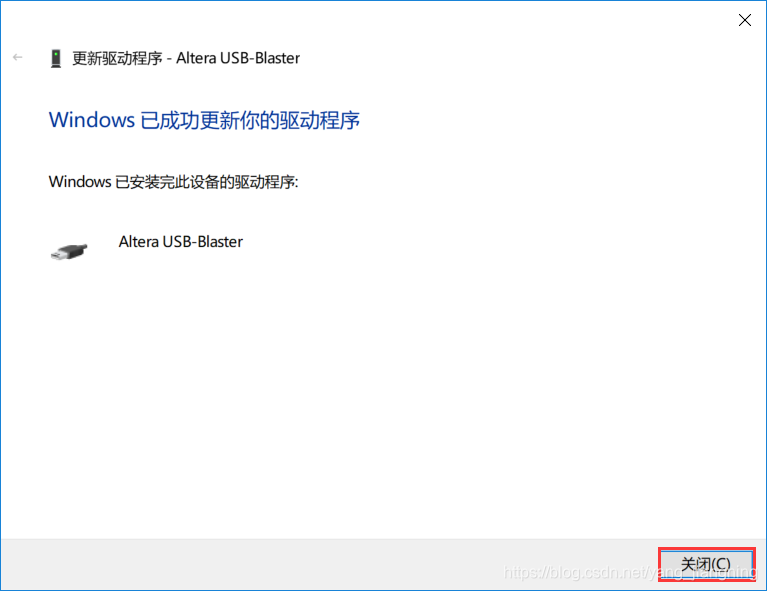

四、 USB-Blasterd驱动的安装

USB Blaster是Altera FPGA的程序下载器,通过计算机的USB接口对Altera的FPGA和配置芯片进行编程、调试以及下载等操作。电脑必须在安装驱动后,USB Blaster才能正常工作。

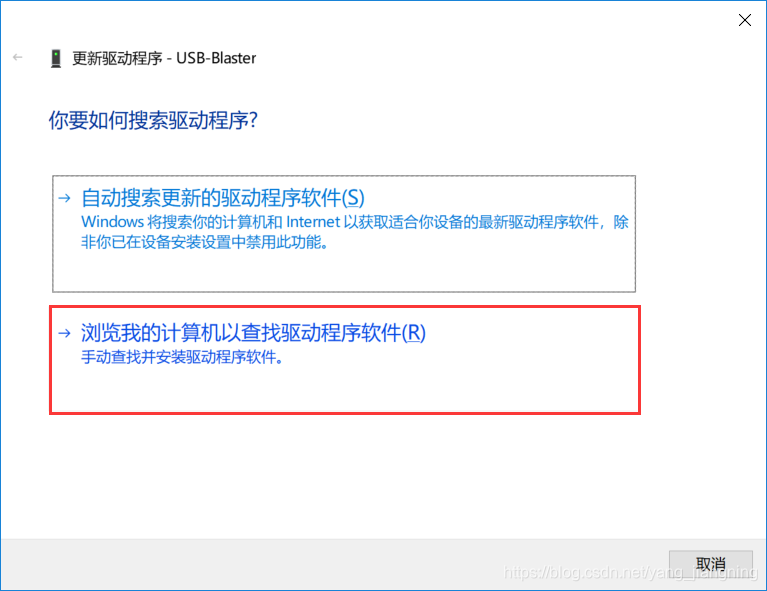

1、 ctrl+x打开设备管理器

驱动程序的路径为Quartus软件安装目录D:\altera\13.1\qurtus\drivers\usb-blaster。

安装完成。

2248

2248

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?