一、实验目的

1.熟悉Candence IC514软件,学会ac仿真,dc仿真,查看每点的电流电压。

2.学会各种Cascode放大器的电气特性,根据仿真现象使用理论对其分析 。

3.将Cascode放大器与Common_Source放大器进行比较,了解两个电路的优劣,学会更具具体问题进行相应的设计。

4.学习电压偏置和电流偏置的基本设计方法并分析。

二、实验环境

集成电路设计实验室;Red Hat Enterprise linux5、Cadence IC Design Tools 5.10.41

三、实验原理

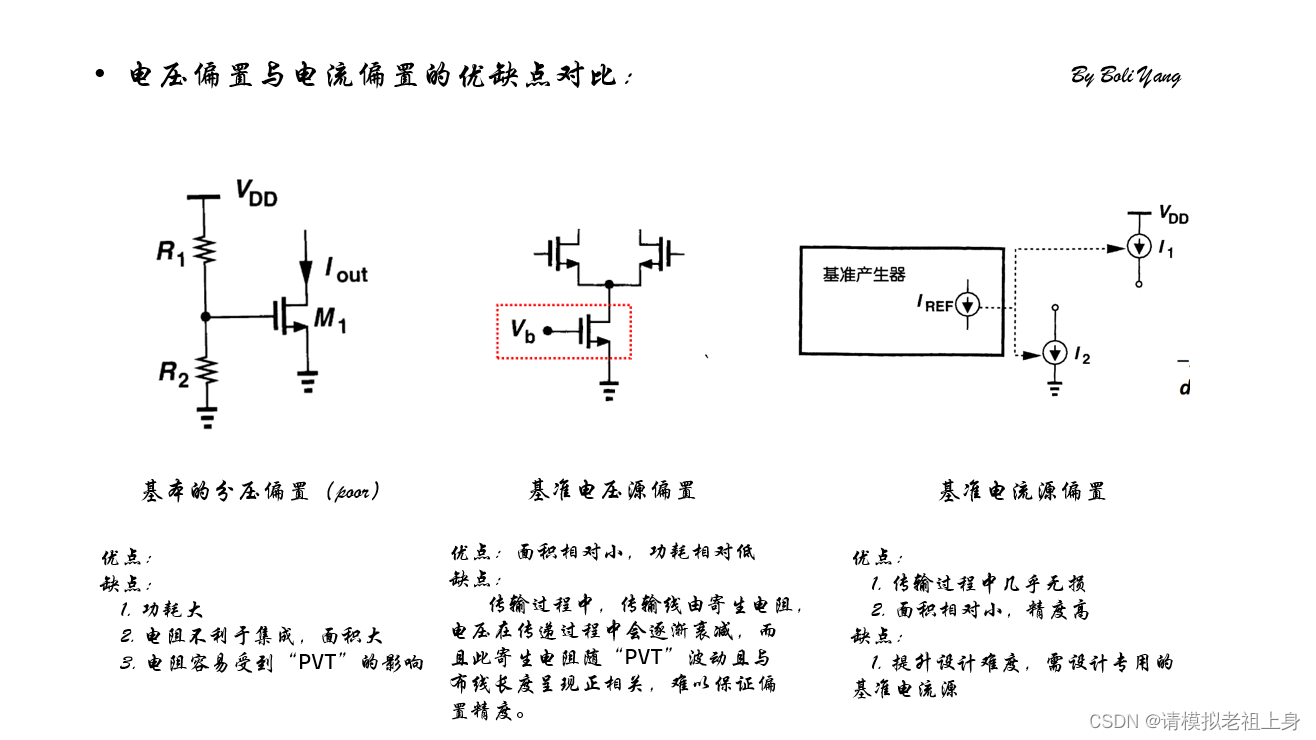

1. 电压偏置与电流偏置

图1 基本偏置方法的优缺点总结

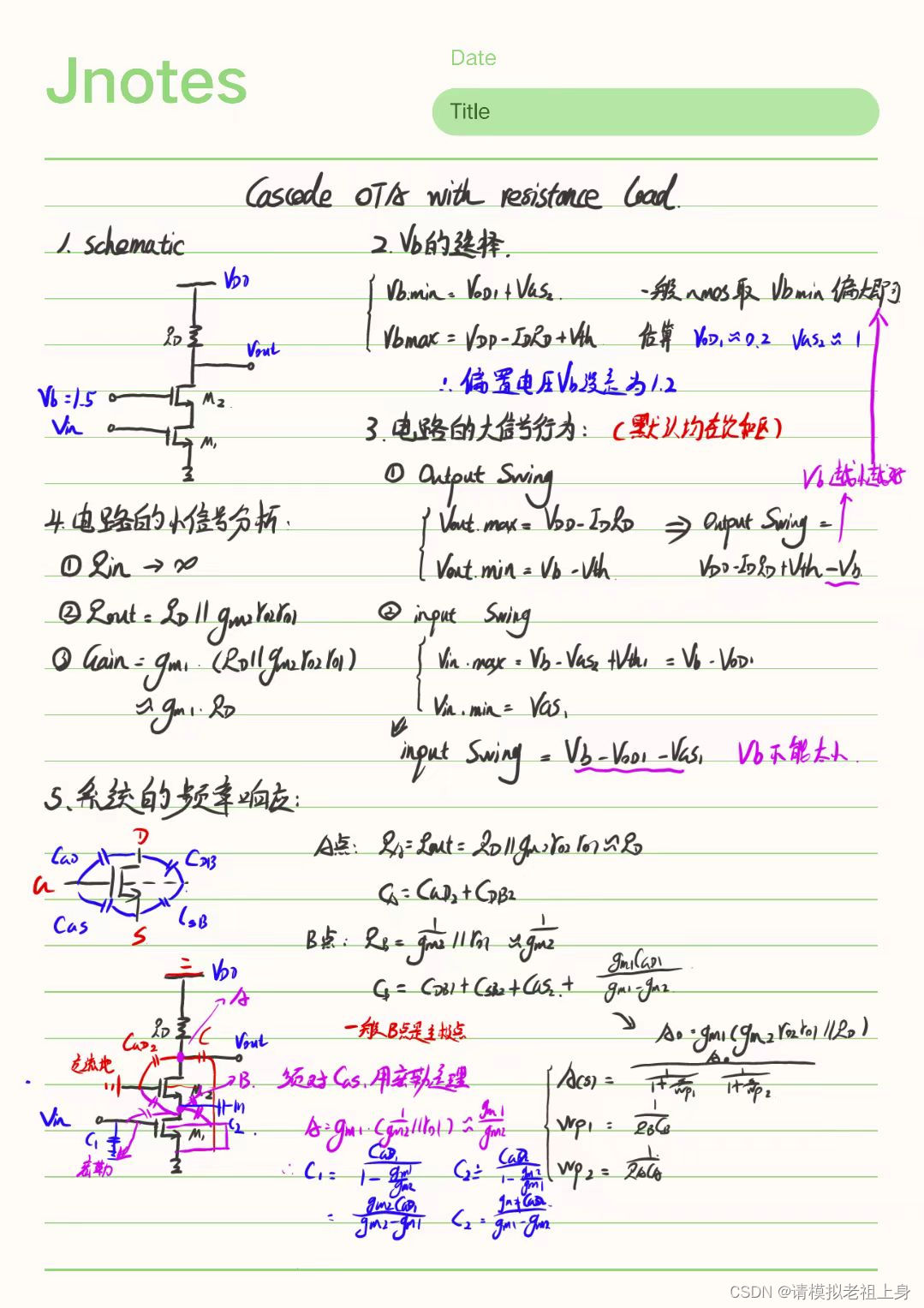

2. res做负载的 Cascode 放大器电路详解:

图2 res做负载的 Cascode 放大器电路解析

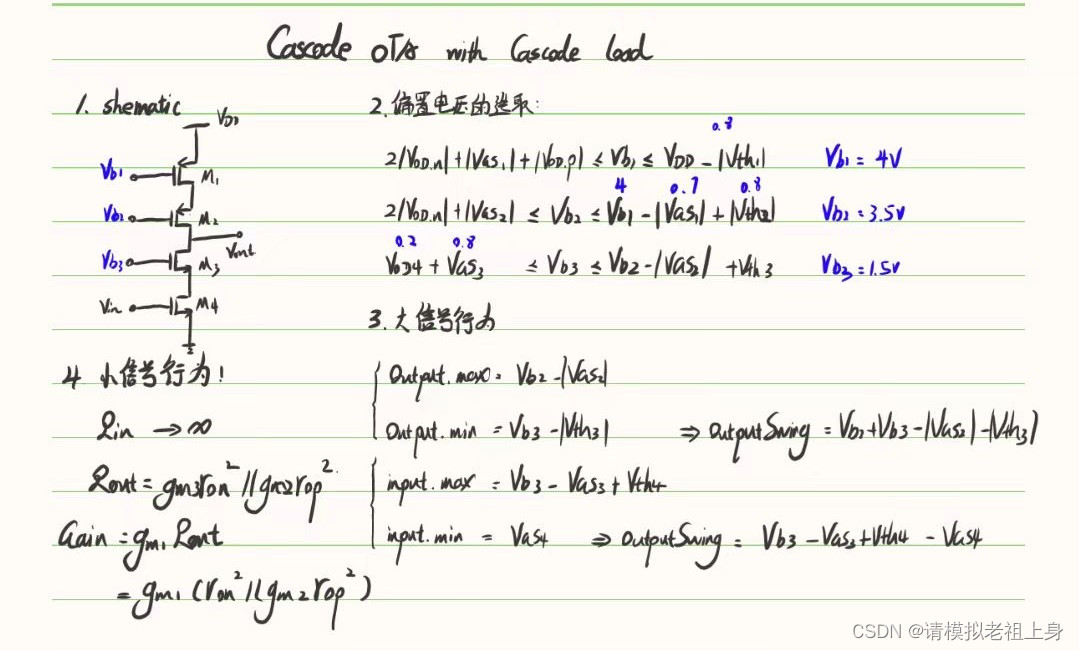

3. pmos二极管连接做负载的Cascode放大器详解:

图3 PMOS二极管连接的 Cascode 放大器电路解析

4. Cascode放大器电路详解:

图4 Cascode负载的 Cascode 放大器电路解析

5. Folded Cascode电路详解:

图5 Folded Cascode电路 解析

四、实验步骤

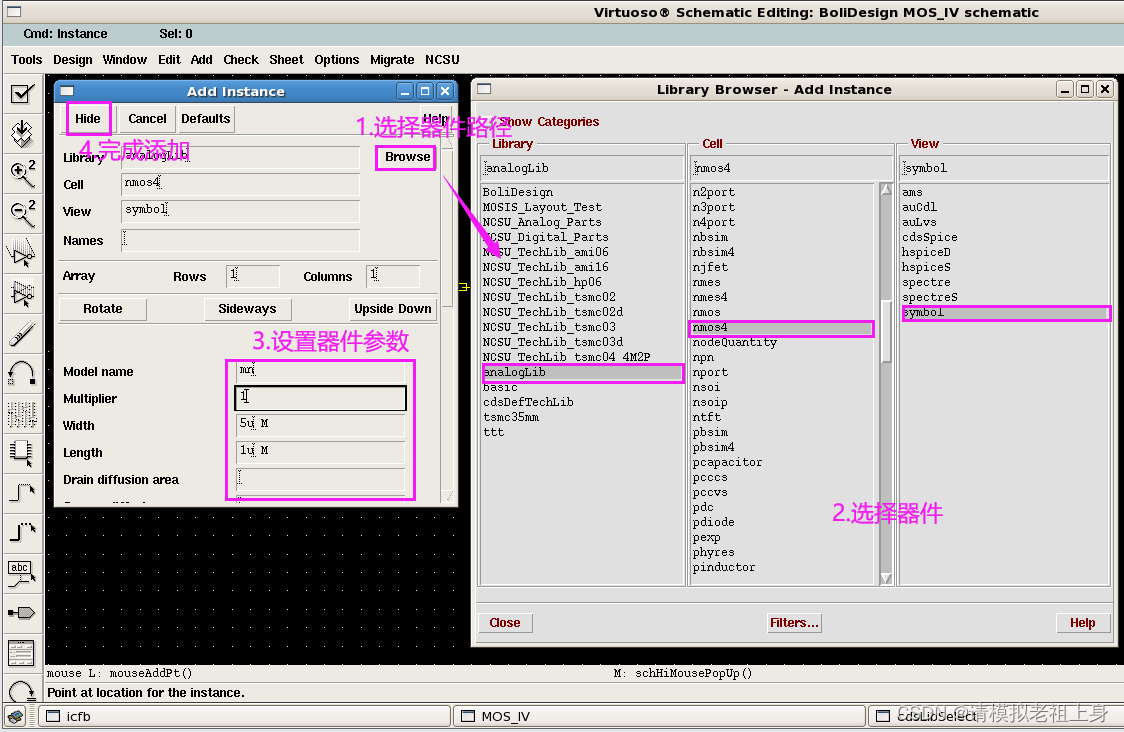

1.新建“cell view”,放置元器件,绘制schematic

|

图6 新建cell view |

图7 在图形界面中添加器件 |

|

图8 依次添加器件并连接完成 |

图9 依次添加器件并连接 |

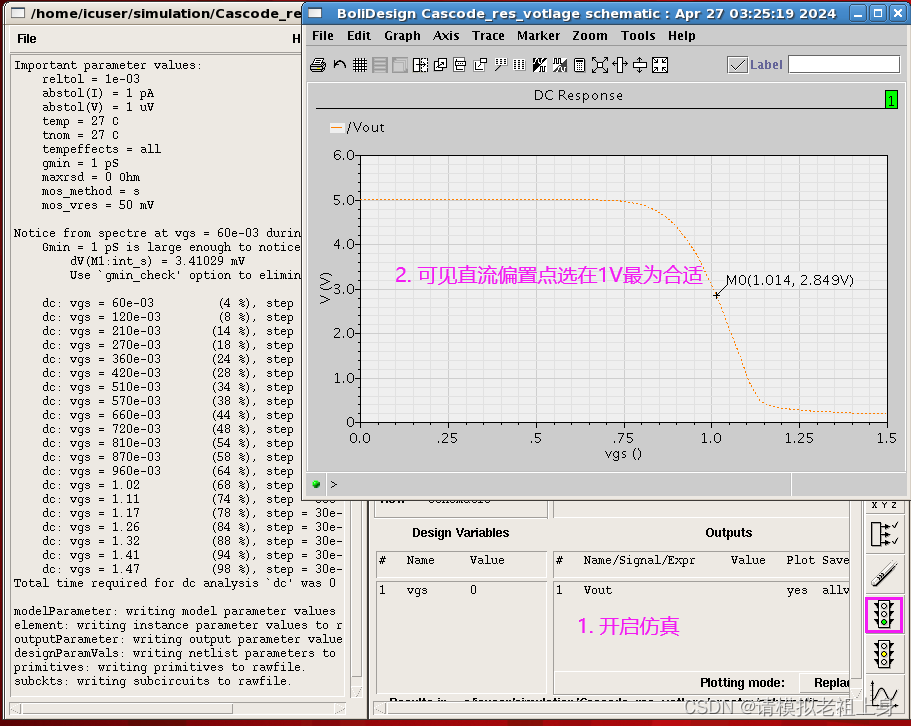

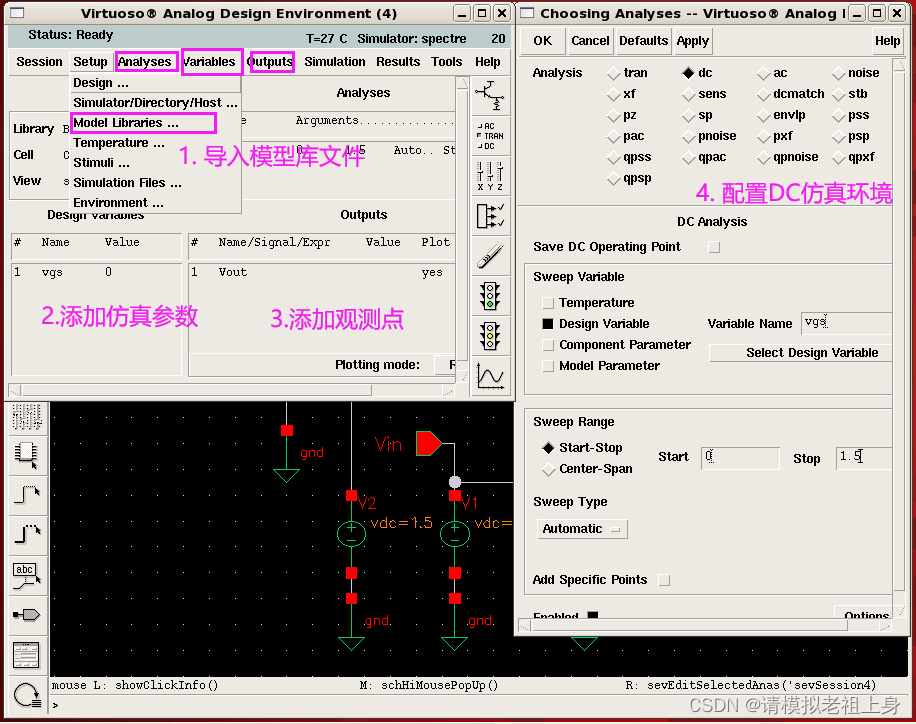

2.【实验一】res做负载的Cascode放大器

|

图10 DC仿真原理图 |

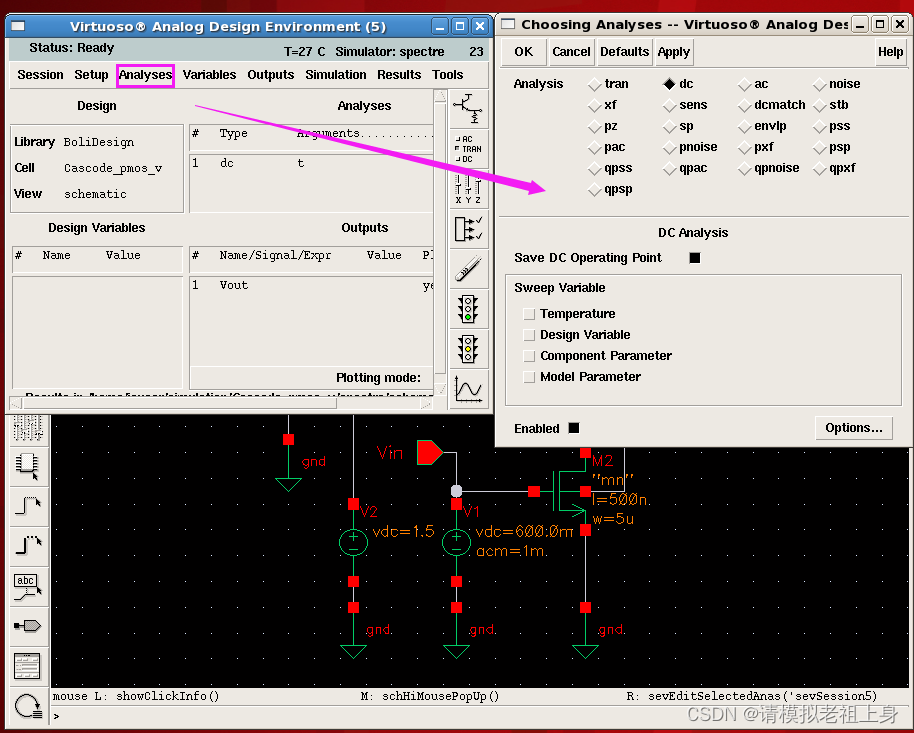

图11 dc仿真环境配置,寻找最佳直流工作点 |

|

图12 DC 仿真结果,设置直流静态工作点为1V |

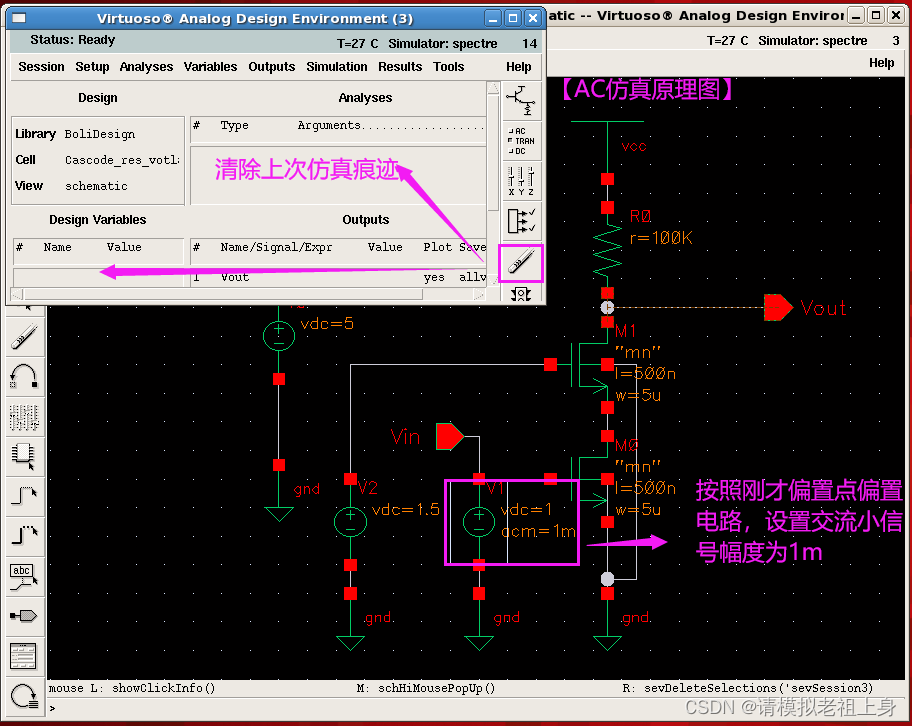

图13 AC仿真原理图 |

|

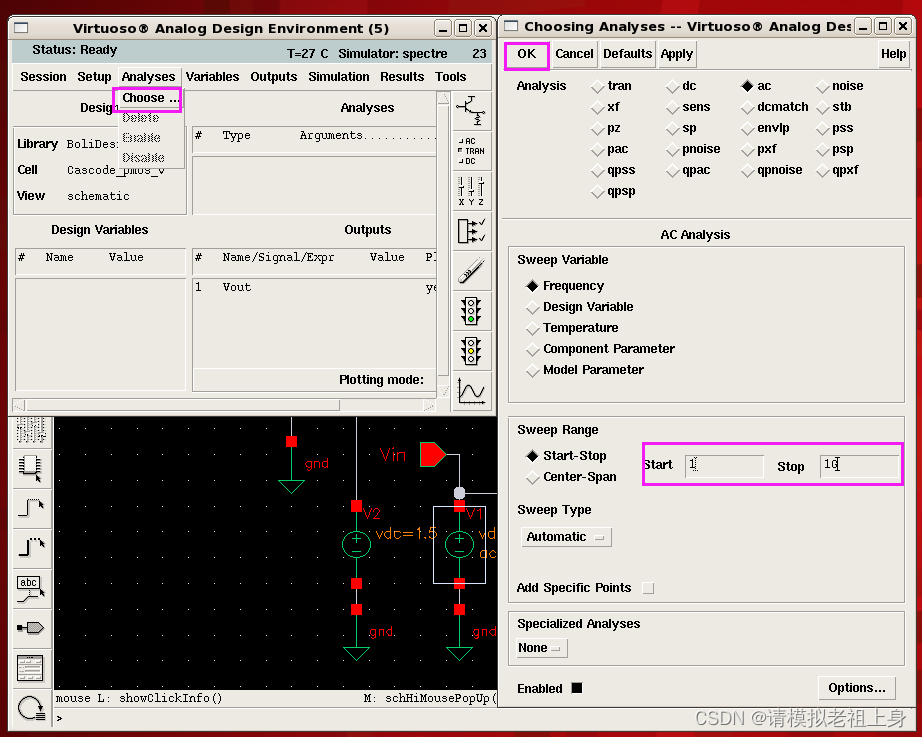

图14 AC仿真环境配置 |

|

|

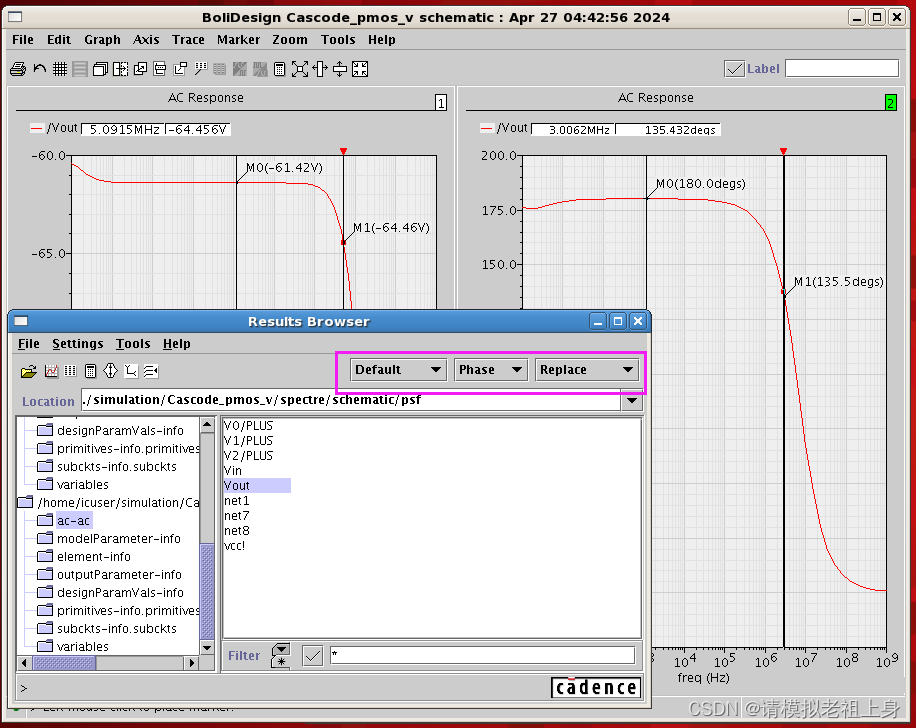

图16 Browser工具调出幅频与相频曲线 |

图17 配置DC仿真环境,查看当前各点的电压和电流(结果在第四部分) |

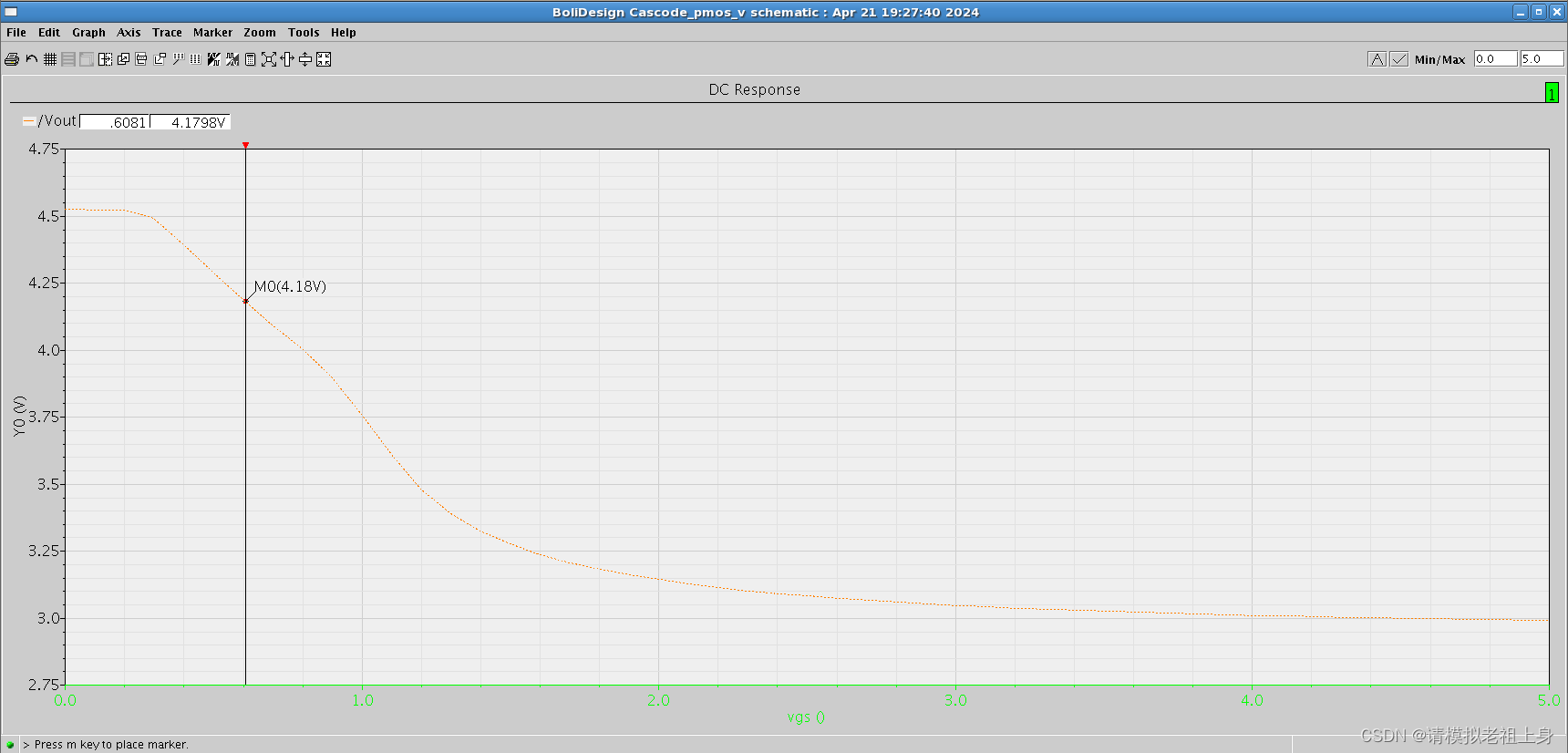

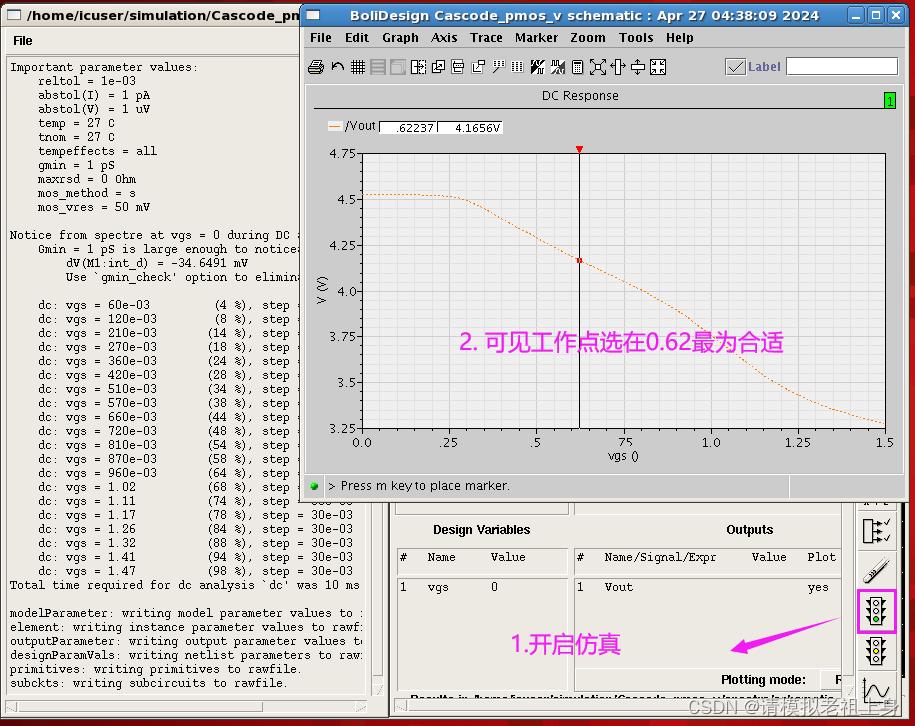

3.【实验二】pmos二极管连接做负载的Cascode放大器

|

图18 DC仿真原理图 |

图19 dc仿真环境配置,寻找最佳直流工作点 |

|

图20 DC 仿真结果 |

图21 AC仿真原理图 |

|

图22 AC仿真环境配置 |

图23 AC仿真结果 |

|

图24 Browser工具调出幅频与相频曲线 |

图25 配置DC仿真环境,查看当前各点的电压和电流(结果在第四部分) |

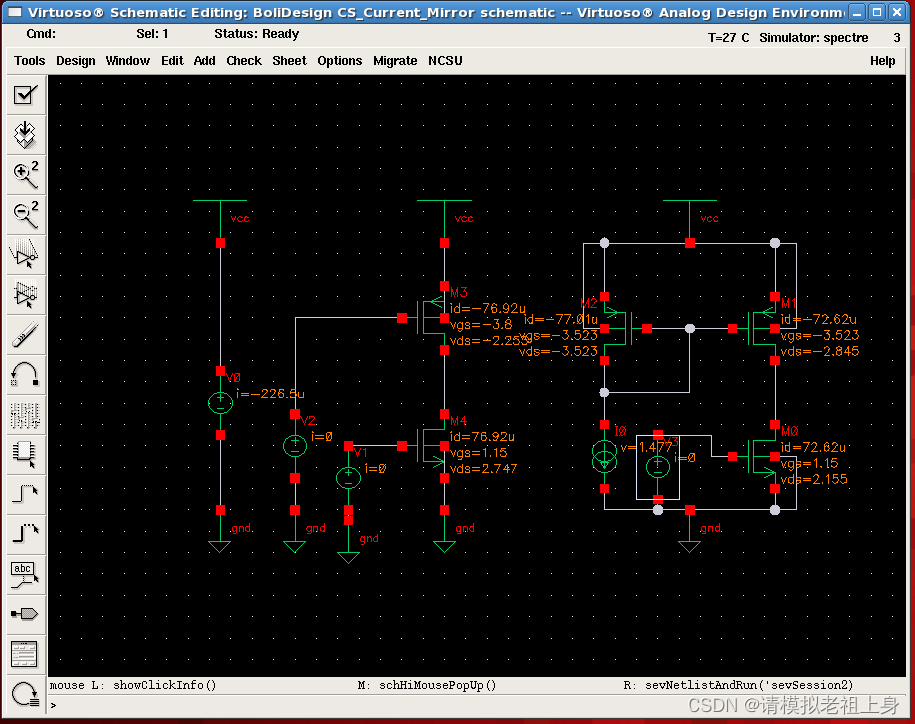

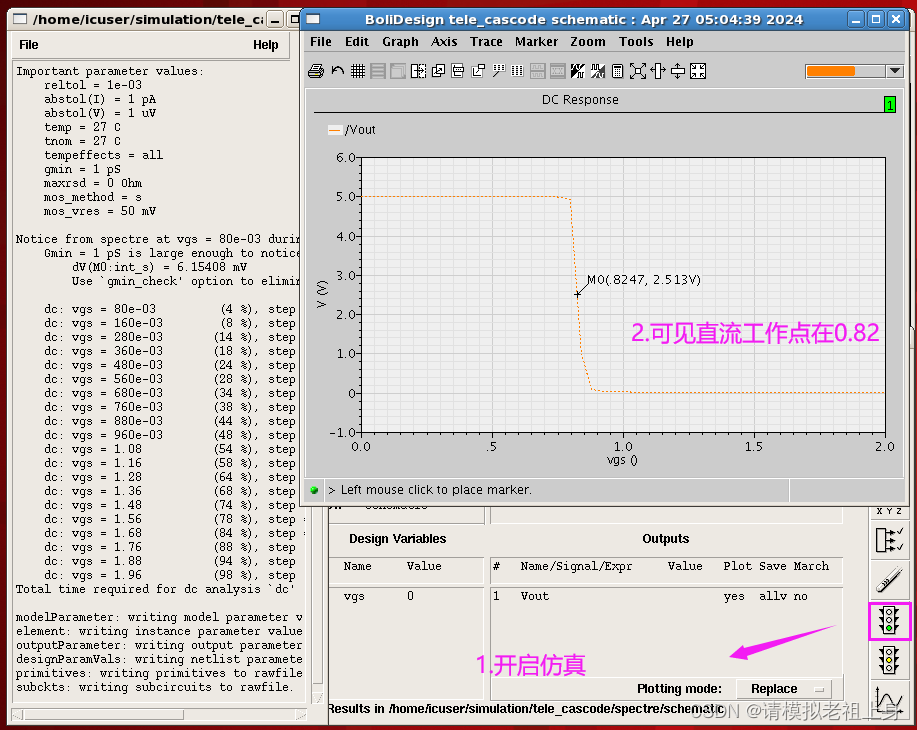

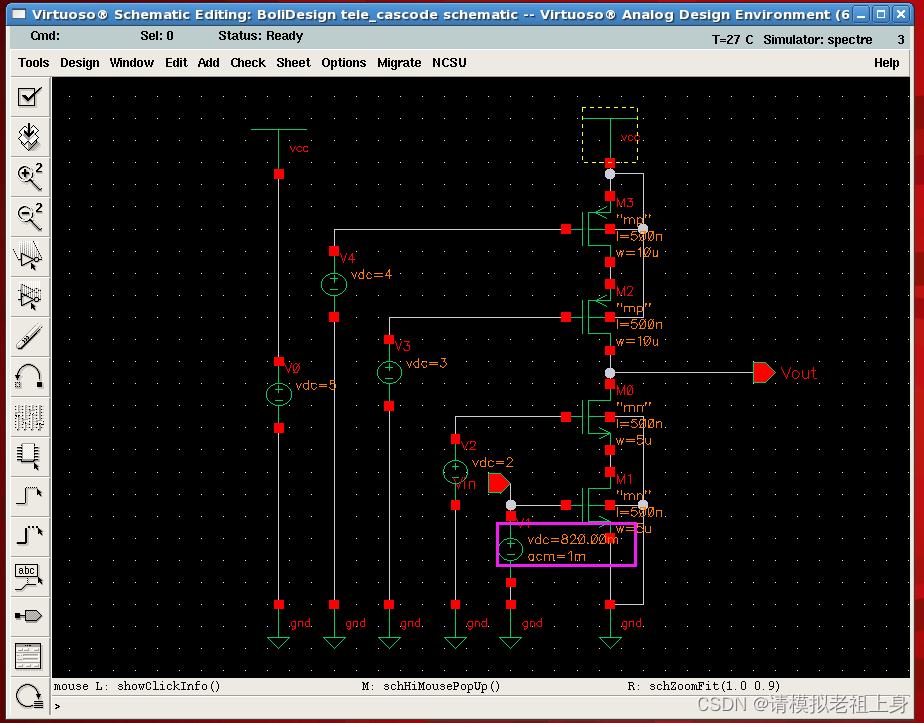

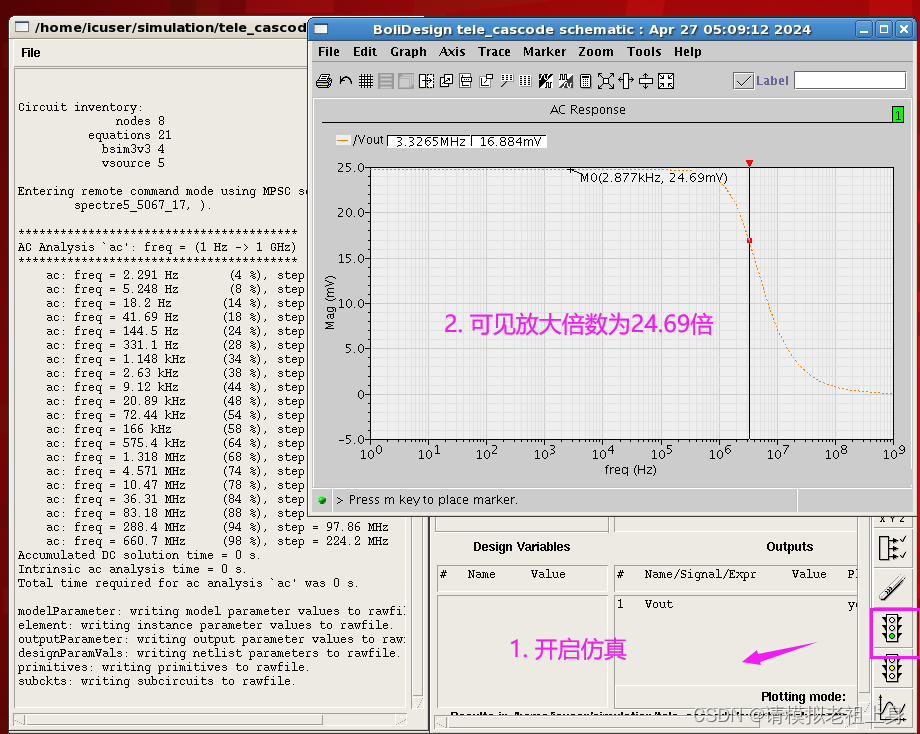

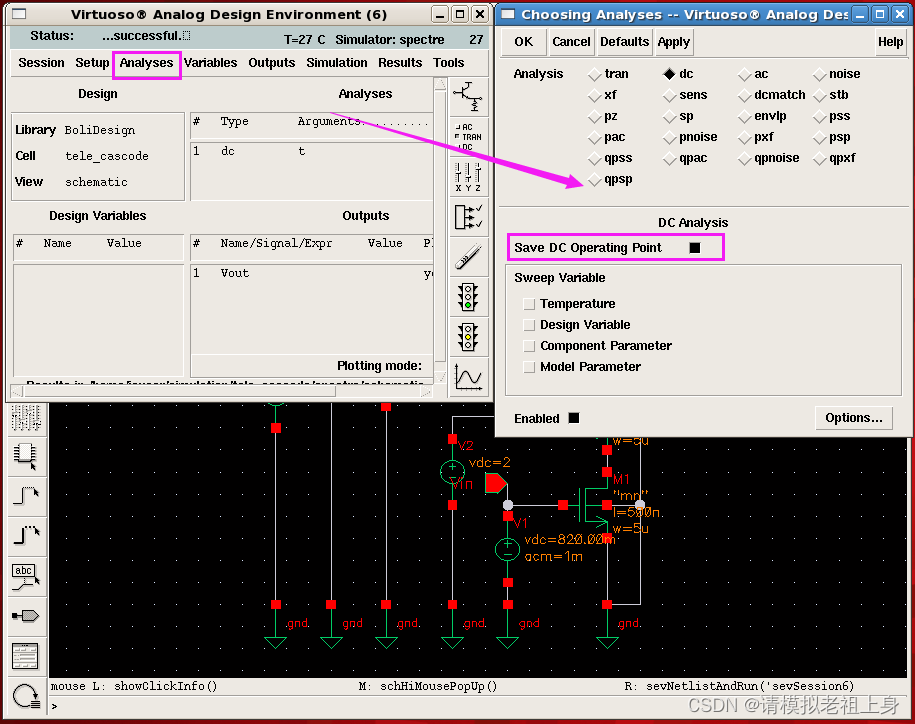

4.【实验三】Cascode放大器

|

图26 DC仿真原理图 |

图27 dc仿真环境配置,寻找最佳直流工作点 |

|

图28 DC 仿真结果 |

图29 AC仿真原理图 |

|

图30 AC仿真环境配置 |

图31 AC仿真结果 |

|

图32 Browser工具调出幅频与相频曲线 |

图33 配置DC仿真环境,查看当前各点的电压和电流(结果在第四部分) |

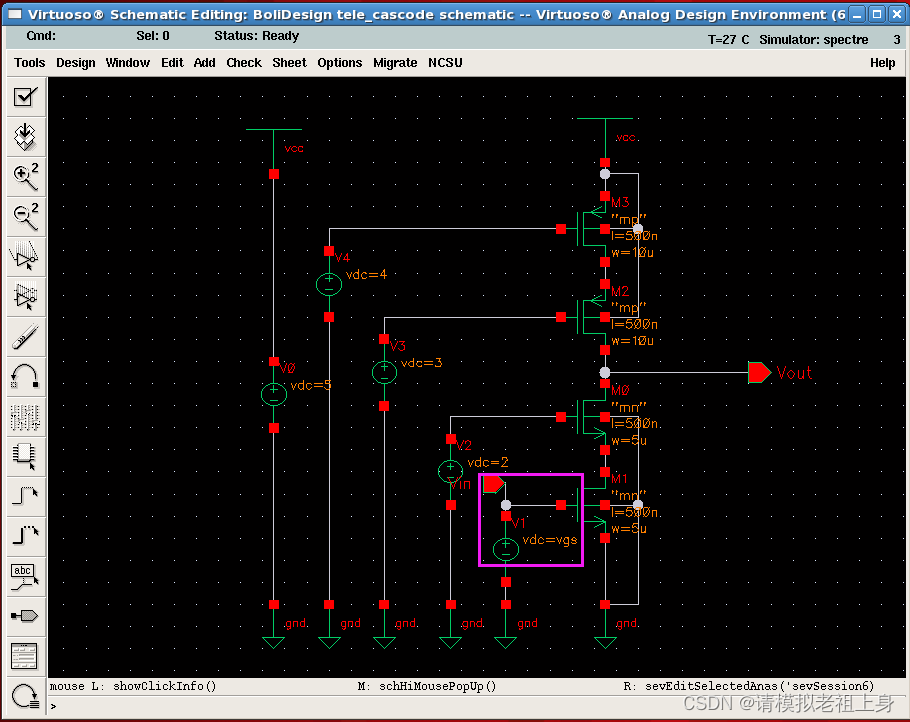

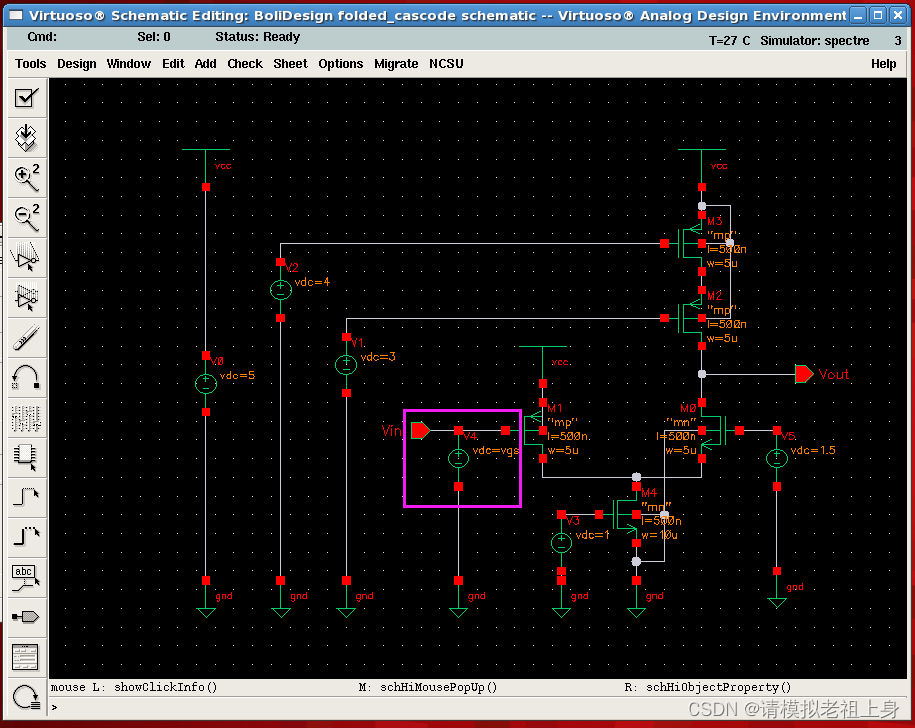

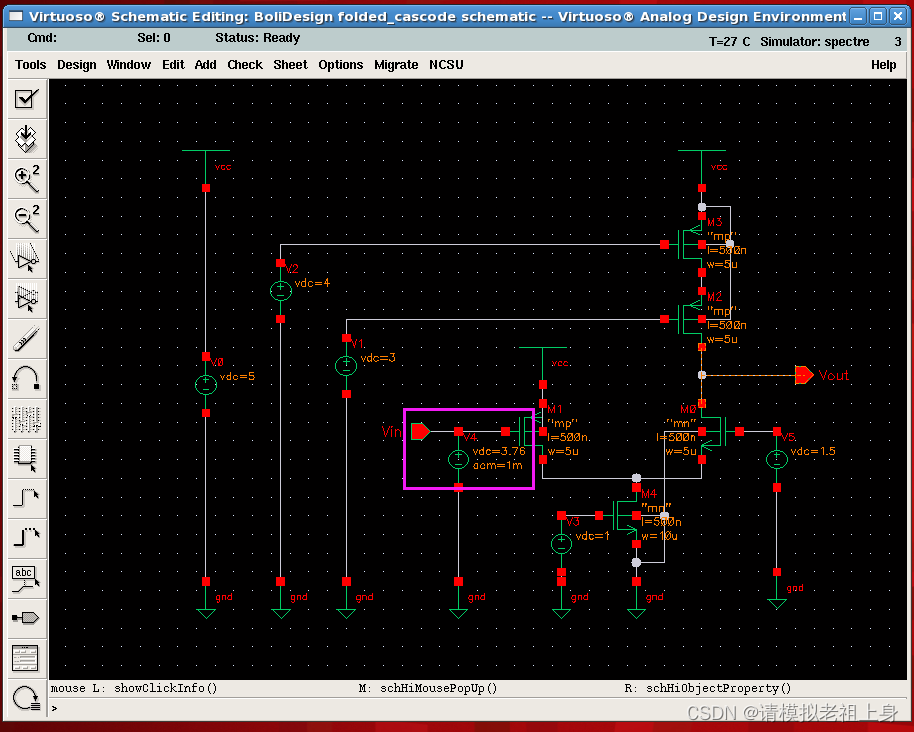

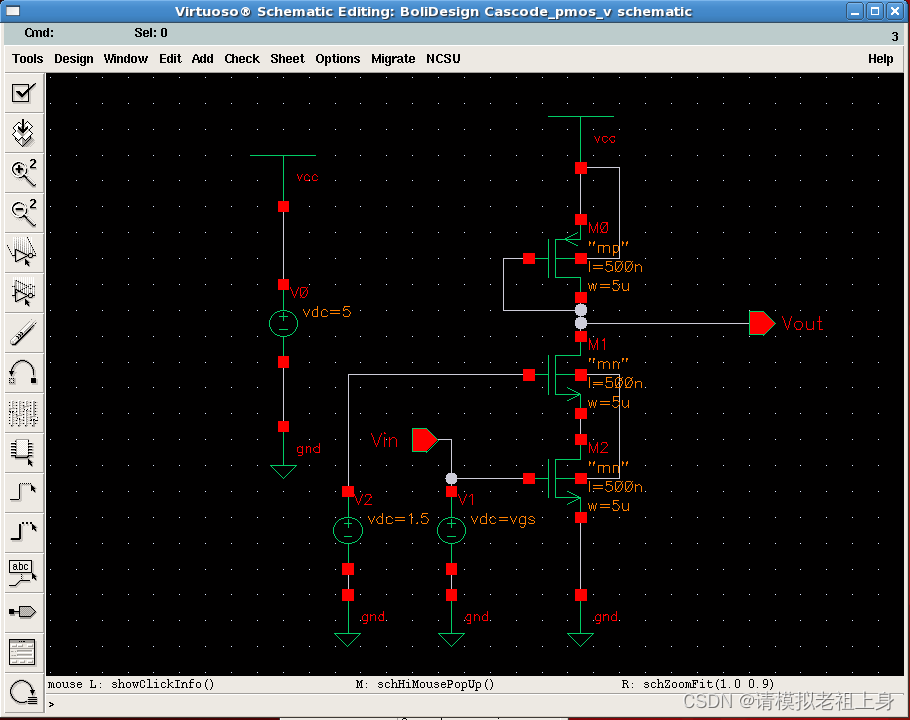

5.【实验四】升级版 Folded Cascode放大器

|

图34 DC仿真原理图 |

图35 dc仿真环境配置,寻找最佳直流工作点 |

|

图36 DC 仿真结果 |

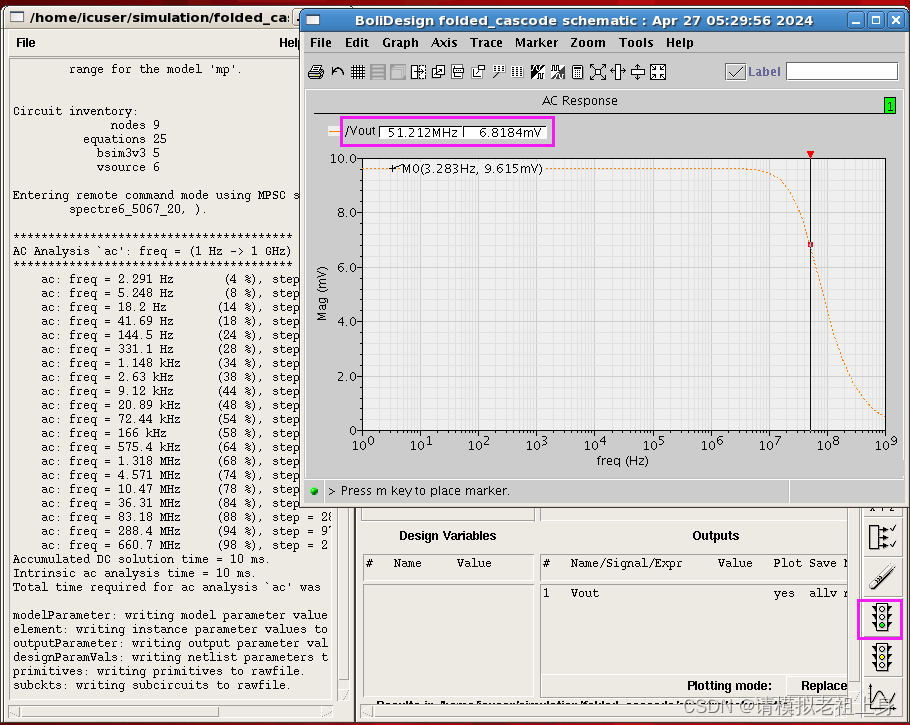

图37 AC仿真原理图 |

|

图38 AC仿真环境配置 |

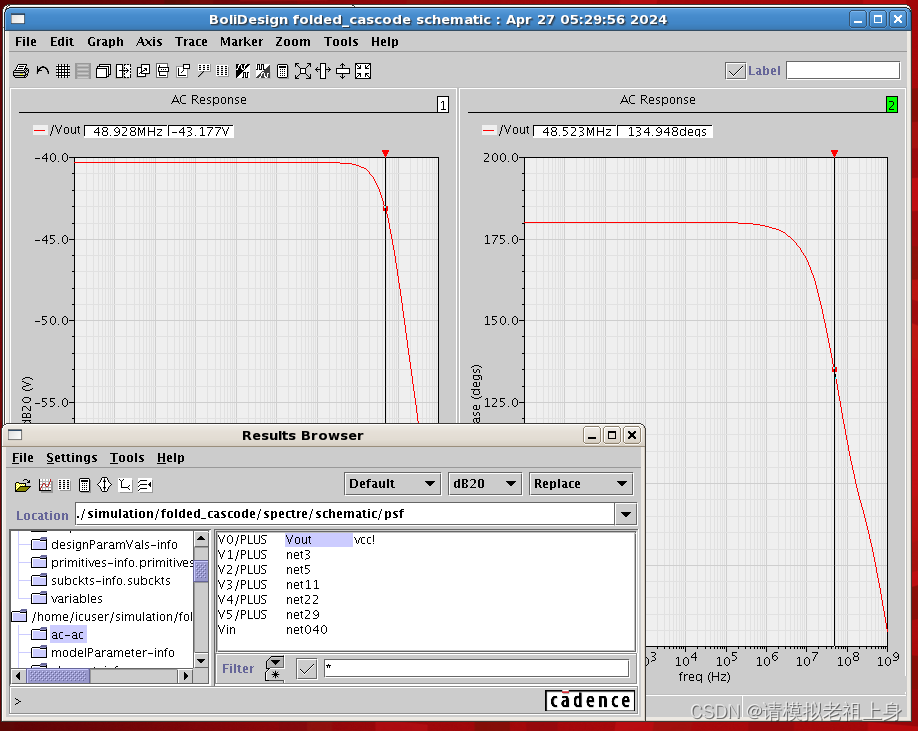

图39 AC仿真结果 |

|

图40 Browser工具调出幅频与相频曲线 |

图41 配置DC仿真环境,查看当前各点的电压和电流(结果在第四部分) |

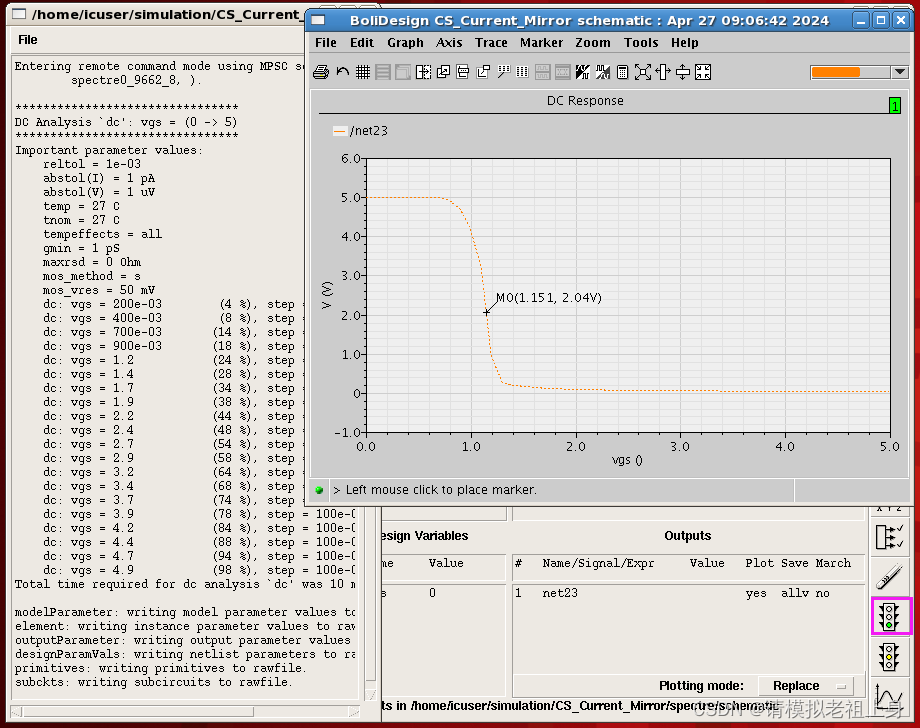

6.【实验五】电流源偏置的共源极

|

图42 电压偏置,DC仿真原理图 |

图43 电压偏置DC仿真配置 |

|

图44 电压偏置,DC 仿真结果 |

图45 在此偏置下,AC仿真结果 |

|

图46 查看此条件下的Id |

图47 修改后的原理图 |

|

图48修改后的原理图,DC仿真结果对比 |

图49查看电流偏置的AC仿真结果 |

五、仿真结果及分析

1. 【实验一】res做负载的Cascode放大器

(0)schematic

|

图50 电压偏置的res负载的Cascode |

图51 电压偏置的res负载的Cascode,DC参数展示 |

a.不同Vb偏置下的 DC静态工作点

图52 DC仿真结果

选择DC_point = 1V。当Vin由0逐渐升高时,下管逐渐“截止-饱和”,当Vin>1.2V时,使得上管进入线性区,而后逐渐截止,电流通路被切断,输出变为0。所以要使两管处于饱和,选择DC_point=1V,最为合适。

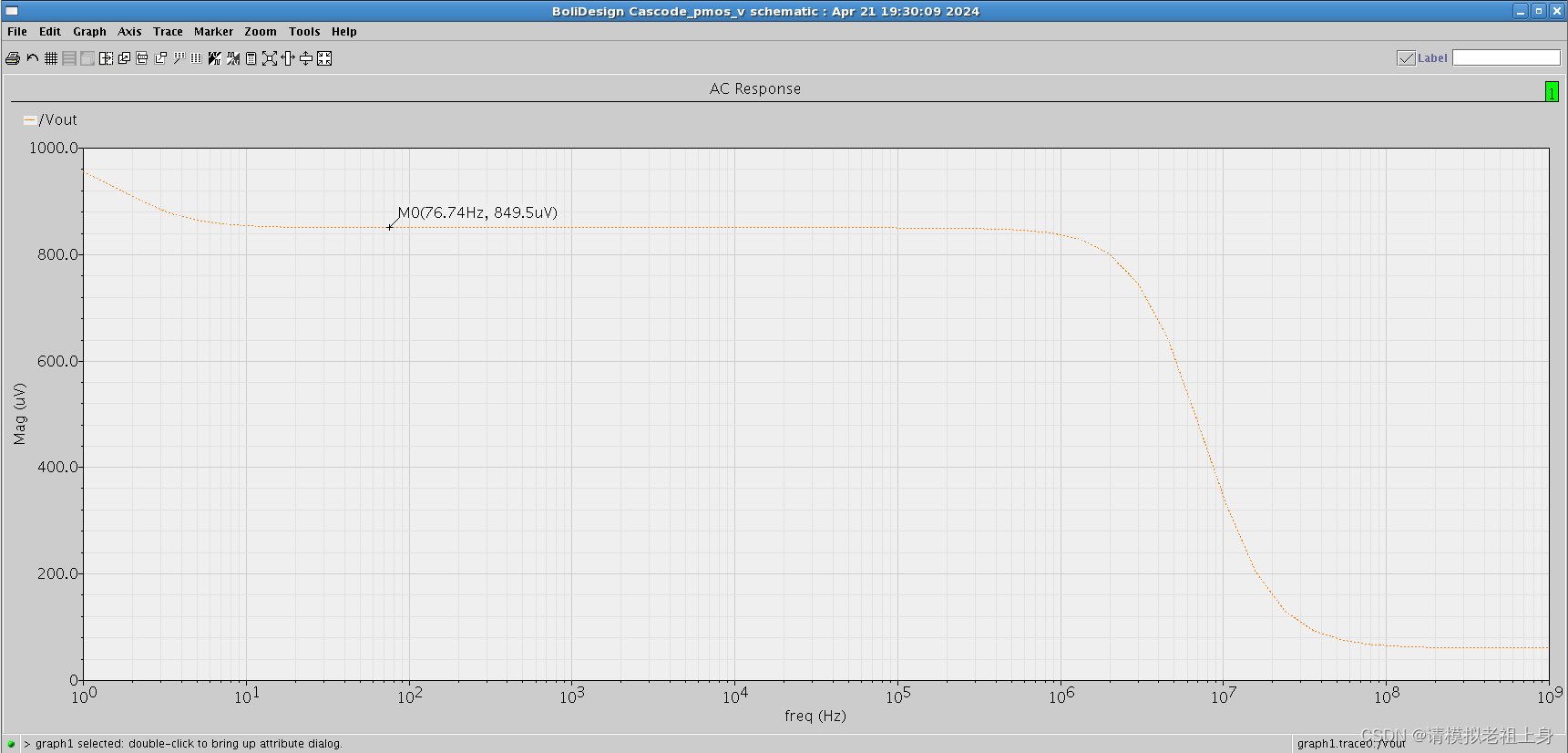

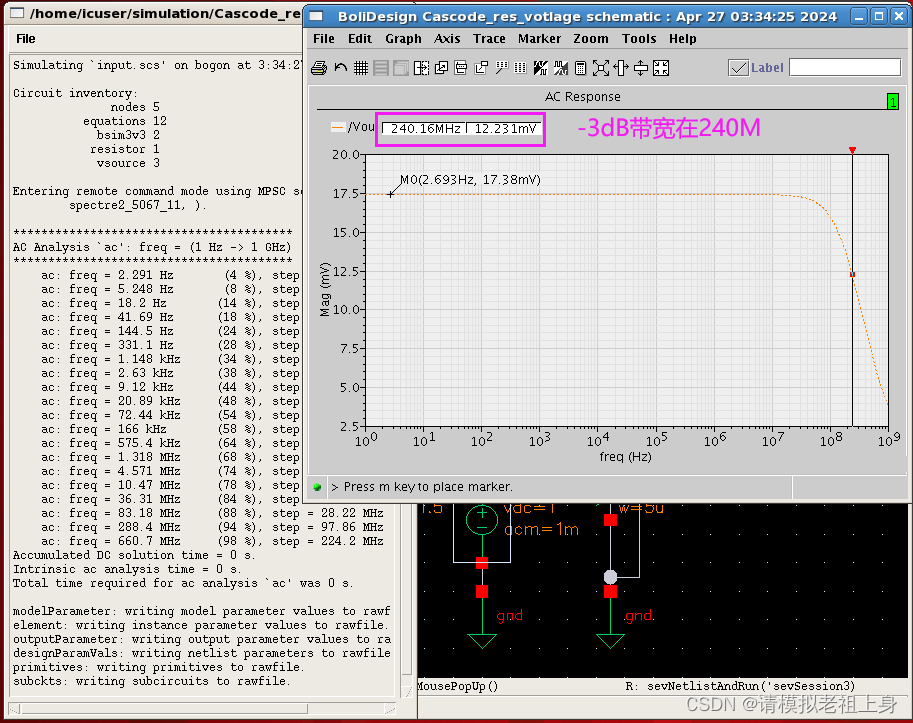

b. AC频域特性

图53 AC仿真结果(幅频特性曲线)

可见,放大倍数为20.62倍。

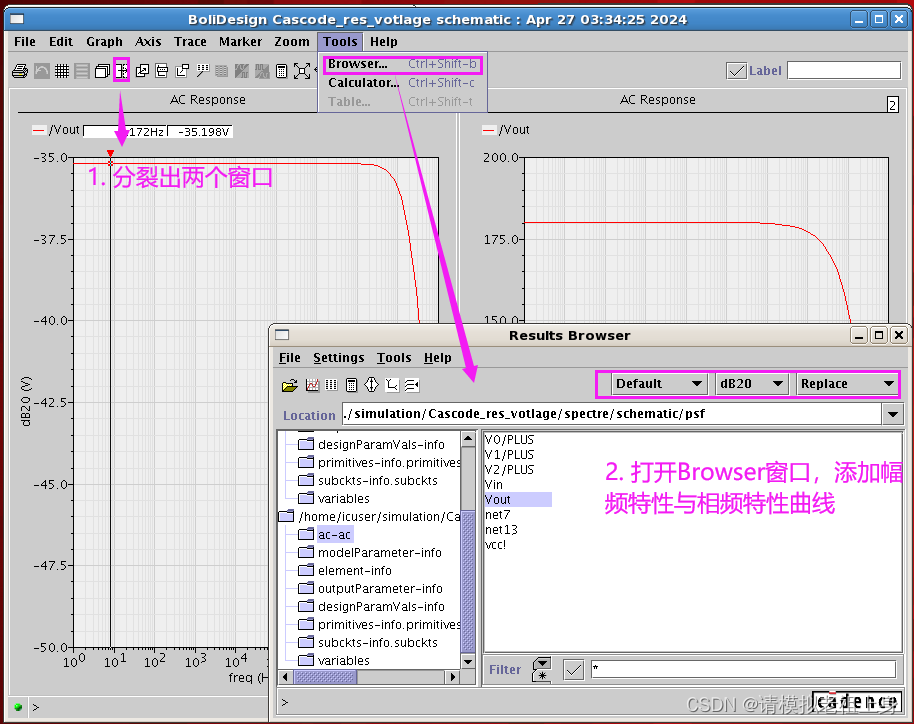

图54 AC仿真结果(幅频特性曲线+相频特性曲线)

幅频特性曲线是用来查看放大倍数与频率之间的关系。相频特性曲线是用来查看相位随着频率的衰减,用于研究系统的稳定性。位于拉普拉斯域左侧的极点会使增益开始以-20dB衰减,相位减少90,左侧的零点则会使增益以-20dB增加,相位超前90。

由图可知,这是一个单极点系统,零点在无穷大处,主极点为189M。放大倍数为20.62倍。由于电阻受“pvt”工艺参数波动很大,加上大电阻难以做集成,此电路优势不是很大。

2. 【实验二】pmos二极管连接做负载的Cascode放大器(电压偏置/电流偏置)

(0)schematic

|

图55 电压偏置的pmos二极管负载的Cascode(电压偏置) |

图56 各点工作电压与器件电气参数 |

a. DC静态工作点

图57 DC仿真结果(PMOS二极管连接的Cascode)

选择DC_point=0.6V。当Vin由0逐渐升高时,下管逐渐“截止-饱和”,当Vin>1.2V时,使得上管进入线性区,输出变为0.所以要使两管处于饱和,选择DC_point=0.6V,最为合适。

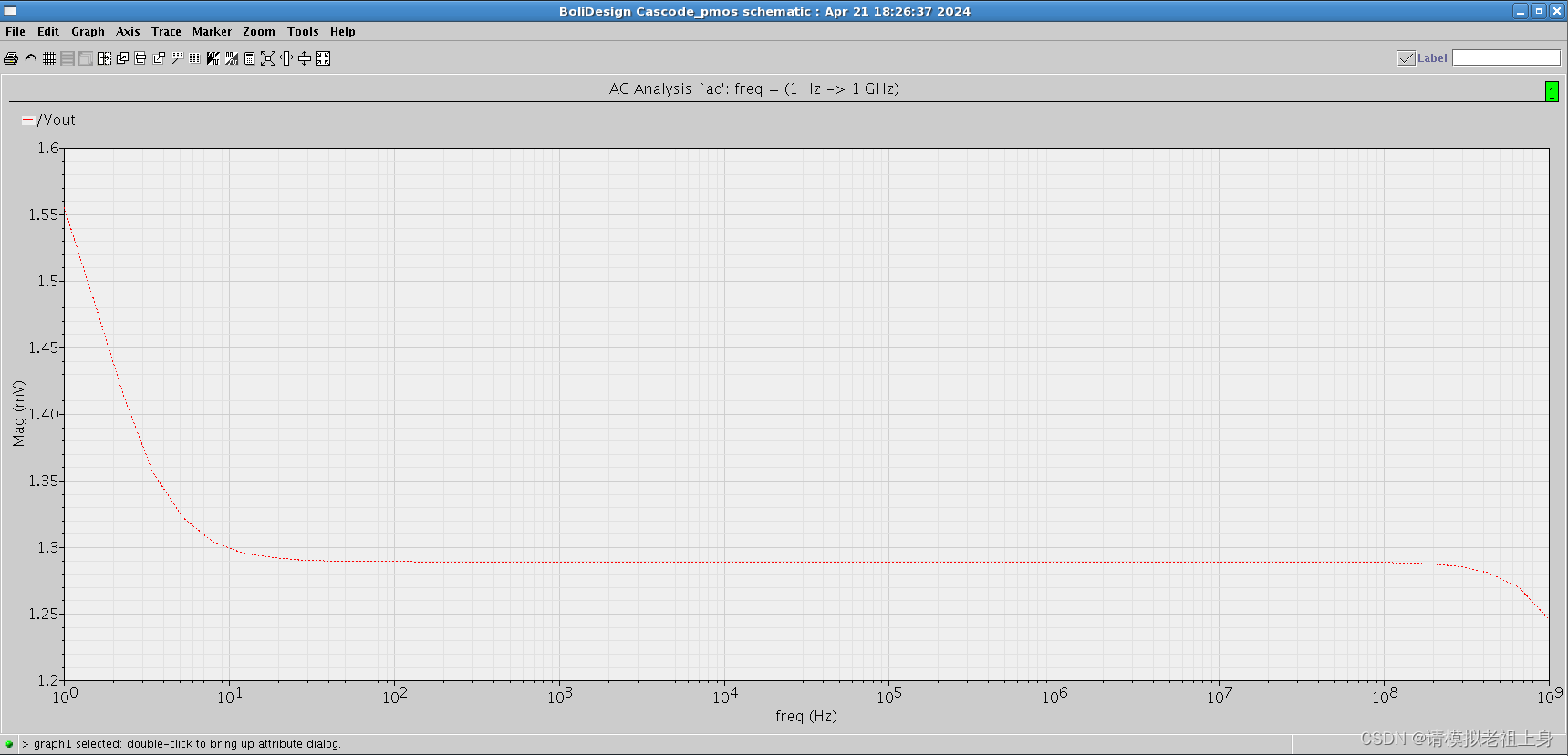

b. AC频域特性

图58 AC仿真结果(PMOS二极管连接的Cascode)

可见,放大倍数为0.8倍,受限于此电路的低输出阻抗,导致Gm = gm*Rout<1。

图59 AC仿真结果(幅频特性曲线+相频特性曲线)

幅频特性曲线是用来查看放大倍数与频率之间的关系。相频特性曲线是用来查看相位随着频率的衰减,用于研究系统的稳定性。位于拉普拉斯域左侧的极点会使增益开始以-20dB衰减,相位减少90,左侧的零点则会使增益以-20dB增加,相位超前90。

由图可知,这是一个单极点系统,零点在无穷大处,主极点为7M。放大倍数为0.8倍。当cascode和nmos都处于饱和区时,增益最大。增益A=gmn/gmp,所以pmos管尺寸越小,增益越大。尺寸小,寄生电容也小,此结构自身输出阻抗小,所以比较高频。但是输出阻抗小会大大影响增益,需要增大nmos的跨导来弥补。

3. 【实验三】Cascode放大器

(0)schematic

|

图60 Cascode放大器(电压偏置) |

图61 Cascode放大器(电流偏置) |

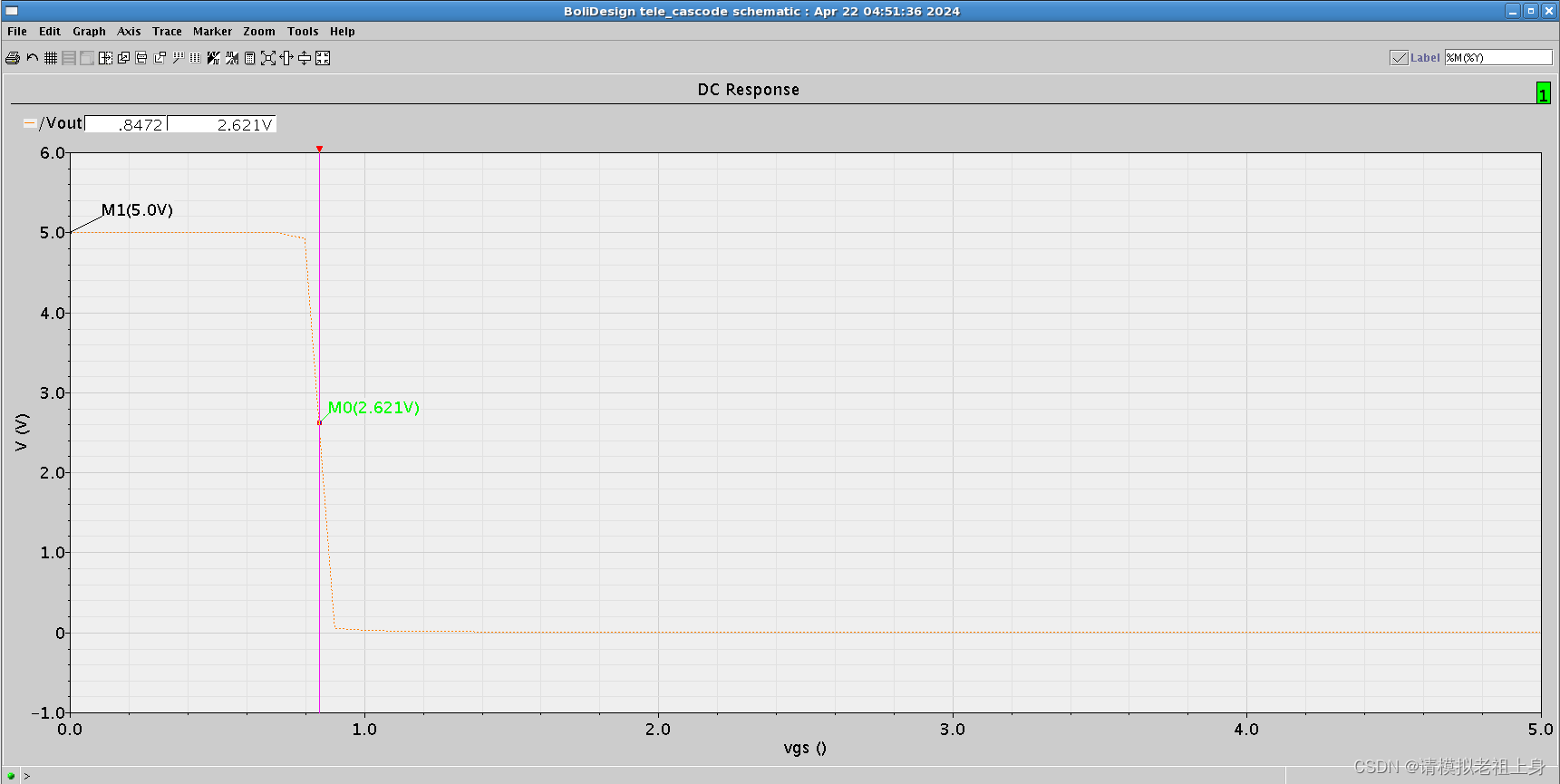

a. DC静态工作点

图62 DC仿真结果(Cascode做负载的放大器)

选择DC_point = 0.84V。

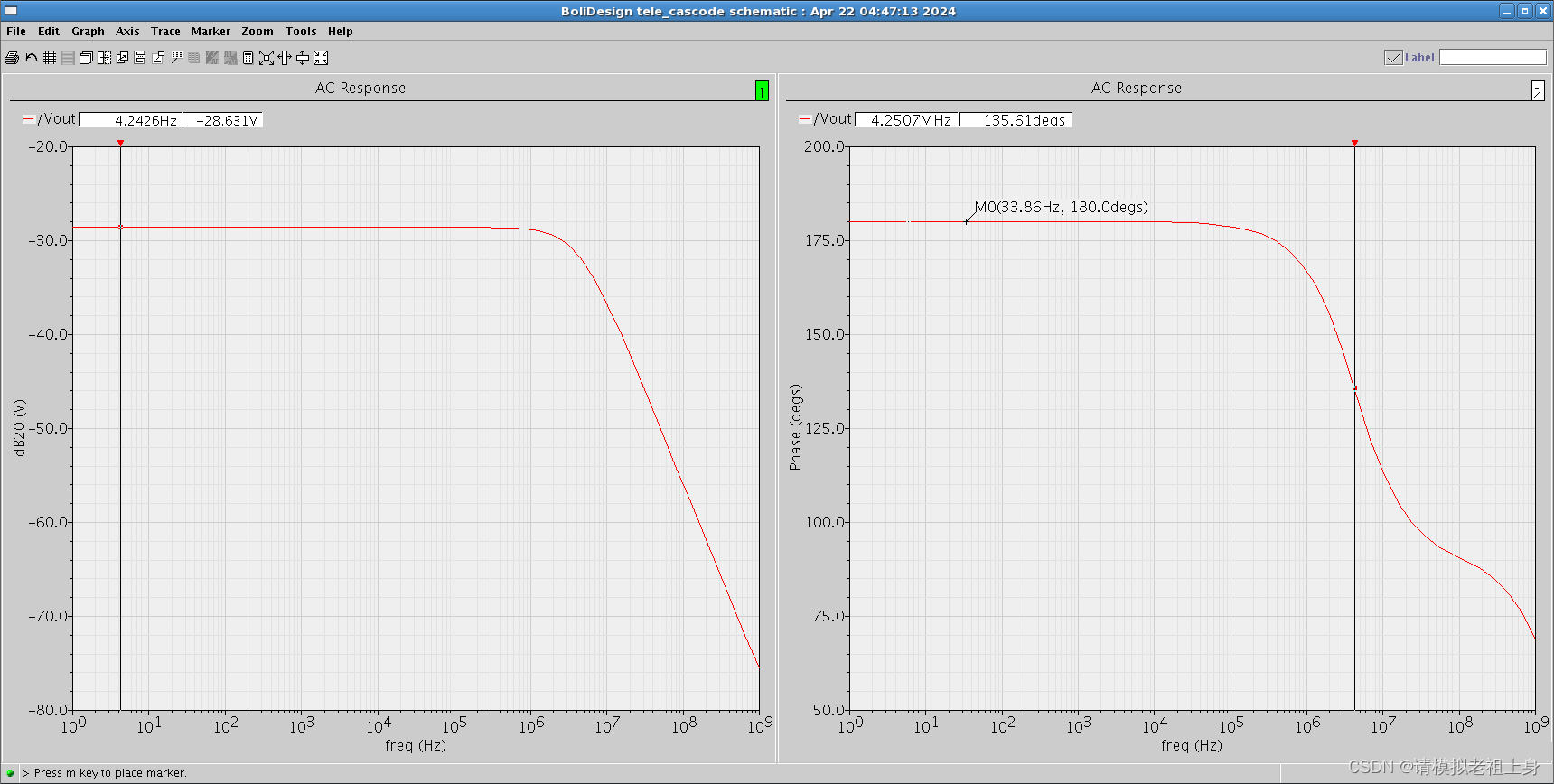

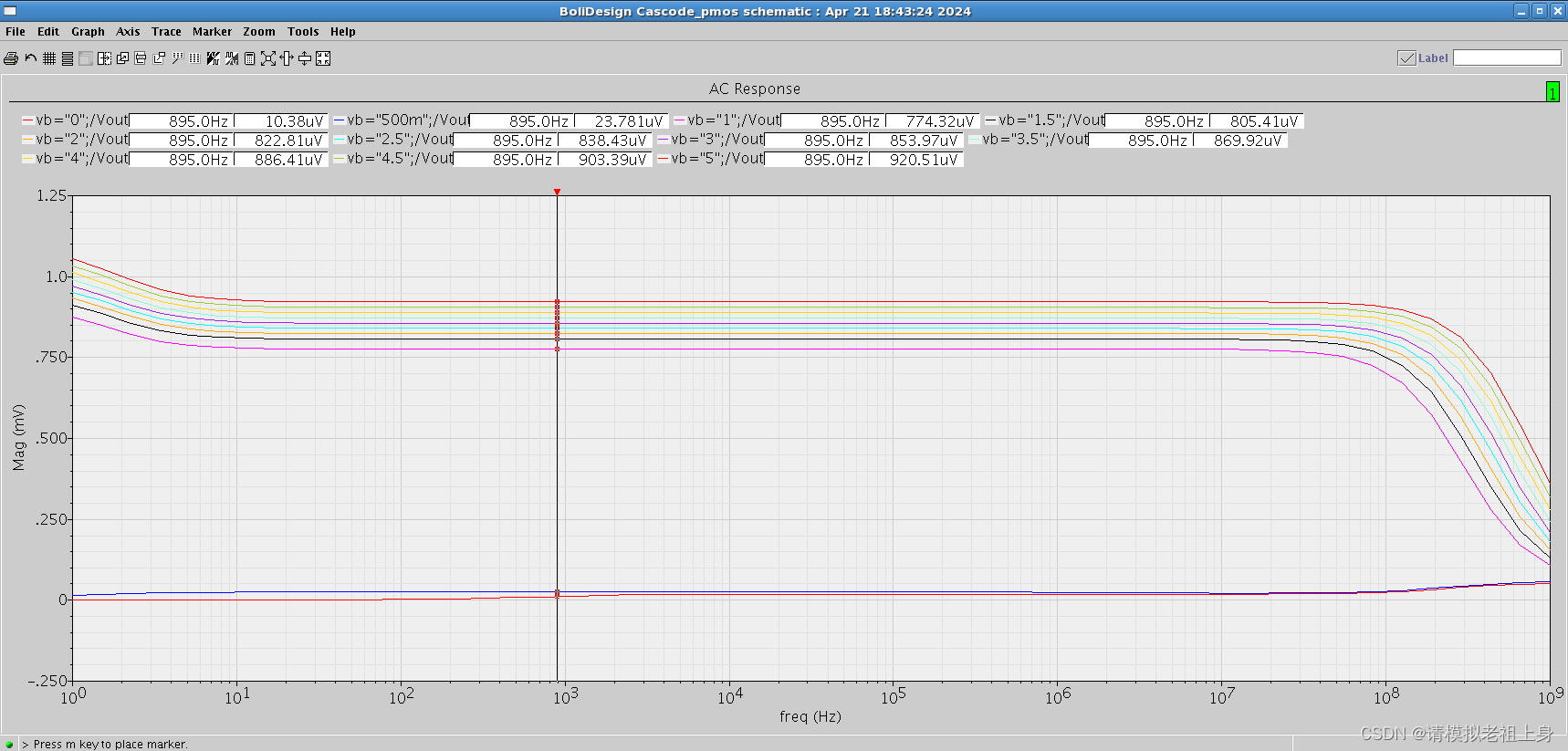

b. AC频域特性

图63 AC仿真结果(Cascode做负载的放大器)

可见,放大倍数为37.02倍,得益于此电路的高输出阻抗,导致Gm = gmn*Rout。Rout=gmn*ron*ron||gmp*rop*rop。所以增益成倍增加。

图64 AC仿真结果(幅频特性曲线+相频特性曲线)

幅频特性曲线是用来查看放大倍数与频率之间的关系。相频特性曲线是用来查看相位随着频率的衰减,用于研究系统的稳定性。位于拉普拉斯域左侧的极点会使增益开始以-20dB衰减,相位减少90,左侧的零点则会使增益以-20dB增加,相位超前90。

由图可知,这是一个单极点系统,零点在无穷大处,主极点为4.25M。放大倍数为37.02倍。当cascode和nmos都处于饱和区时,增益最大。增益Gm = gmn*Rout。Rout=gmn*ron*ron||gmp*rop*rop。此种结构为套筒式的共源共栅,当电源轨足够大时,可以在增加一级套筒使得输出阻抗成倍增加,大大提升放大倍数,美中不足,此电路输出摆幅极小,可通过折叠式的Cascode得以改善,或者两级运放在输出级级联一级“NMOS+PMOS”。

4. 【实验四】Folded Cascode放大器

(0)schematic

|

图65 Cascode放大器(电压偏置) |

图66 电压偏置工作状态展示 |

a. DC静态工作点

图67 DC仿真结果(Folded Cascode放大器)

选择DC_point = 3.75V。

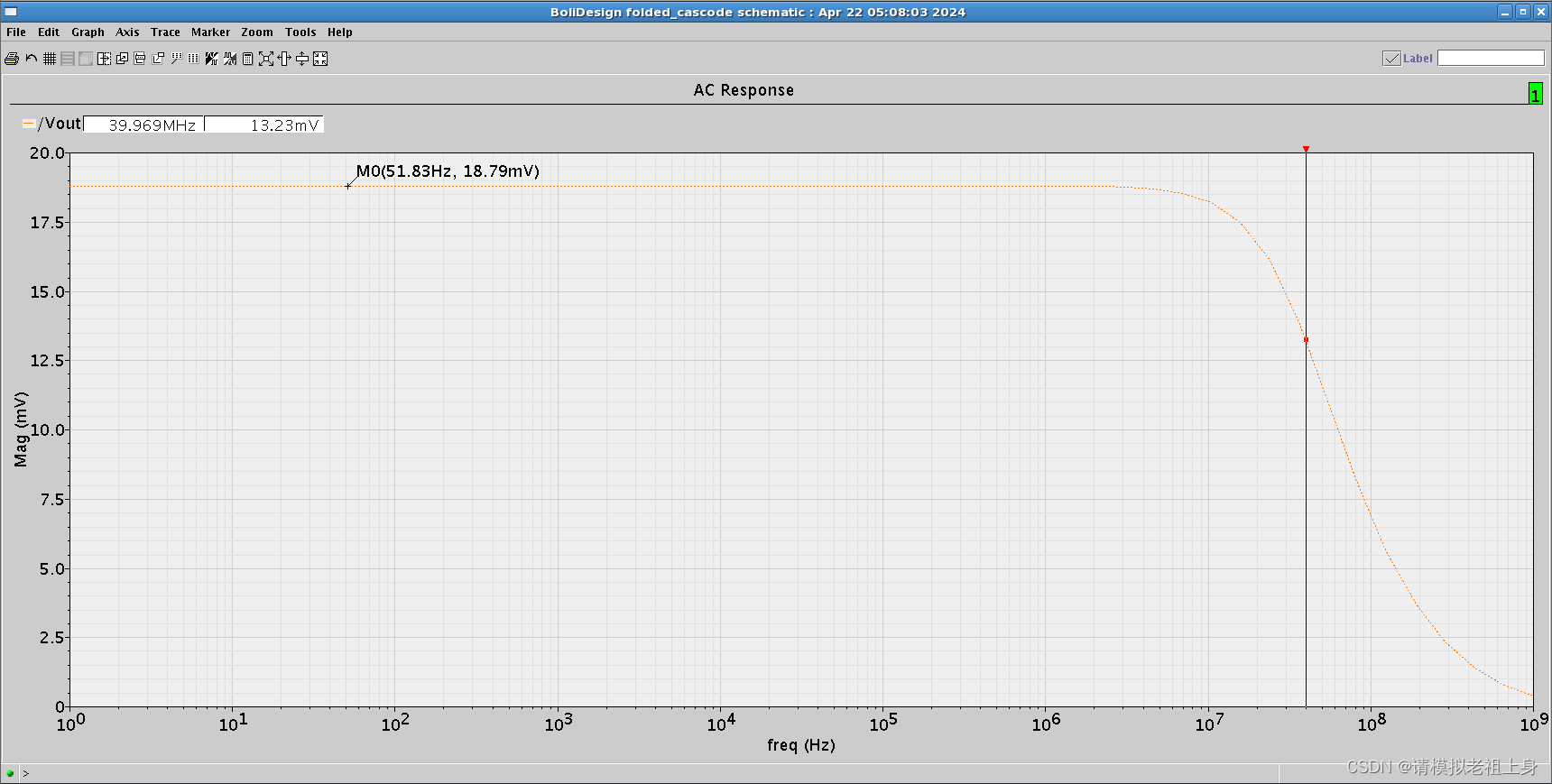

b. AC频域特性

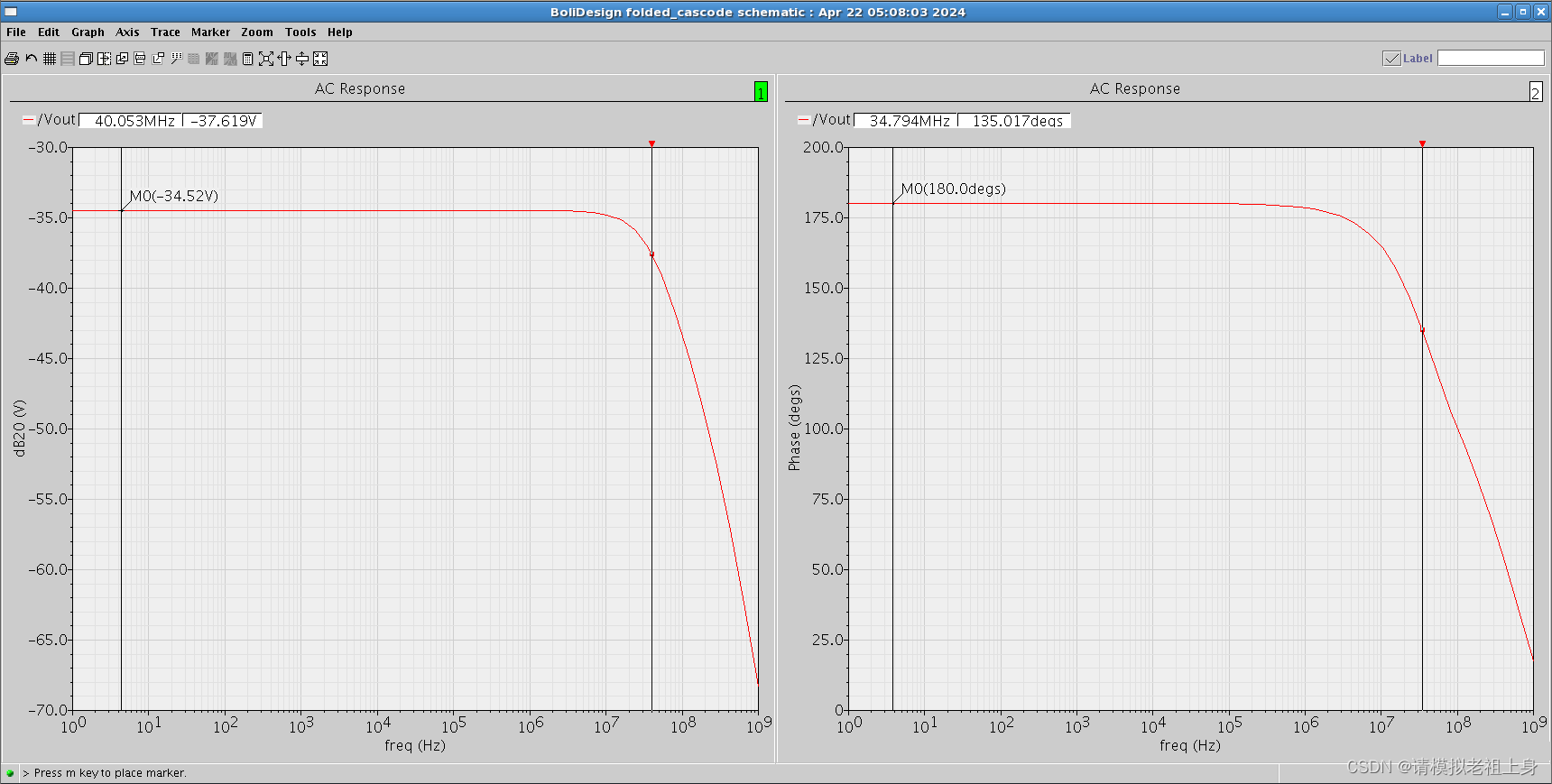

图68 AC仿真结果(Folded Cascode放大器)

可见,放大倍数为18.79倍,得益于此电路的高输出阻抗,Gm = gmn*Rout。所以增益成倍增加。如果还要更大的阻抗,可以增加宽长比。

图69 AC仿真结果(幅频特性曲线+相频特性曲线)

幅频特性曲线是用来查看放大倍数与频率之间的关系。相频特性曲线是用来查看相位随着频率的衰减,用于研究系统的稳定性。位于拉普拉斯域左侧的极点会使增益开始以-20dB衰减,相位减少90,左侧的零点则会使增益以-20dB增加,相位超前90。

由图可知,这是一个单极点系统,零点在无穷大处,主极点为40M。放大倍数为18.79倍。当cascode和nmos都处于饱和区时,增益最大。

5. 【实验五】Folded Cascode放大器(电流源偏置的共源极)

(0)schematic

|

图70 Folded Cascode放大器 |

图71 电压偏置与电流偏置的对比 |

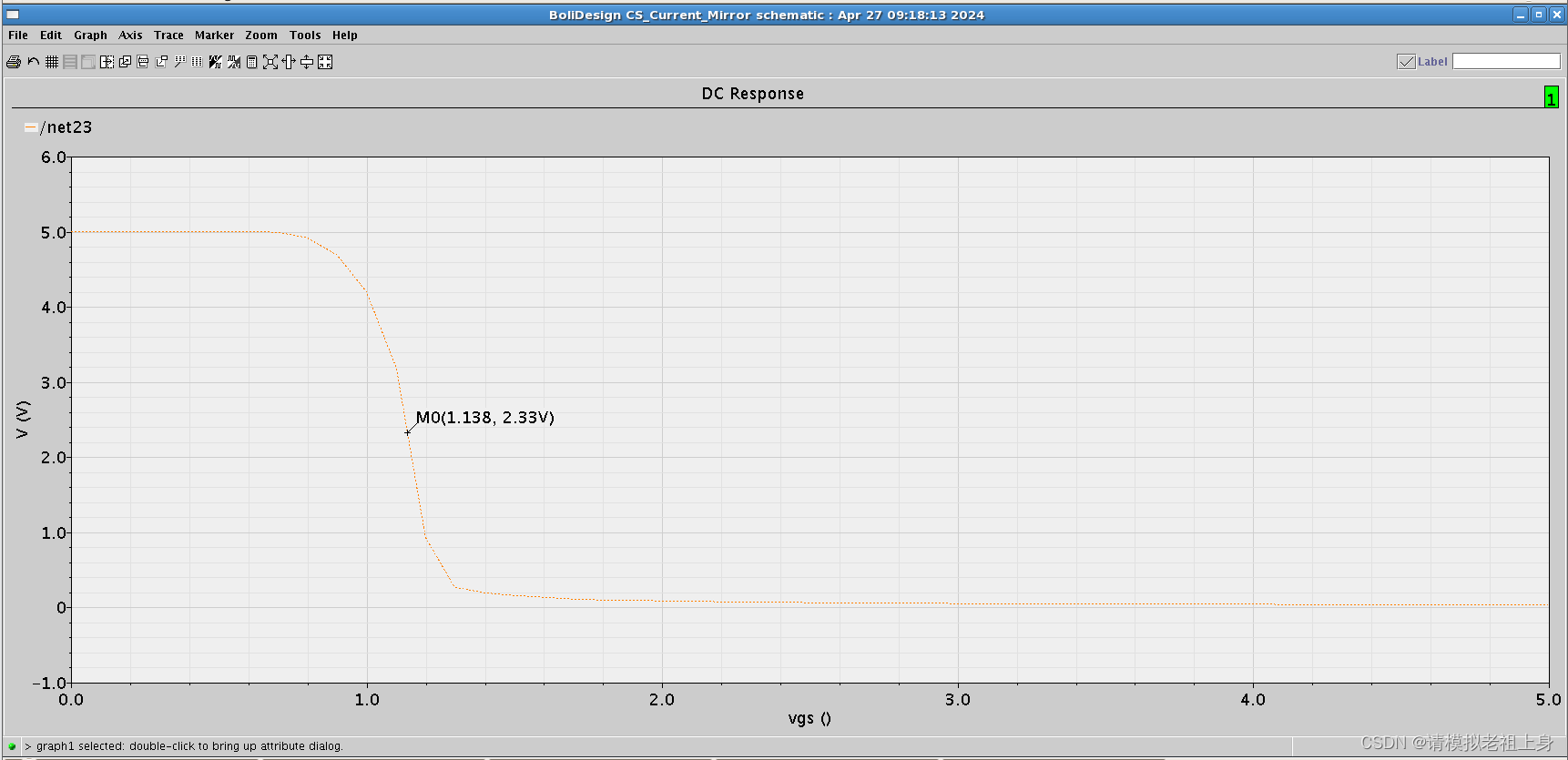

a. DC静态工作点

图72 DC仿真结果(Folded Cascode放大器)

选择DC_point = 1.15V。

b. AC频域特性

图73 AC仿真结果(Folded Cascode放大器)

可见,放大倍数为24.8倍,得益于此电路的高输出阻抗,导致Gm = gmn*Rout。Rout=ron||rop。所以增益成倍增加。

图74 AC仿真结果(幅频特性曲线+相频特性曲线)

幅频特性曲线是用来查看放大倍数与频率之间的关系。相频特性曲线是用来查看相位随着频率的衰减,用于研究系统的稳定性。位于拉普拉斯域左侧的极点会使增益开始以-20dB衰减,相位减少90,左侧的零点则会使增益以-20dB增加,相位超前90。

由图可知,这是一个单极点系统,零点在无穷大处,主极点为430M。放大倍数为24.8倍。Gm = gmn*Rout。Rout=ron||rop。此电路使用电流偏置使得电路稳定性相较于电压特性更为优良。

六、心得体会

本次实验是第三次实验课,王老师先是向我们讲述了电路的原理,接着演示实操步骤,并在重要节点做出引申。我在本次实验中遇到了多种问题,主要是关于如何给电路设计偏置电路,下面从两个问题展开我的心得体会:

【问题一】电路:“pmos二极管连接做负载的Cascode放大器”

当偏置电压Vb设置为4-5V时,输出曲线相差不大,所以偏置电压选择4V,DC_Point选择在1.4V处。

(对偏置工作区进行分析)

直流工作点在0.6,对Vb扫频

直流工作点在0.8,对Vb扫频

直流工作点在1.4

在和王老师深入交流后,我得到了一个结论,对于NMOS设计电压偏置电路时,需要根据理论分析,选取尽可能小的偏置值,如果偏置值较大,很有可能使得上方的MOS进入线性区,所以设计时,需要再输出摆幅和偏置电流(增益)之间作取舍,一般保留输出摆幅,电路增益可以通过两级运放或者其他结构得以改善。对于PMOS设计电压偏置电路时,正好相反,需要尽可能选取大的偏置值,偏置值较小会使下方MOS进入线性区。这个结论非常之适用,设计偏置电路时根本不需要扫描,这下一下便解决了我的困惑,感谢王老师的耐心解答。

【问题二】电路:“Folded Cascode放大器(电流源偏置的共源极)”

问题描述:当按照设计的电压偏置进行对应的电流偏置设计时,电流镜并未正常偏置,接下来我尝试增加MOS的尺寸,不改变宽长比,问题未得以解决。接着查看不正常的情况下的DC输出与AC输出,发现放大倍数比起之前略有增加,带宽几乎不变。但是电流镜不正常偏置,所以接下来还是得深入钻研,尝试解决。

非常感谢王老师的讲授,希望自己可以在模拟的世界走的更远。

图图15 AC仿真结果

图图15 AC仿真结果

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?