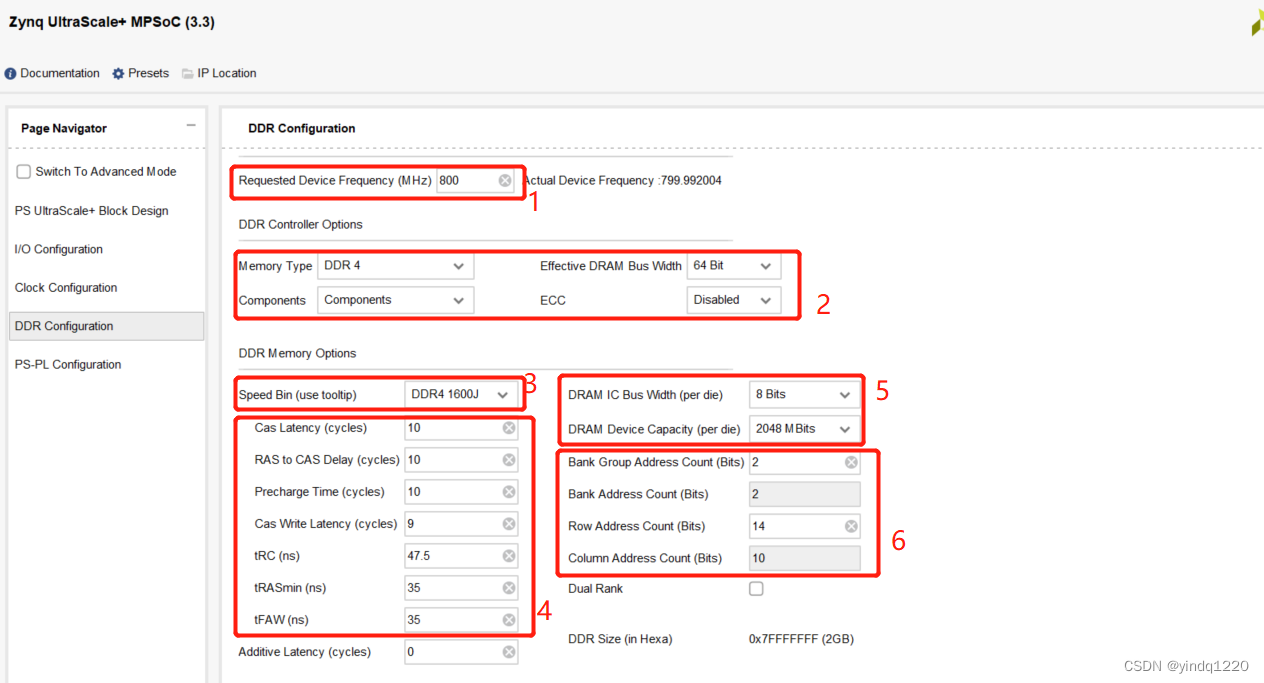

使用MPSOC系列FPGA,在vivado的BOLCK DESIGN设计中,需要按照硬件使用的DDR芯片,正确的配置DDR相关参数,以便ARM可以正常运行。此处进行简单的介绍记录。

1、Requested Device Frequency(MHz)

根据DDR选型,选择DDR的工作频率,此处为800Mhz。

2、DDR控制器选项

Memory Type: 内存类型可以使DDR3、DDR4等,依据DDR信号选择;

Component: 内存元件可以使颗粒、内存条等形式。可选项为颗粒、UDIMM内存模组、RDIMM内存模组。此处为components,内存颗粒。

Effective DRAM Bus Width:硬件上ARM与DDR之间的数据总线宽度。

3、Speed Bin

DDR 速度等级,依据DDR手册选择。

4、DDR相关参数

DDR是根据行和列寻址的:

a、执行读写操作时,最初先执行预充电Active to precharge Delay

b、预充电后,内存才真正开始初始化RAS(Row Address Strobe),即选通行地址,选通需要的时间表示为tRAS;

c、再接着需要执行首先是列地址选通,行地址选通到列地址选通之间的时间是tRCD(RAS to CAS Delay);

d、执行列地址选通CAS(Column Address Strobe)访问所需数据的十六进制地址。其中,从CAS开始到CAS结束,就是CAS延迟(即tCL)。所以CAS是找到数据的最后一个步骤,tCL也是内存参数中最重要的。

实际工作中,DDR工作流程如下:

a、同时发出BANK地址、ROW行地址,此时进行行激活

b、同时发出列地址和具体读写命令,从行有效到发出读写命令之间有一段延迟,称为RAS to CAS delay,tRCD。这段时间会进行在存储和预充电

c、列地址被选中后,会触发数据传输。

| 参数名称 | 含义 | 备注 |

| CAS Latency(cycles) | tCL:内存读写操作前列地址控制器的潜伏时间,单位一般为时钟周期。 CAS为列地址选通脉冲,控制着DDR从收到命令到执行命令的间隔时间。即读一个数据需要的时间为CAS latency。 | |

| RAS to CAS delay(cycles) | 从CAS行有效开始,到发出读写命令和列有效开始,之间有一段延迟,称为RAS to CAS delay,tRCD | |

| Precharge time(cycles) | 由于DDR的物理特性,打开新的一行时,需要先关闭原有工作行,这个过程伴随着充电或者放电,因此成为预充电操作。 tRP:Precharge command period,预充电有效周期,在发出预充电命令之后,要经过一段时间才能允许发送RAS行有效命令打开新的工作行; | |

| CAS Write latency(cycles) | 和读数据类似,这个参数描述的是CAS发出之后经过一定的时间数据可以写入到DDR。 即CAS开始到数据写入的时间tCWL | |

| tRC(ns) | ROW Cycle Time,SDRAM 行周期时间,即同一BANK两次行激活命令的间隔(包括行预充电在内的整个过程的最小间隔)。 tRC=tRAS+tRP。 | |

| tRASmin(ns) | RAS active time 行有效到预充电的最短时间。 | |

| tFAW(ns) | Four active window 定义了一个RANk中允许同时发送大于4个BANK行激活命令的间隔时间。若DDR含有超过4个BANK,其在tFAW不允许发送超过4个行激活命令。 |

5、DRAM IC BUS width 和 DRAM Device Capacity( per die)

DRAM IC BUS width: 单个DDR的数据总线宽度

DRAM Device Capacity: 单个DDR的内存大小

6、BANK地址信息

BANK Group Address Count: DDR 地址组的引脚个数

BANK Address Count : BANK地址的引脚个数

Row Address Count : 行地址引脚个数

Column Address Count: 列地址引脚个数

1803

1803

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?