参考资料

使用方法

文件构成

trigonometric_function/dds/dds.v:主模块文件trigonometric_function/cos_function/Makefile:用于测试的make脚本文件trigonometric_function/cos_function/testbench.sv:测试激励文件trigonometric_function/cos_function/python/gen_cos_data.py:用于生成余弦函数数据的python脚本

需要注意的是,DDS发生器依赖于COS函数发生器,使用了其ROM资源优化版本。

主模块信号及其参数配置

// trigonometric_function/dds/dds.v

module dds #(

parameter DEPTH_BITWIDTH = 8,

parameter DATA_BITWIDTH = 8

) (

input clk,

input rstn,

input [DEPTH_BITWIDTH-1:0] pword,

input [DEPTH_BITWIDTH-1:0] fword,

output [DATA_BITWIDTH-1:0] cos,

output [DATA_BITWIDTH-1:0] sin

);

以下是参数的相关解释:

| 参数 | 备注 |

|---|---|

DEPTH_BITWIDTH | DDS发生器地址深度 |

DATA_BITWIDTH | 输出的数据位宽 |

这两个参数实际上与COS函数发生器的参数一致,用于配置地址宽度与数据深度。

以下是信号的定义:

| 方向 | 位宽 | 信号 | 备注 |

|---|---|---|---|

| 输入 | 1 | clk | 系统时钟信号 |

| 输入 | 1 | rstn | 同步复位信号,低有效 |

| 输入 | DEPTH_BITWIDTH | pword | DDS相位字 |

| 输入 | DEPTH_BITWIDTH | fword | DDS频率字 |

| 输入 | DATA_BITWIDTH | cos | 余弦函数输出 |

| 输入 | DATA_BITWIDTH | sin | 正弦函数输出(比cos输出超前∠90°) |

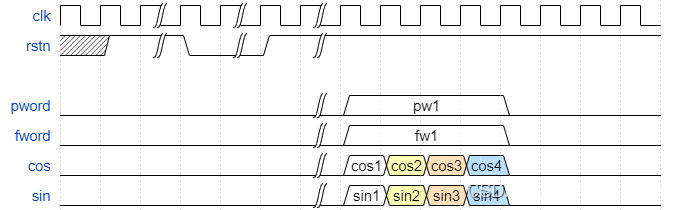

信号时序

频率字fword就是cos发生器相位在一个时钟周期递增的幅度,相位字pword就是每一个时钟周期cos发生器相位的偏移幅度。

设计原理

很简单的令cos函数发生器相位递增就可以了,如下:

// trigonometric_function/dds/dds.v

module dds #(

parameter DEPTH_BITWIDTH = 8,

parameter DATA_BITWIDTH = 8

) (

input clk,

input rstn,

input [DEPTH_BITWIDTH-1:0] pword,

input [DEPTH_BITWIDTH-1:0] fword,

output [DATA_BITWIDTH-1:0] cos,

output [DATA_BITWIDTH-1:0] sin

);

reg [DEPTH_BITWIDTH-1:0] cosf_cos_pword;

cos_function_x1 #(

.DEPTH_BITWIDTH(DEPTH_BITWIDTH),

.DATA_BITWIDTH (DATA_BITWIDTH)

) cos_function_inst_cos (

.clk (clk),

.rstn(rstn),

.pword(cosf_cos_pword + pword),

.cos (cos)

);

wire [DEPTH_BITWIDTH-1:0] cosf_sin_pword = cosf_cos_pword + 2 ** (DEPTH_BITWIDTH - 2);

cos_function_x1 #(

.DEPTH_BITWIDTH(DEPTH_BITWIDTH),

.DATA_BITWIDTH (DATA_BITWIDTH)

) cos_function_inst_sin (

.clk (clk),

.rstn(rstn),

.pword(cosf_sin_pword + pword),

.cos (sin)

);

always @(posedge clk) begin

if (!rstn) begin

cosf_cos_pword <= {DEPTH_BITWIDTH{1'b0}};

end else begin

cosf_cos_pword <= cosf_cos_pword + fword;

end

end

endmodule //dds

补充说明

一般IDE都会有DDS的软IP(紫光同创除外,此处着重提醒),用IDE自带的那个软IP肯定比自己写的好用,这个DDS其实演示意义大于实际意义。

611

611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?