PCIE基本原理简单概述

项目简述

PCIE技术在FPGA中的应用已经非常普遍,也是同学们学习的一个难点。我们会在本篇博客中讲解PCIE的理论知识,供大家了解PCIE。在下一篇博客中讲解PCIE在VIVADO中的应用,这里使用简单的方式,即XDMA。或许直接使用XDMA便可以不用了解PCIE的基础知识,但是为了知识的完整性,我们还是先在这篇博客中简要介绍PCIE。

PCIE简介

PCI Express 是用来互联计算机和外围设备的高速接口总线,是一种能够应用于移动设备,台式电脑,工作站,服务器,嵌入式计算机和通信平台等。

PCIe的两个设备之间可以实现点对点的通信串行通信,如果是多台设备需要通过交换器(Switch)进行互联,这样一个系统可以连接多个设备。

PCIe总线作为处理器系统的局部总线,其作用与PCI总线类似,主要目的是为了连接处理器系统中的外部设备,当然PCIe总线也可以连接其他处理器系统。在不同的处理器系统中, PCIe体系结构的实现方法略有不同。但是在大多数处理器系统中,都使用了RC、 Switch和PCIe-to-PCI桥这些基本模块连接PCIe和PCI设备。在PCIe总线中,基于PCIe总线的设备,也被称为EP(Endpoint)。

计算机通信平台中 , PCI Express体系结构代表作高性能的外围组件互联方法

1、 由PCI 和PCI-X 体系结构演变而来architectures

2、 PCI Express 以一种串行的点对点的方式互联两个设备

3、 信息传输基于数据包协议实现

4、 PCI Express 互联中可实现单通道或多通道的数据传输

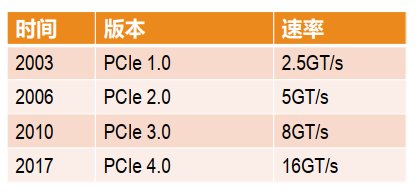

5、 PCI Express 协议目前已经发布4个版本

PCIE的特性如下:

1、点对点传输

2、 串行总线意味着使用更少的引脚

3、 通道数可选择: x1, x2, x4, x8, x12, x16, x32

4、 全双工通信

5、 2.5Gbps / 5.0Gbps

6、 基于数据包的传输协议

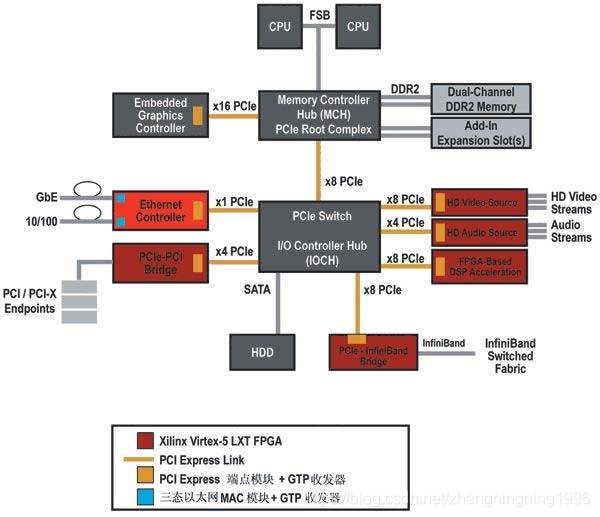

计算机体系结构中PCIe的应用架构如下:

从上面我们可以看出PCIE应用架构主要包括四部分:

1、FSB总线CPU交互总线:FSB总线(Front Side Bus)是CPU和DDR内存交互的总线

2、Root Complex:RC (Root complex)是PCIe结构体系中的一个重要的结构部件, RC的提出跟X86系统架构密切相关,实际上只有在x86架构中才有标准的RC规范定义,而在其他系统中并不存在标准定义的RC的全部功能。例如X86的架构中包含DDR控制器和FSB to PCIe的桥, 而ZynqSoc芯片架构中包含AXI to PCIe的桥和DDR控制器,PowerPc只包含一个PCIe总线控制器。这里需要注意Root complex包括root port。

3、PCIe Switch:Switch PCIe链路通过Switch进行链路扩展

4、PCIe End point:即常见的PCIE终端设备,FPGA最常用的也是End point。

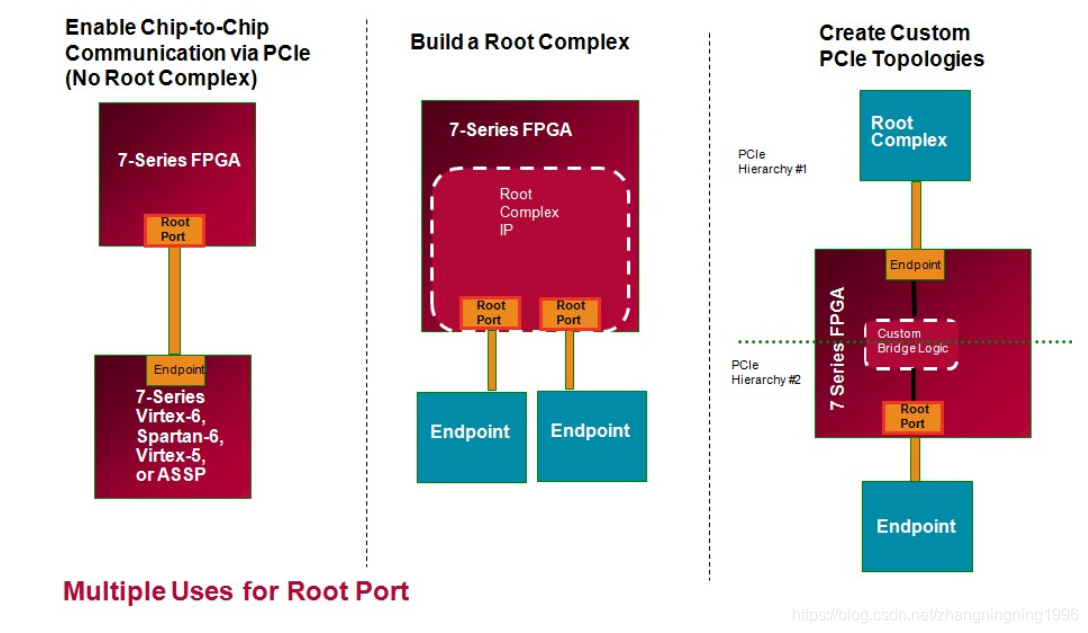

FPGA在PCIE中可以成为Root Complex、Switch和 End point:

PCIe总线层次结构主要包括三层主要是事务层、数据链路层、物理层。

1、事务层:PCIe总线层次结构的最高层,该层次将接收PCIe设备核心层的数据请求,并将其转换为PCIe总线事务, PCIe总线使用的这些总线事务在TLP头中定义。PCIe总线使用的数据报文首先在事务层中形成, 这个数据报文也被称之为事务层数据报

文,即TLP。(解释:主要意思也就是事务层将数据封装成TLP包发给下层使用)

2、数据连路层:TLP在经过数据链路层时被加上Sequence Number前缀和CRC后缀,然后发向物理层。

3、物理层:PCIe的电气特性、电路等。在PCIe链路可以正常工作之前,需要对PCIe链路进行链路训练,在这个过程中,就会用。

LTSSM状态机。 LTSSM全称是Link Training and Status State Machine。这个状态机在PCIe总线的物理层之中。状态转移图如下:

Detect状态是PCIe链路训练的开端。此外, Detect&#

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

915

915

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?